Process for producing semiconductor article using graded epitaxial growth

a technology of epitaxial growth and semiconductors, applied in semiconductor devices, chemistry apparatus and processes, single crystal growth, etc., can solve the problems of limiting the maximum ge composition to a low value, complicating or destroying the silicon layer may also complicate or undermine the performance of devices built, so as to achieve simplified and improved process, high quality material

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

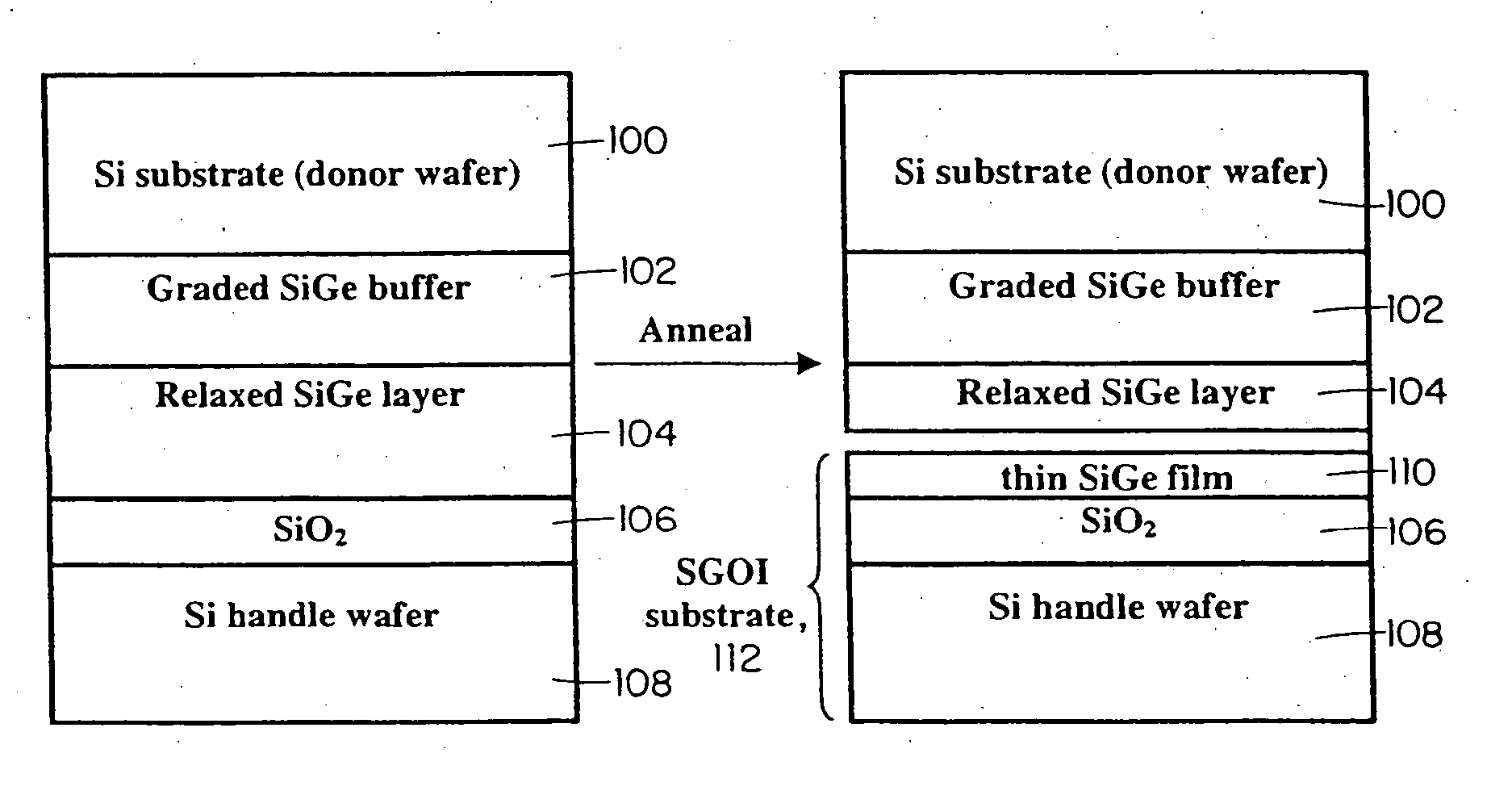

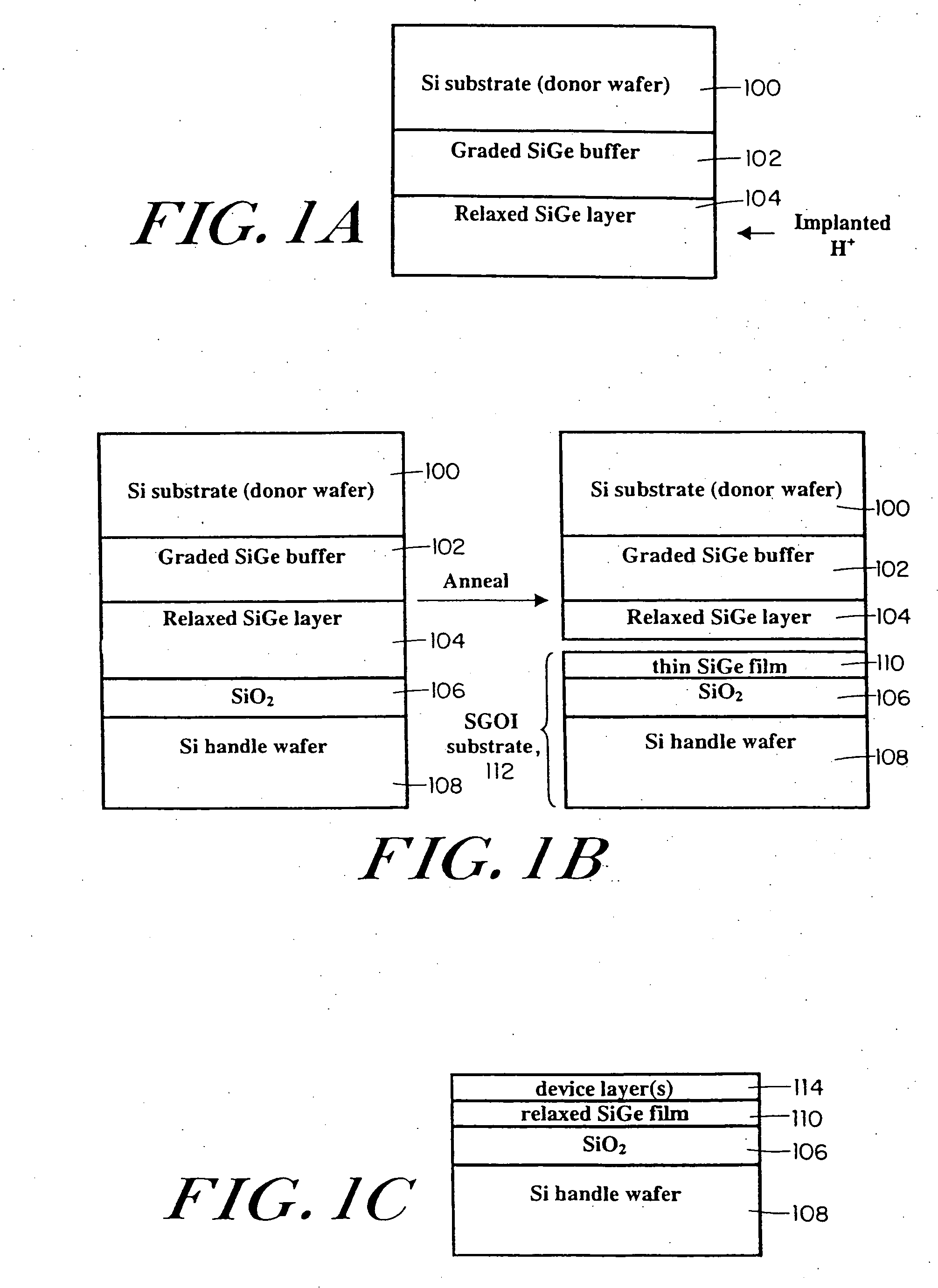

[0019] An example of a process in which SGOI is created by layer transfer is described. The experiment was performed in two stages. In the first stage, heteroepitaxial SiGe layers are formed by a graded epitaxial growth technology. Starting with a 4-inch Si (100) donor wafer 100, a linearly stepwise compositionally graded Si1-xGex buffer 102 is deposited with CVD, by increasing Ge concentration from zero to 25%. Then a 2.5 μm relaxed Si0.75Ge0.25 cap layer 104 is deposited with the final Ge composition, as shown in FIG. 1A.

[0020] The relaxed SiGe cap layer has high quality with very low dislocation defect density (less than 1E6 / cm2), as the graded buffer accommodates the lattice mismatch between Si and relaxed SiGe. A thin layer of this high quality SiGe will be transferred into the final SGOI structure. The surface of the as-grown relaxed SiGe layer shows a high roughness around 11 nm to 15 nm due to the underlying strain fields generated by misfit dislocations at the graded layer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More