Method of surface pretreatment before selective epitaxial growth

a technology of selective epitaxial growth and surface pretreatment, which is applied in the direction of crystal growth process, chemically reactive gas, chemistry apparatus and processes, etc., can solve the problems of rough surface of epitaxial layer, serious undercutting of first sidewall spacer, and junction leakage, and achieve good quality and effective removal of native oxide

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

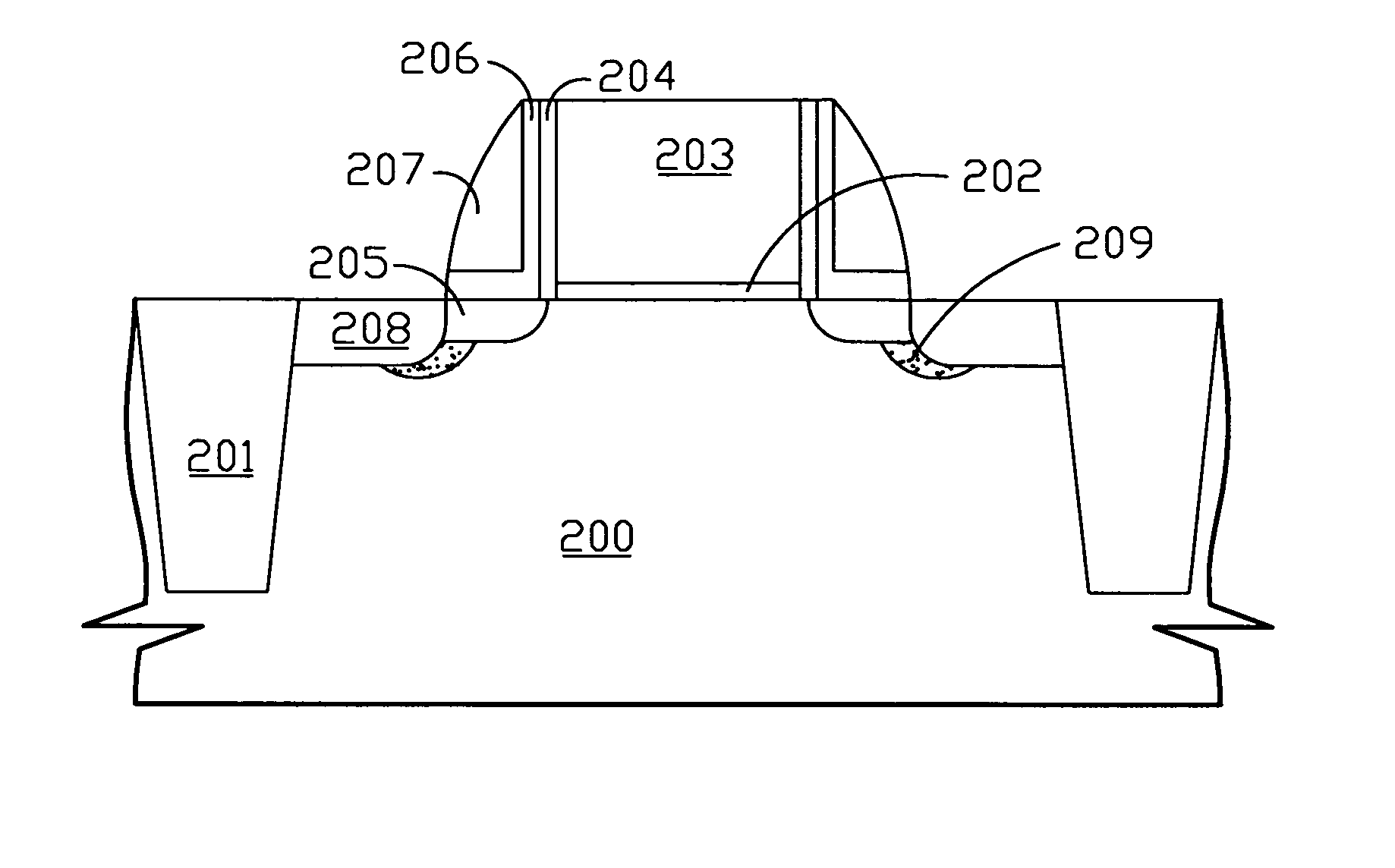

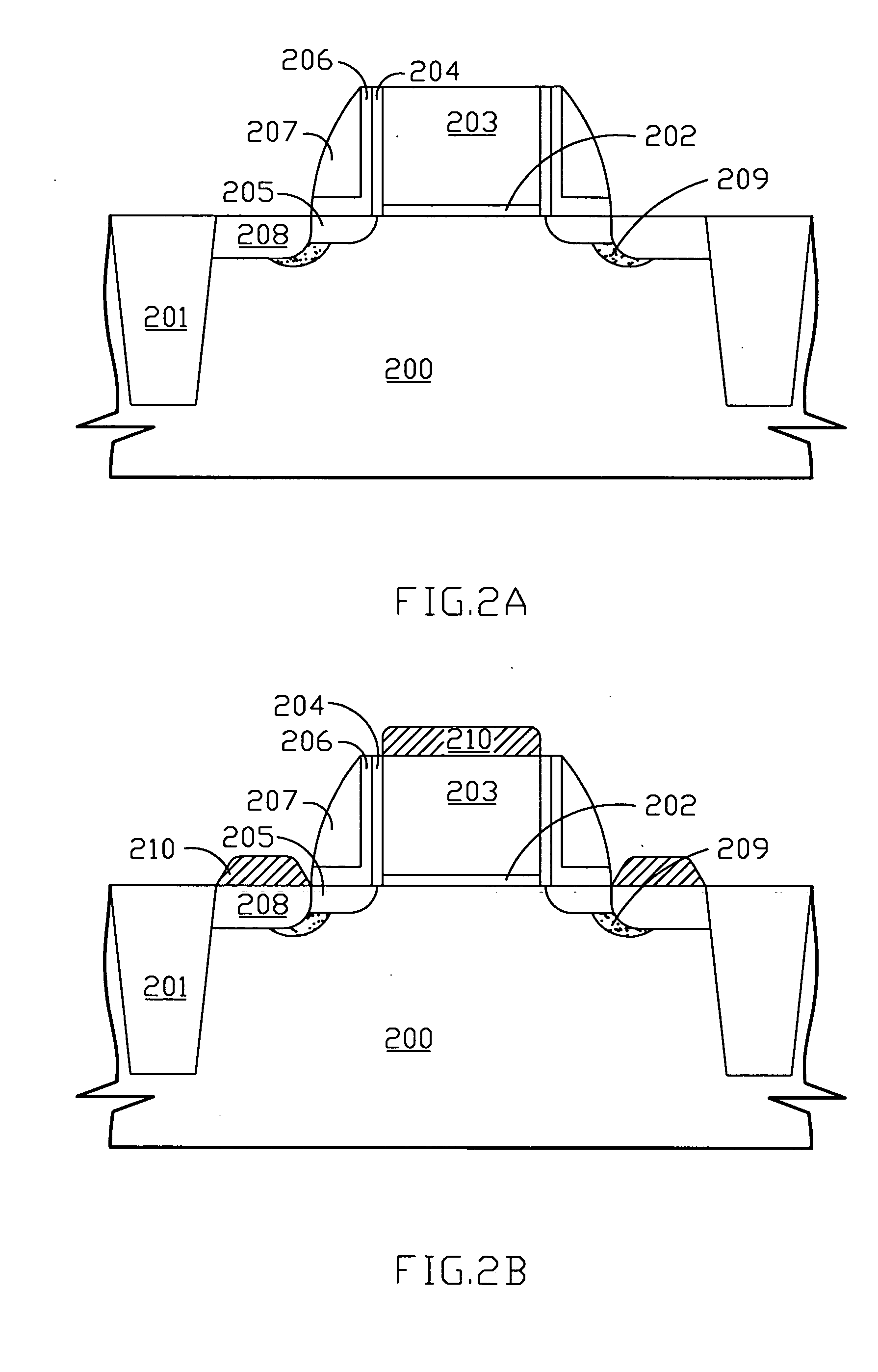

[0016] The present invention will be described in detail with reference to the accompanying drawings. The present invention provides a method of surface pretreatment before selective epitaxial growth process, which can resolve the undercut issue and surface roughness of the epitaxial layer. Referring to FIG.2A, a semiconductor substrate 200, such as a silicon substrate, with a first conductive type, is firstly provided. The first conductive type is either of N type and P type. A plurality of shallow trench isolations 201 is formed in the semiconductor substrate 200. Other isolation region, for example, field oxide, can be substituted for the shallow trench isolation 201. Then, a gate oxide 202 and a polysilicon gate electrode 203 are sequentially formed between each pair of the shallow trench isolations 201 on the semiconductor substrate 200. Next, forming an offset spacer of silicon dioxide 204 around the gate oxide 202 and the polysilicon gate electrode 203. Then, forming a lightl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More