Trenched MOSFETS with part of the device formed on a (110) crystal plane

a crystal plane and mosfet technology, applied in the direction of semiconductor devices, basic electric elements, electrical appliances, etc., can solve the problems of affecting the practical implementation of such configurations, affecting the mobility of channels, and difficult to achieve high interface state density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

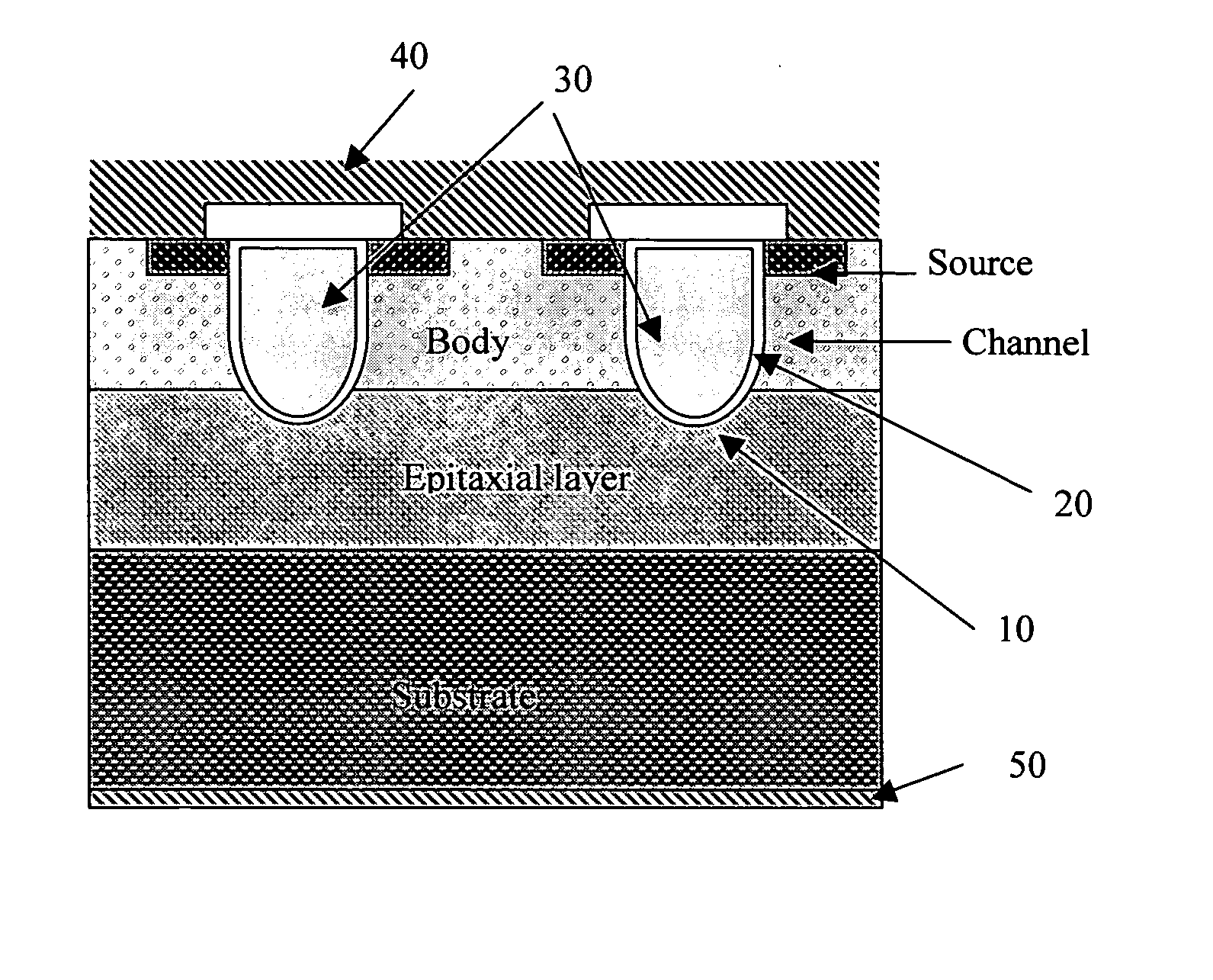

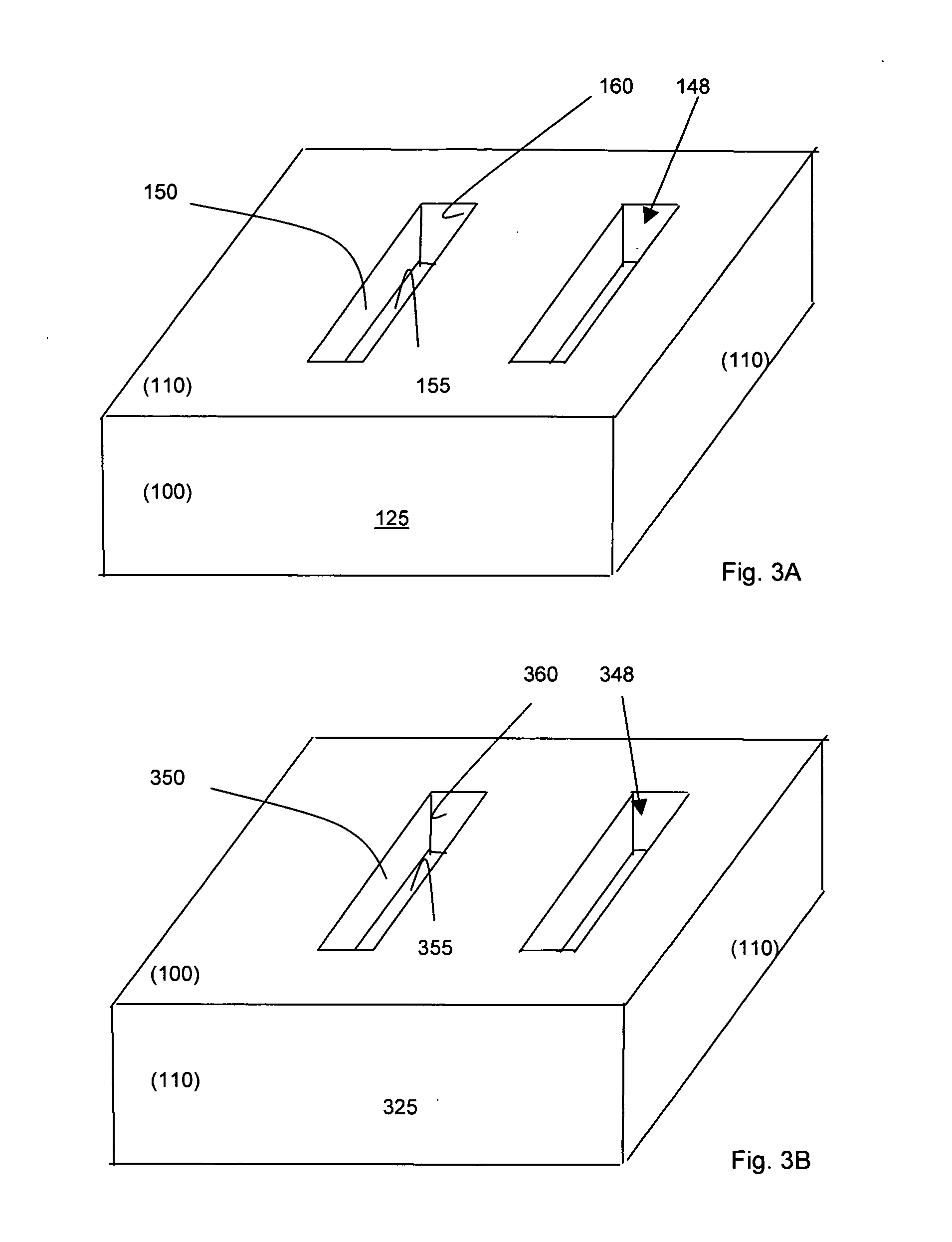

[0026] For P-channel implementations, FIGS. 3A and 3B show the orientations of the substrate and trench according to the current invention. In FIG. 3A, the silicon ingot 125 is grown in the (110) plane. The silicon ingot 125 provides a configuration that four sidewalls are situated with four sidewall surfaces forming a corner with a corner angle of 90 degrees, thus these sidewall surfaces are perpendicular to each other. Two of these sidewalls are along a (100) crystal orientation and two are along a (110) crystal orientation. Referring to FIG. 3A, two sidewalls 150 and bottom 155 of the trench 148 are formed along a (110) crystal orientation while the termination end surface 160 of the trench 148 is formed along a (100) crystal orientation. In FIG. 3B, the wafer 325 is formed by rotating a normal (100) wafer as shown in FIG. 2 by 45° thus forming two interface planes on a (110) plane while the top and bottom planes are still on the (100) plane. As can be observed from FIG. 3B, when...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More