Manufacture method for semiconductor device having field oxide film

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

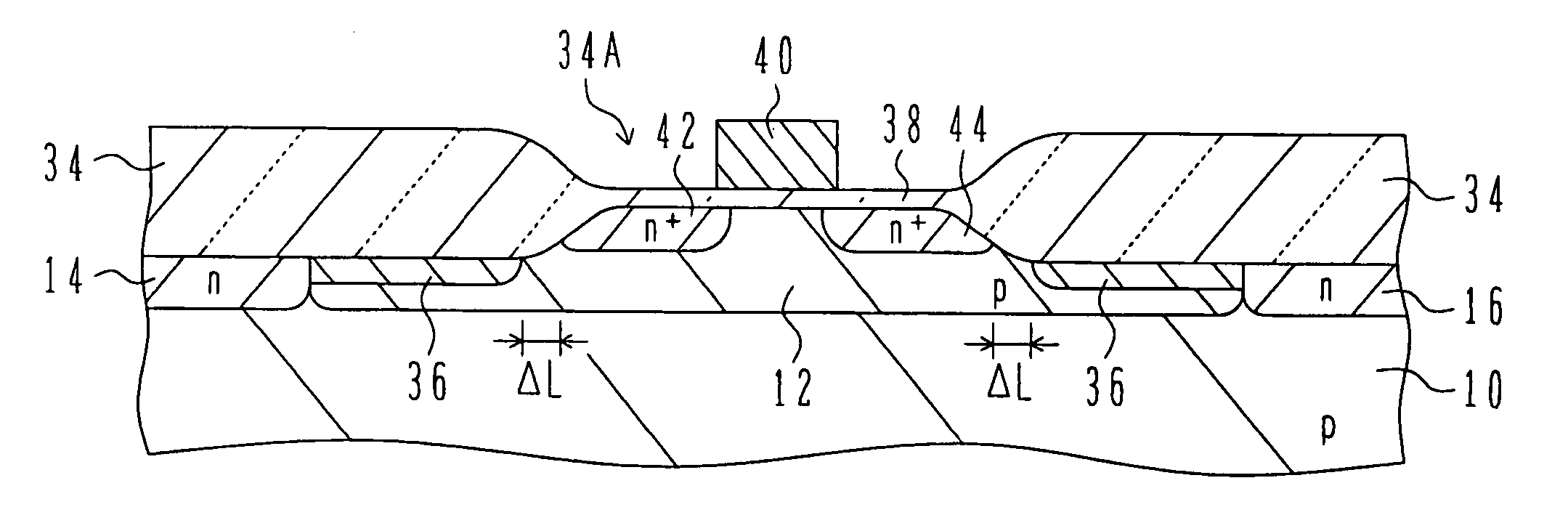

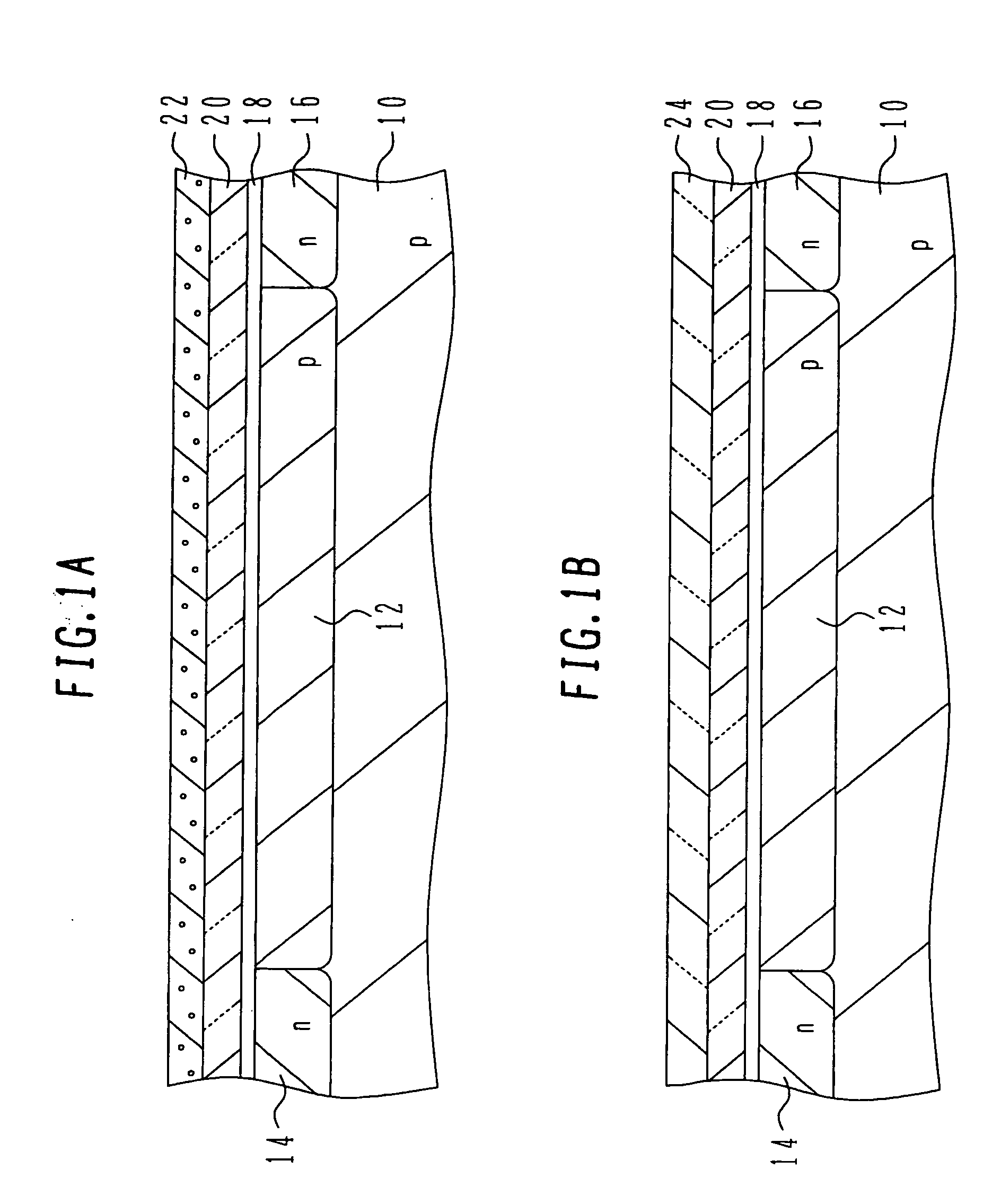

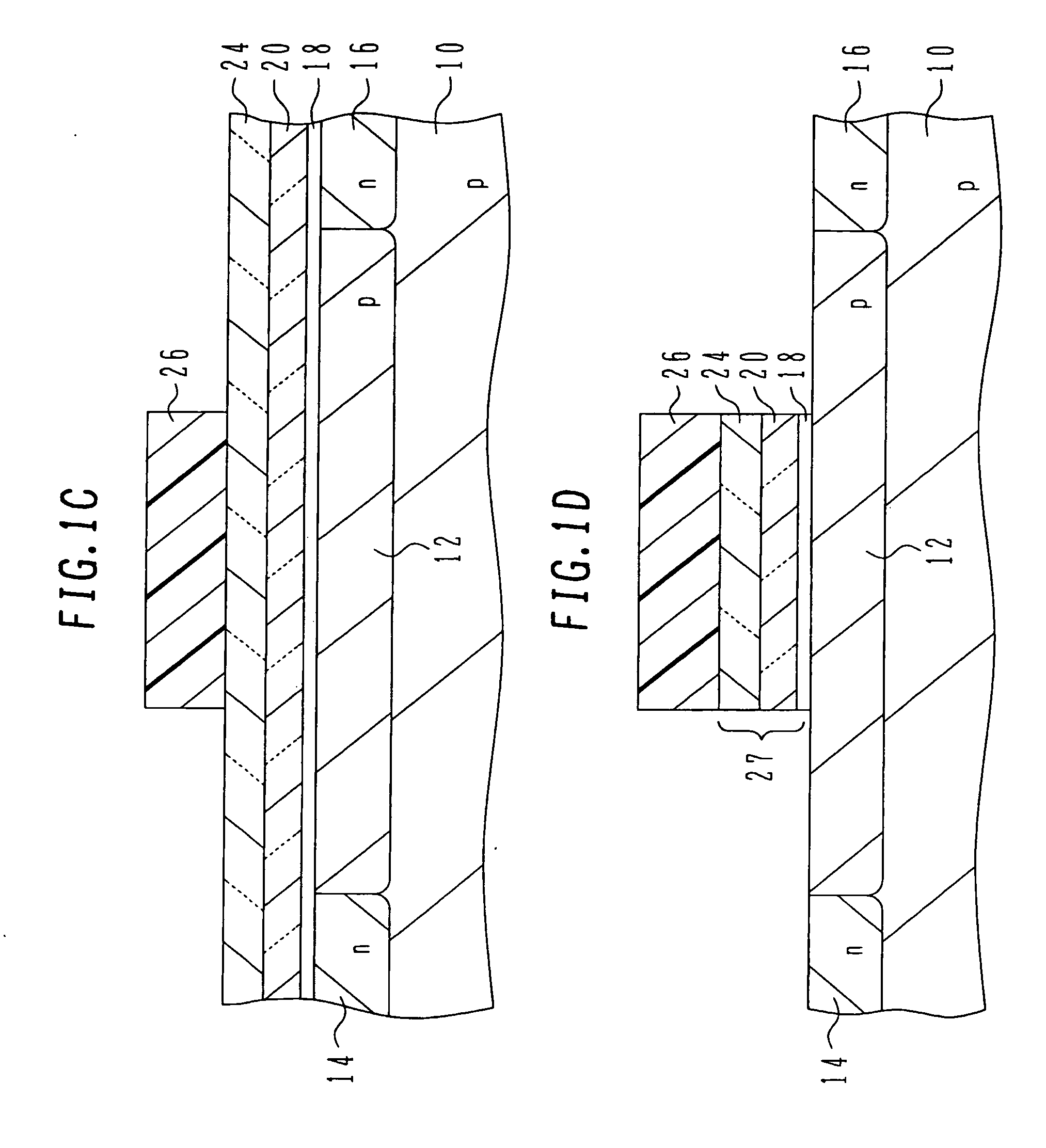

[0069]FIGS. 1A to 1J illustrate a manufacture method for a metal oxide semiconductor (MOS) type integrated circuit (IC) using a field oxide film forming method according to the present invention. Processes corresponding to FIGS. 1A to 1J will be described sequentially.

[0070] In a process shown in FIG. 1A, a p-type well region 12 and n-type well regions 14 and 16 are formed side by side on a principal surface of a p-type silicon substrate 10 by a well-known method. The n-type well regions 14 and 16 may be formed as one well region surrounding the p-type well region 12. After the well regions 12 to 16 are formed, a silicon oxide film (stress relaxing pad oxide film) 18 is formed on the principal surface of the substrate 10 by thermal oxidation. A thickness of the silicon oxide film 18 may be, for example, in a range from 30 nm to 40 nm. A silicon nitride film 20 is formed on the silicon oxide film 18 by CVD, and a polysilicon film 22 is formed on the silicon nitride film 20 by CVD. A ...

second embodiment

[0100]FIGS. 3A to 3H illustrate a manufacture method for an n-channel MOS type transistor of a complementary metal oxide semiconductor (CMOS) type IC according to the present invention. Processes corresponding to FIGS. 3A to 3H will be described sequentially.

[0101] In a process shown in FIG. 3A, a p-type well region 112 and n-type well regions 114 and 116 are formed side by side on a principal surface of a p-type silicon substrate 110 by a well-known method. The n-type well regions 114 and 116 may be formed as one well region surrounding the p-type well region 112. After the well regions 112 to 116 are formed, a silicon oxide film (stress relaxing pad oxide film) 118 is formed on the principal surface of the substrate 110 by thermal oxidation. A thickness of the silicon oxide film 118 may be, for example, in a range from 30 nm to 40 nm. A silicon nitride film 120 is formed on the silicon oxide film 118 by CVD. A thickness of the silicon nitride film 120 may be 75 nm to 150 nm (prefe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More