Mis transistor and cmos transistor

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] In the following description, details of a preferred embodiment of the present invention are set forth with reference to the accompanying drawings.

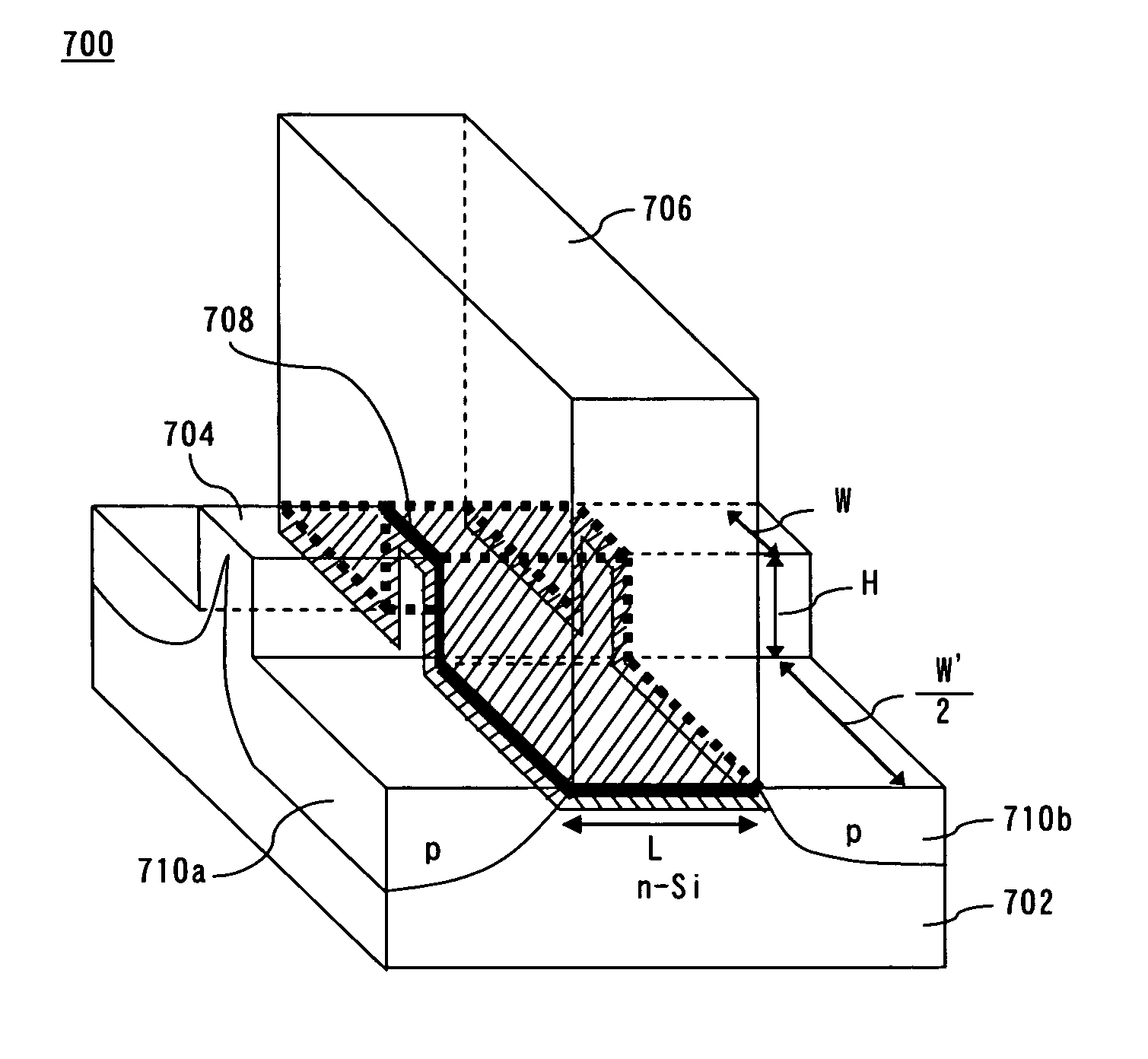

[0047] A transistor of the embodiment of the present invention has an MIS (Metal Insulator Semiconductor) configuration.

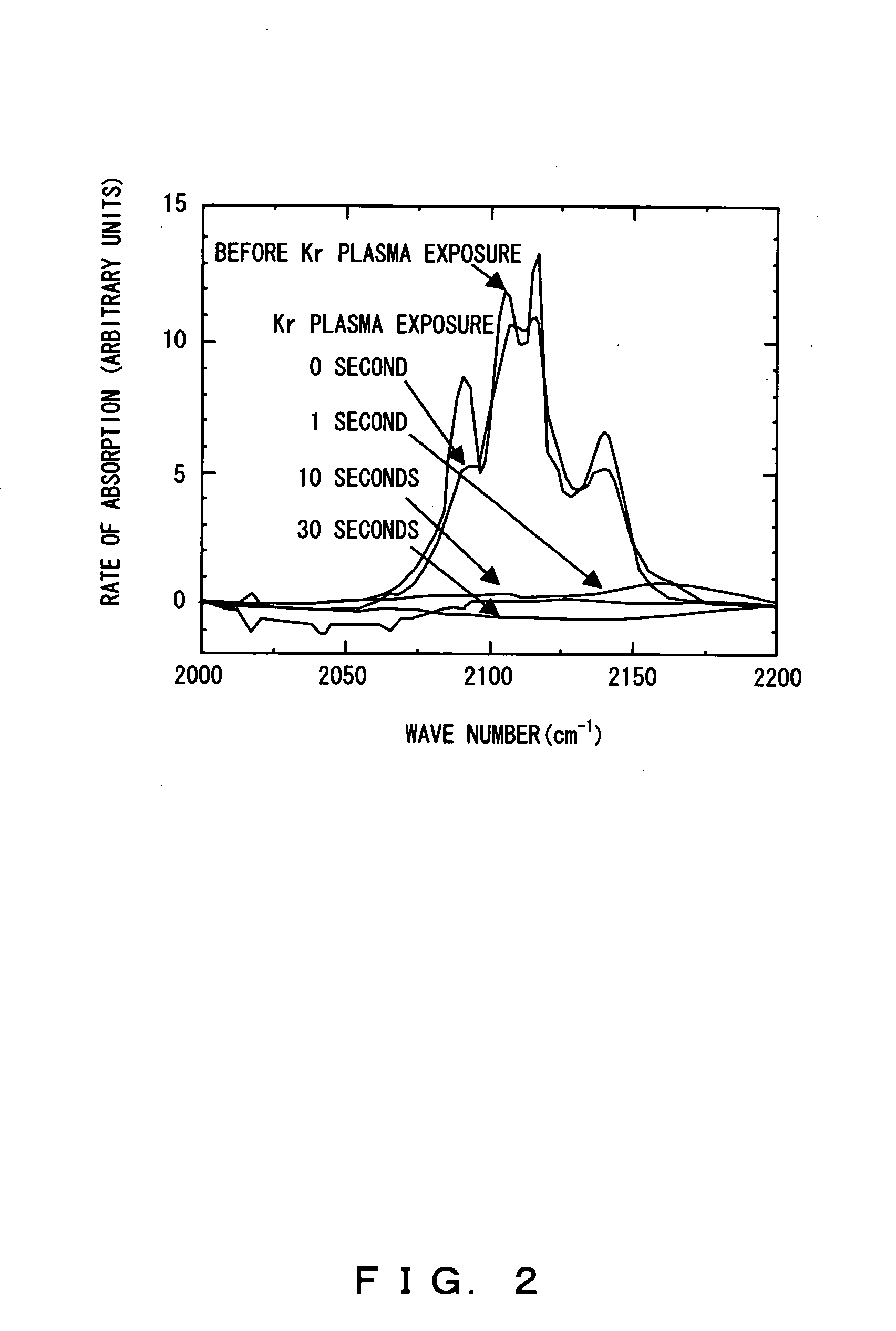

[0048] A gate insulator of the MIS transistor is formed based on a gate insulator thin film formation technique, in which a thin gate insulator of an MIS transistor is formed with high performance electrical characteristics, as disclosed in Japanese laid-open unexamined patent publication No. 2002-261091.

[0049] An explanation of the gate insulator thin film formation technique of the MIS transistor is provided first.

[0050] Regarding the type of gate insulator of the MIS transistor there are a variety such as an oxide film, a nitride film and an oxynitride film described in Japanese laid-open unexamined patent publication No. 2002-261091, and also many varieties for semiconductor substrates with different cryst...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More