Metal oxide semiconductor field-effect transistor (MOSFET) and method of fabricating the same

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will now be described more fully with reference to the accompanying drawings, in which exemplary embodiments of the invention are shown.

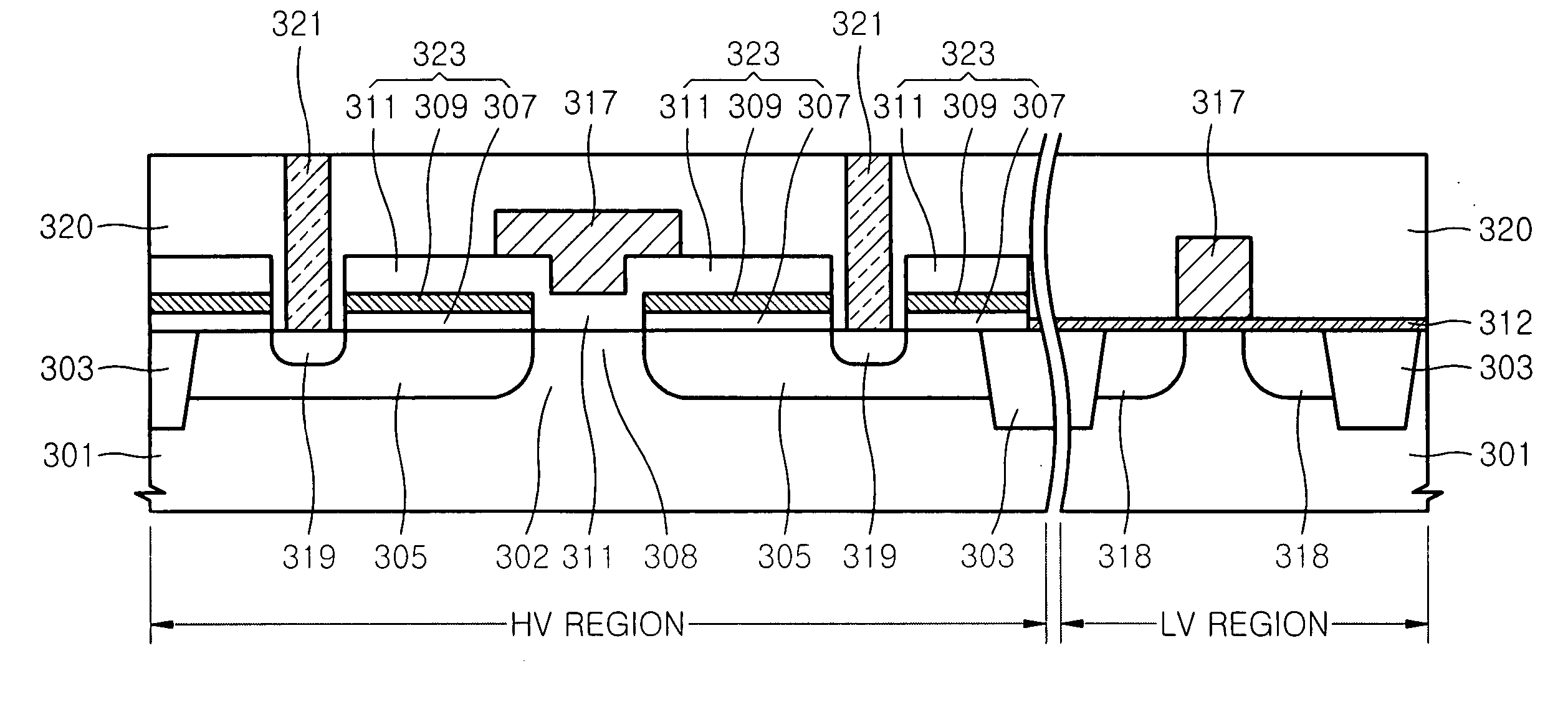

[0027]FIG. 10 shows a structure of a MOSFET according to an exemplary embodiment of the present invention, in which the left portion is a high voltage (HV) region formed with a high voltage transistor and the right portion is a low voltage (LV) region formed with a low voltage transistor. For example, in LDI-related products, a high voltage transistor for driving an LCD device is formed in the HV region, and a low voltage transistor for logic may be formed on the LV region. The exemplary embodiments of the present invention is not limited to the LDI structure, but may be applied to semiconductor devices with various types as long as a high voltage transistor is formed at least in the HV region.

[0028] Referring to FIG. 10, in the HV region, a trench-shaped device isolating region 303 is disposed in a predetermined porti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More