Semiconductor device and method of manufacturing the same

a semiconductor and channel technology, applied in the direction of semiconductor devices, electrical devices, transistors, etc., can solve the problems of high barrier to solving, insufficient utilization of the merit of schottky source-drain which can inject high-speed carriers into channels, and difficulty in improving device performance relying only on micro-patterning, etc., to achieve effective suppression of short channel effect and junction leakage, improve performance, and increase the injection rate of carriers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

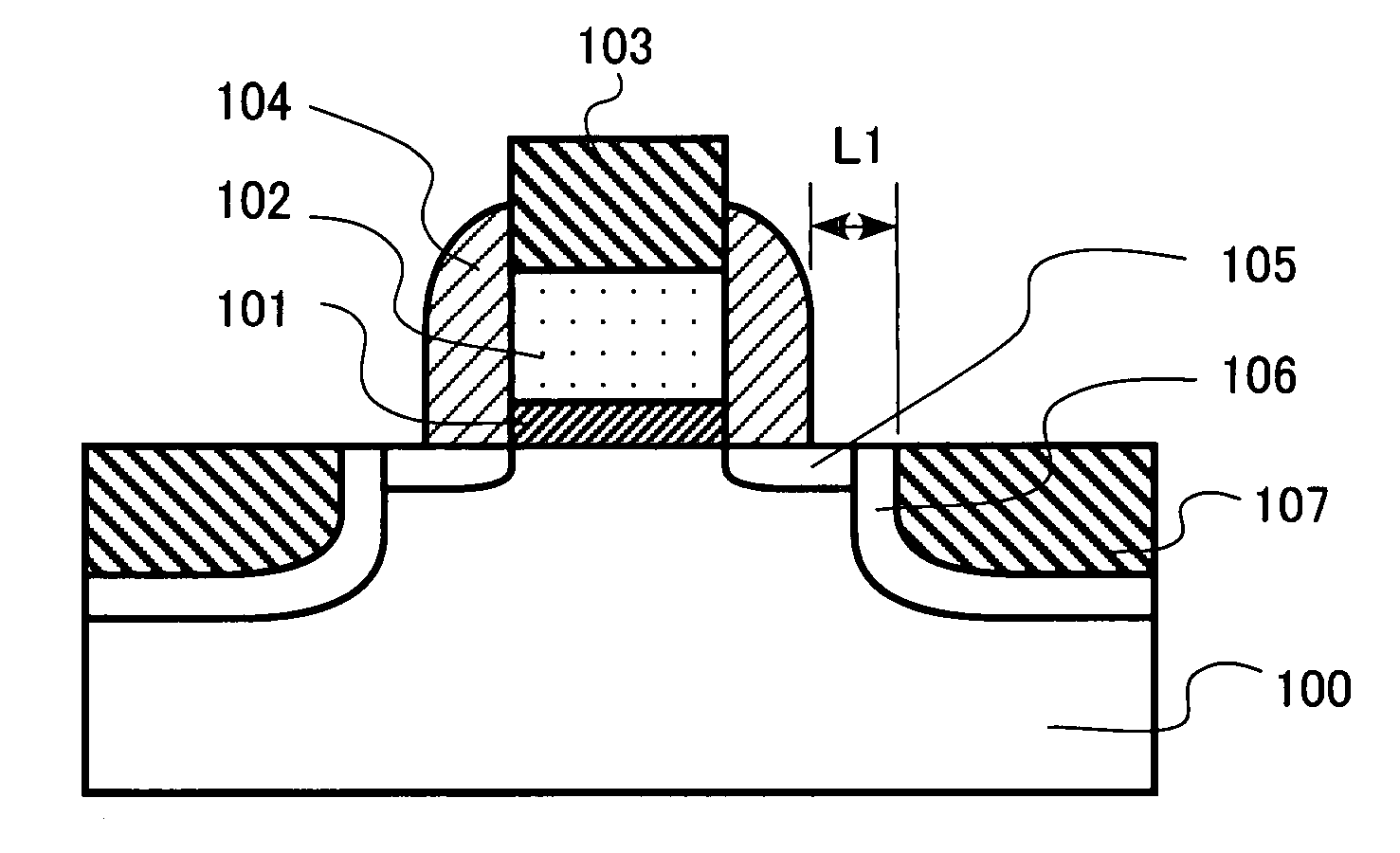

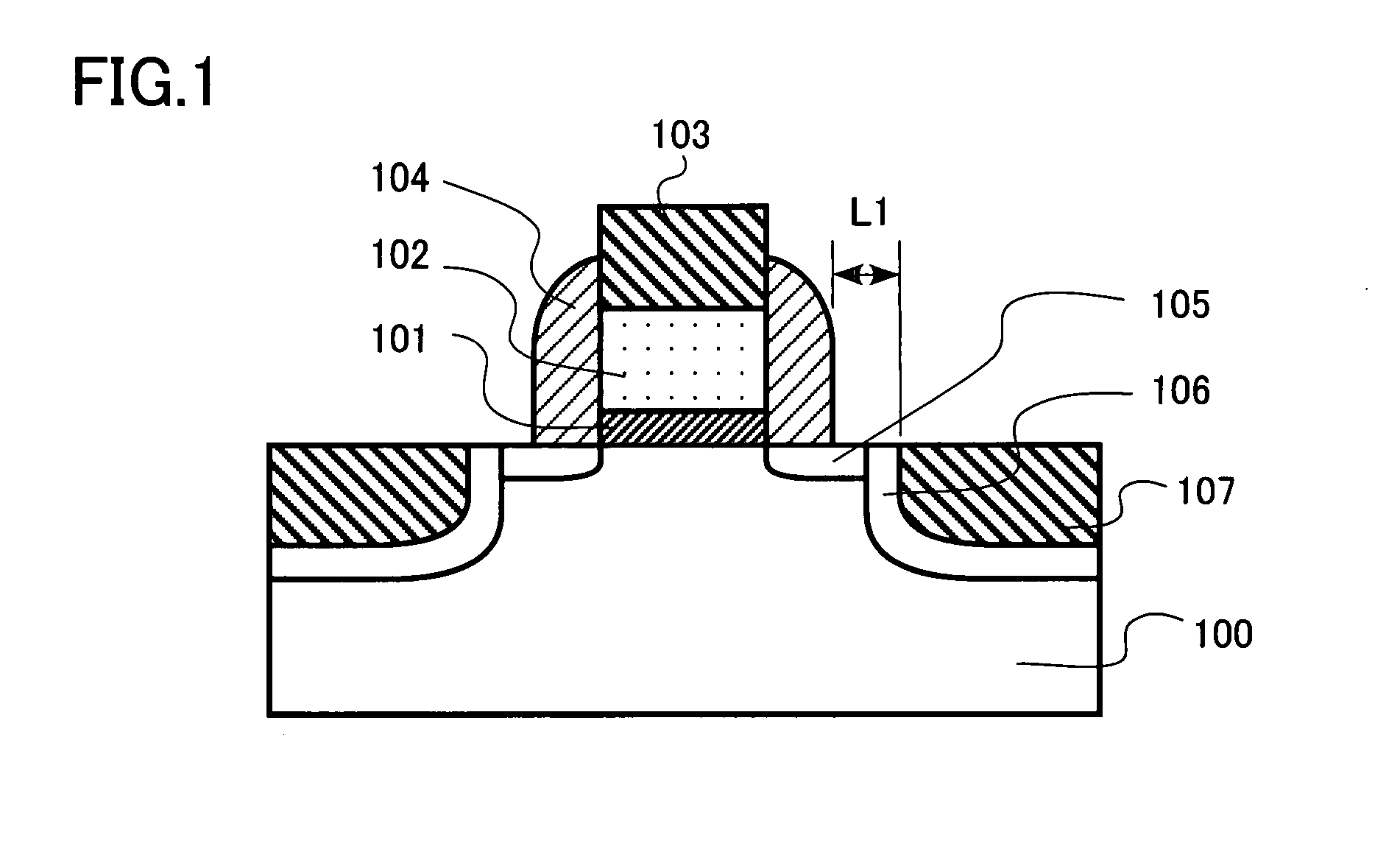

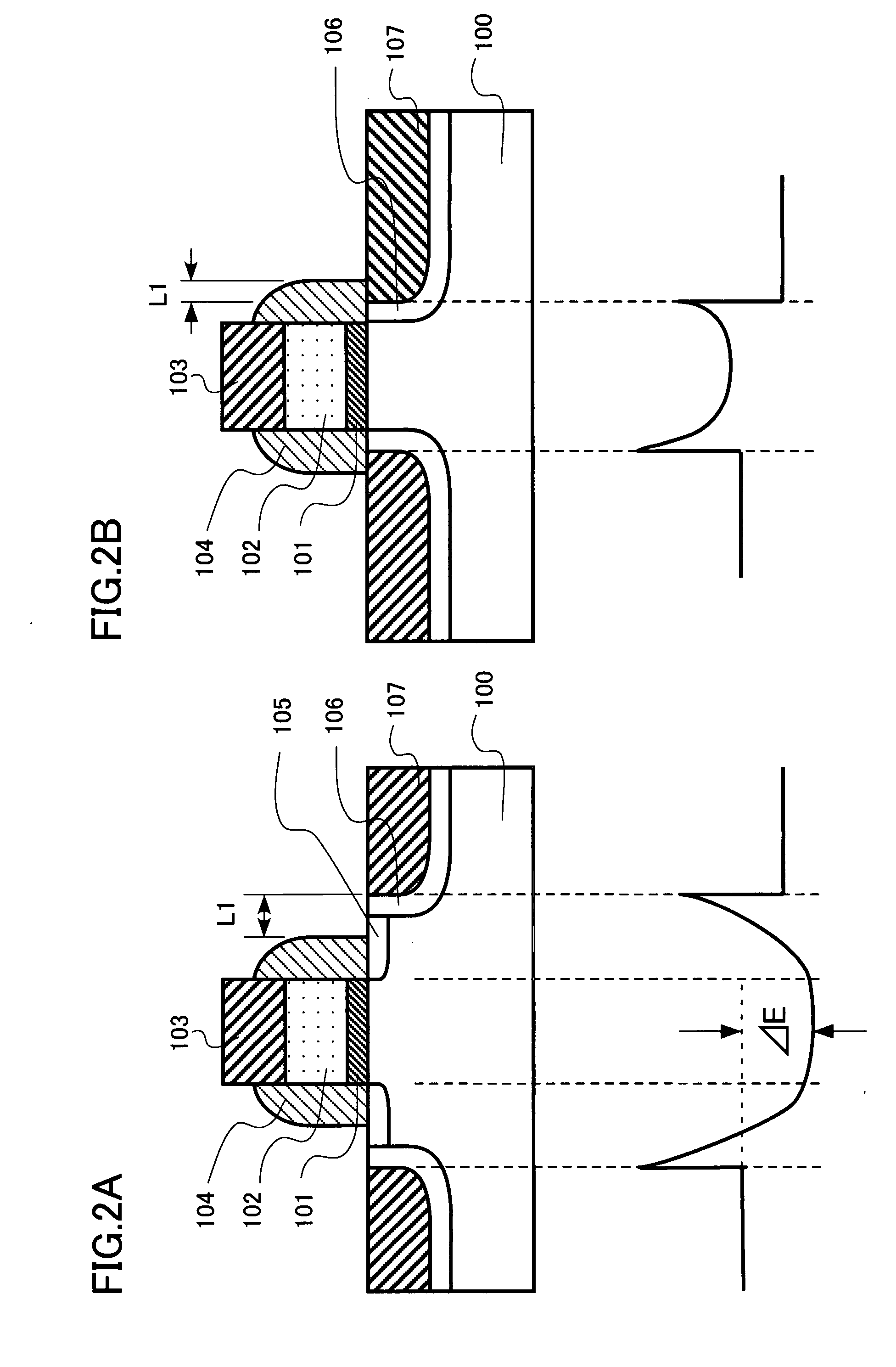

[0026]FIG. 1 is a sectional view showing an device structure of a MIS field effect transistor according to a first embodiment.

[0027] A polysilicon gate electrode 102 is formed on a p-type silicon substrate (first semiconductor region) 100 a gate insulating film 101 in between. A gate silicide 103 is formed on the polysilicon gate electrode 102. In this case, the gate electrode 102 is made of polysilicon. However, a metal gate structure in which the polysilicon gate electrode 102 and the gate silicide 103 are replaced by a single metal layer may be employed.

[0028] On both the side surfaces of the gate electrodes 102 and 103, a gate side wall insulating film 104 constituted by a silicon nitride film is formed. Source and drain regions are formed in the silicon substrate 100 to interpose a channel region under the polysilicon gate electrode 102. The source and drain regions are constituted by, an n-type extension diffusion layer (second semiconductor region) 105 using, for example, A...

second embodiment

[0072]FIG. 24 is a cross-sectional view showing an device structure of a MIS field effect transistor according to a second embodiment of the present invention. Since the MIS field effect transistor is the same as that in the first embodiment except that an HALO diffusion layer (fourth semiconductor region) 201 is formed, a description thereof will be omitted.

[0073] The HALO diffusion layer 201 is a p-type region the impurity type of which is the same as that of a silicon substrate 100, and has an impurity concentration higher than that of the silicon substrate 100 as a characteristic feature. The field effect transistor according to the embodiment includes the HALO diffusion layer 201 to obtain the operation and effect of the first embodiment and to achieve improvement of a roll-off characteristic.

third embodiment

[0074]FIG. 25 is a cross-sectional view showing an device structure of a MIS field effect transistor according to a third embodiment of the present invention. Since the MIS field effect transistor according to the third embodiment is the same as that of the first embodiment except that an n+-type deep diffusion layer (fifth semiconductor region) 301 is formed, a description thereof will be omitted.

[0075] The n+-type deep diffusion layer 301 is formed between an n+-type high-concentration impurity layer 106 and the silicon substrate 100, and has a thickness of, for example, about 50 nm.

[0076] The field effect transistor according to the embodiment includes the n+-type deep diffusion layer 301 to obtain the operation and effect of the first embodiment and to achieve a considerable reduction in junction leakage from the source-drain bottom portion.

[0077] Due to the presence of the n+-type high-concentration impurity layer 106, the n+-type deep diffusion layer 301 can be made shallow...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More