Leakage aware design post-processing

a post-processing and leakage detection technology, applied in the direction of originals for photomechanical treatment, instruments, optics, etc., can solve the problems of ed-opc more time-consuming and costly than conventional opc, and the inability to print perfect polygons, etc., to achieve cost-effective effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

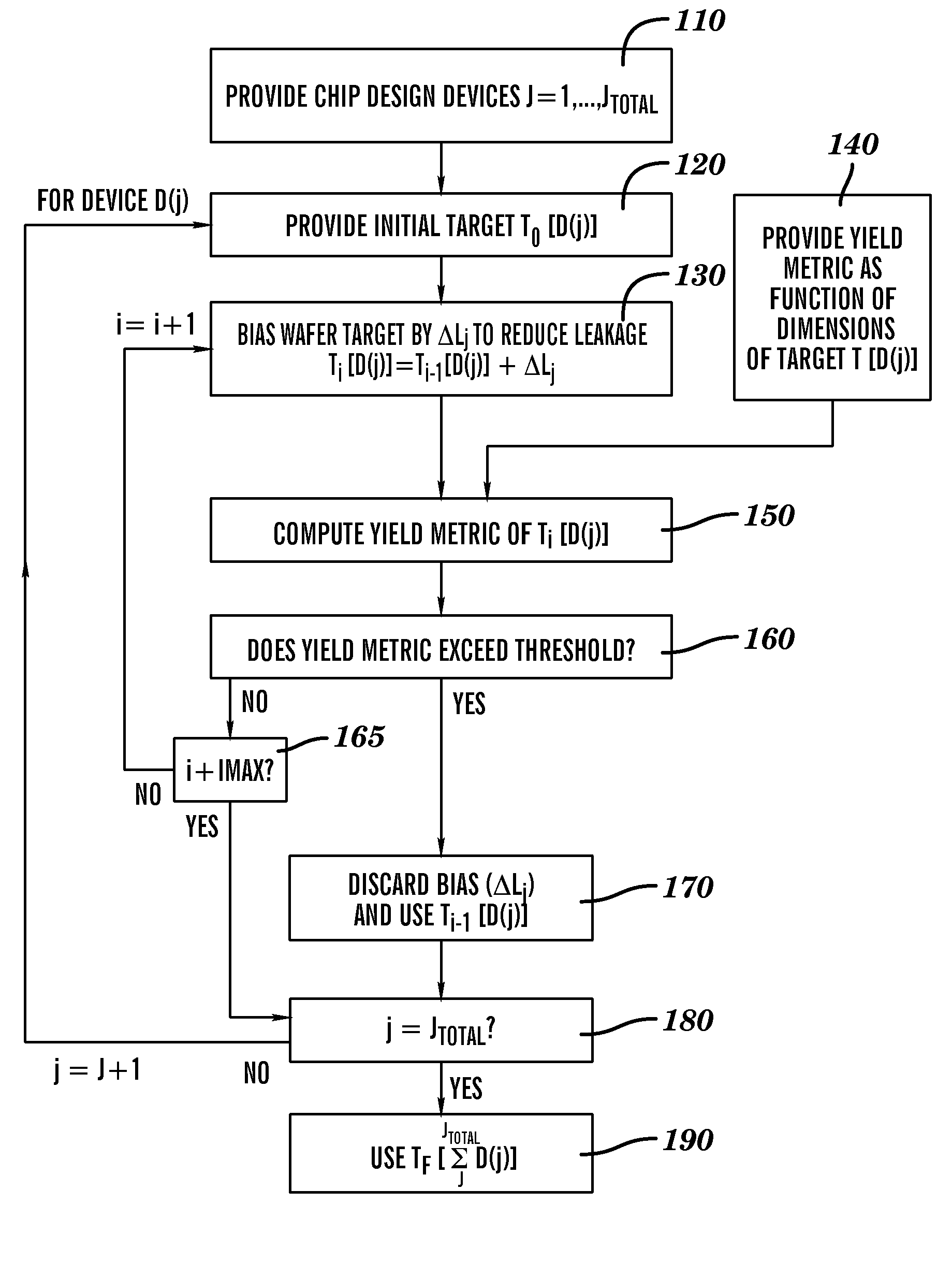

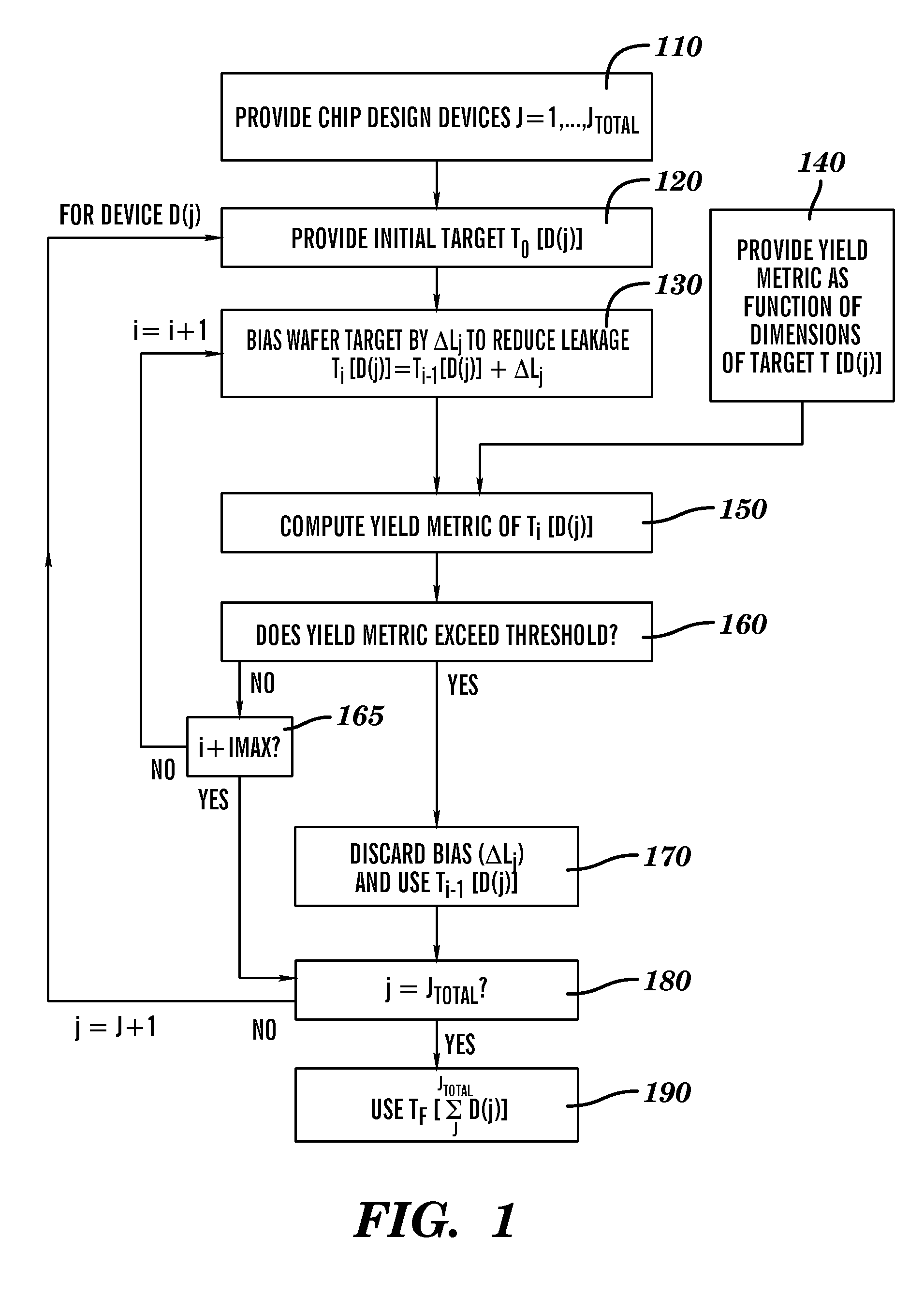

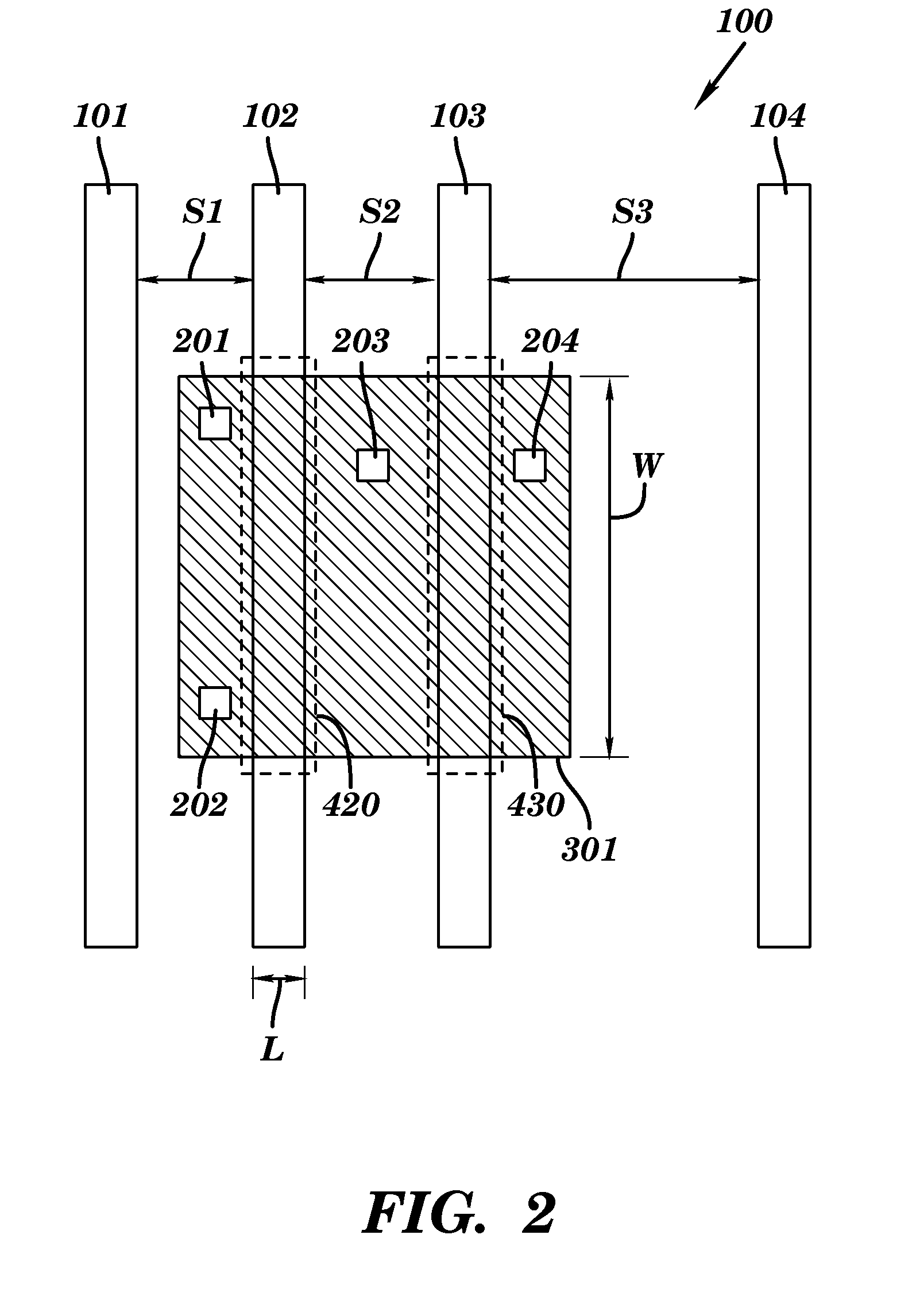

[0025]This invention presents a method for designing and optimizing a lithographic mask that accounts for lithographic process variations across the layout while meeting designers' intent for product requirements. The term “lithographic process” as used and referred to herein, includes, without limitation, any pattern transfer process, such as forming a resist image, forming implants, performing a patterned etch, etc. An integrated circuit design or chip design typically includes layouts of multiple layers of shapes to be printed. A device layer may be printed by using one or more lithographic masks. The on-wafer target is used by an OPC tool or OPC verification tool during the mask design process by ensuring or verifying that simulated image contours resulting from the mask (or masks) for printing a given layer matches the on-wafer target according to predetermined criteria. More particularly, the method, in accordance with the invention, modifies the initial design target by optim...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More