Effective Work Function Modulation by Metal Thickness and Nitrogen Ratio for a Last Approach CMOS Gate

a technology of nitrogen ratio and work function, applied in the field of effective work function modulation of metal thickness and nitrogen ratio for a last approach cmos gate, can solve the problems of difficult to achieve, significantly affect the ewf, and relatively complex process, and achieve the effect of increasing ewf, reducing ewf, and high thermal budg

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

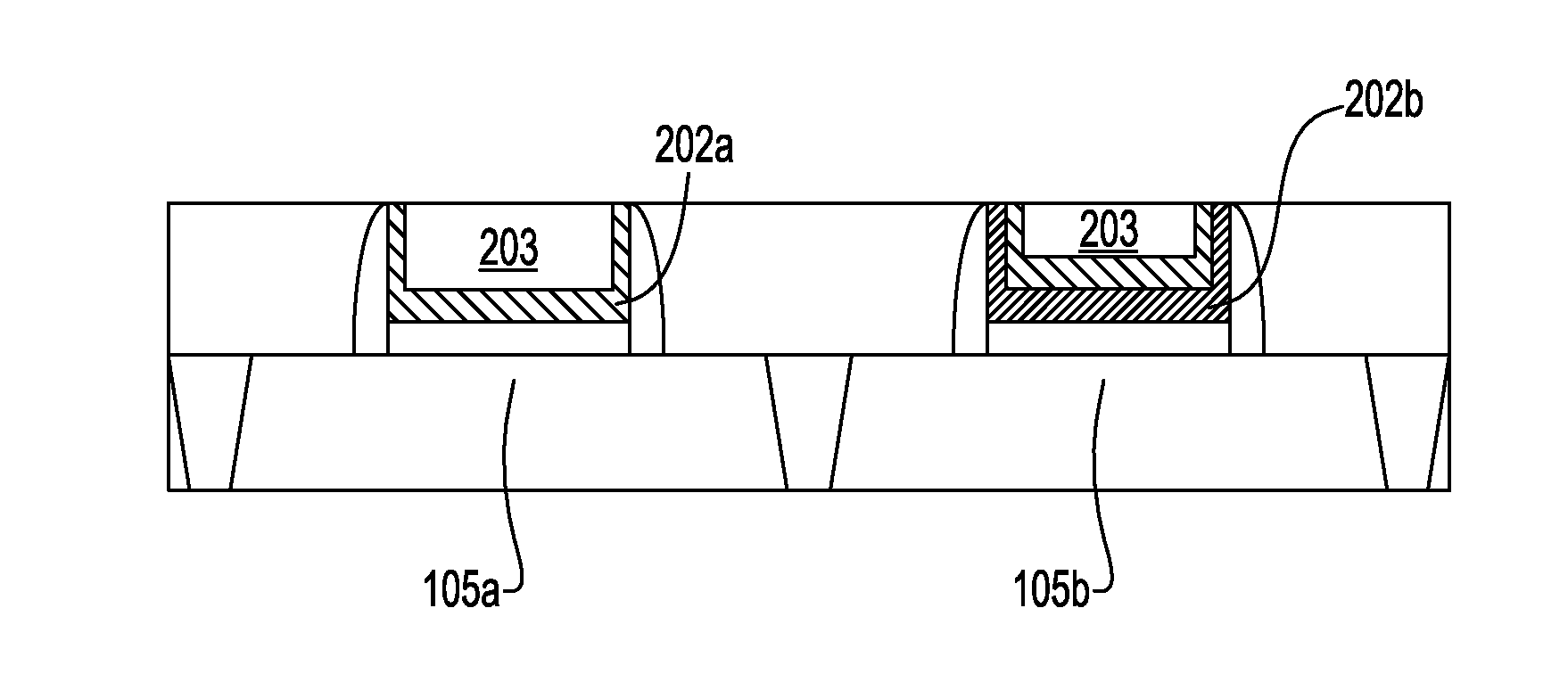

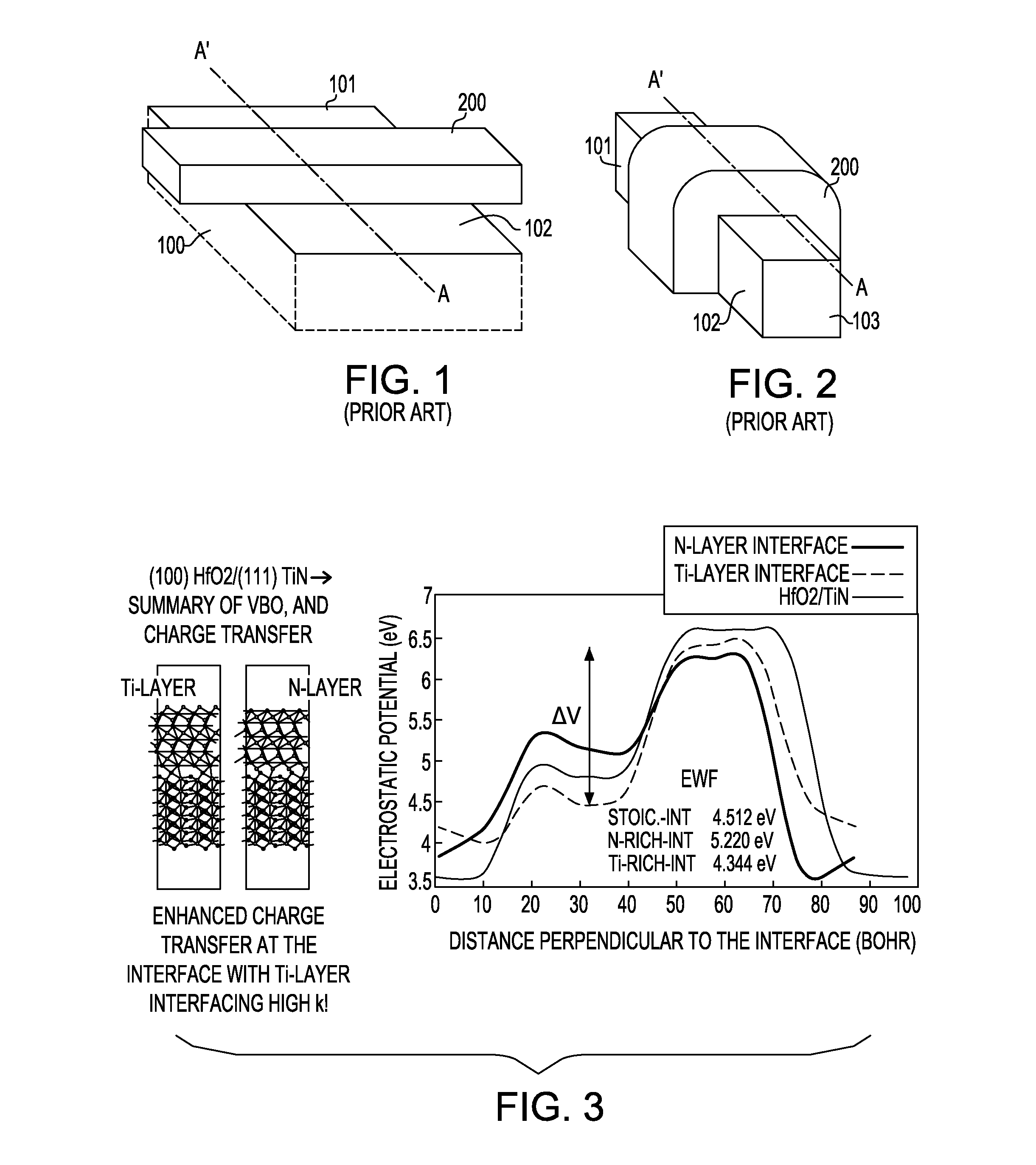

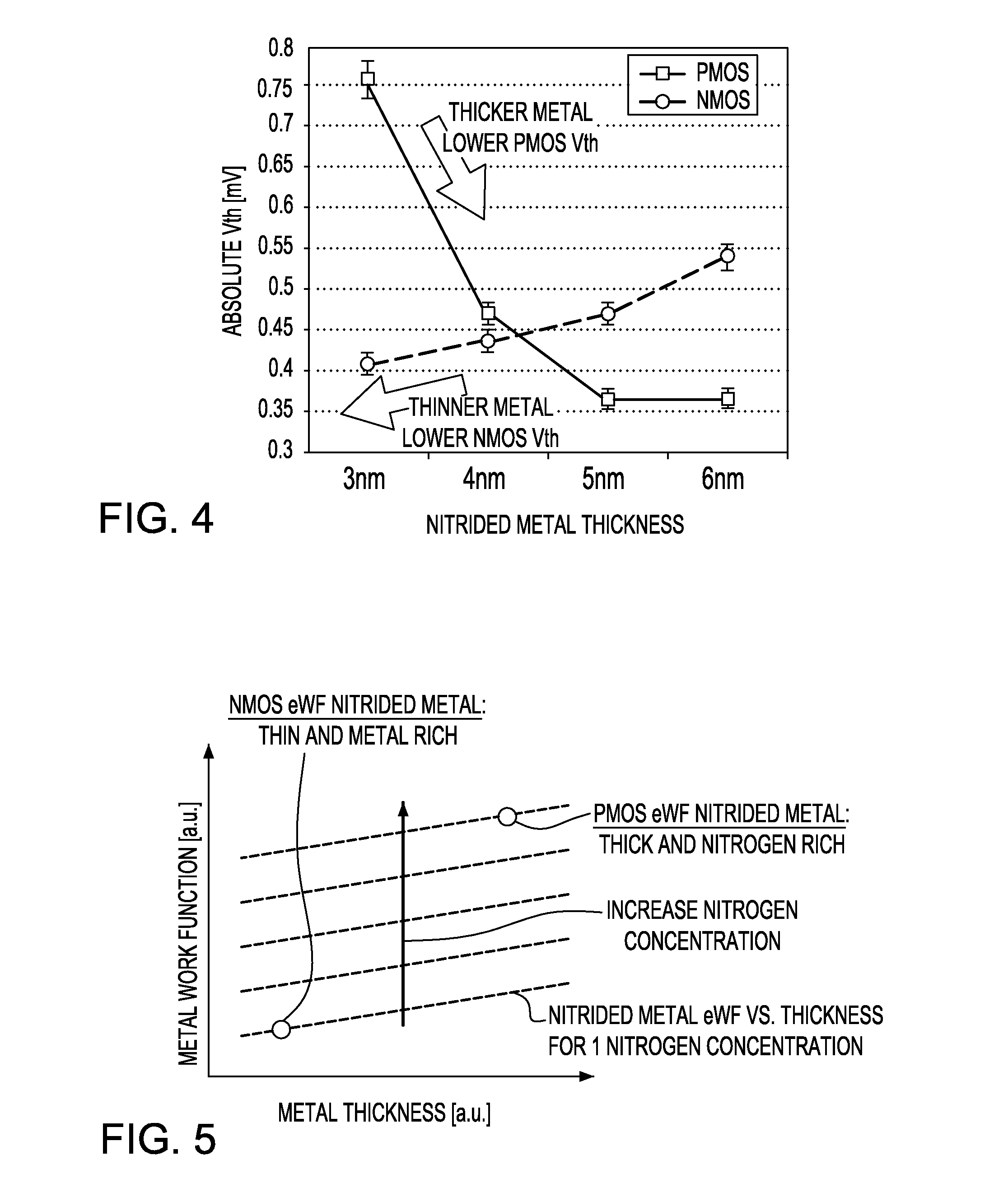

[0031]The present disclosure relates to forming a pFET device by controlling its work function (WF) employing a thick metal nitride alloy or carbon metal nitride alloy, both of which are nitrogen rich (1−X atoms of metal for X atoms of nitrogen, wherein X>0.5, e.g., two or more nitrogen atoms for each metal atom), and forming a complementary nFET device by controlling its WF employing the same metal nitride alloy or carbon metal nitride alloy, but having a thin layer of the aforementioned metal nitride alloy and which is metal-rich (1−X atoms of metal for X atoms of nitrogen where X<0.5, e.g., two or more metal atoms for each nitrogen atom).

[0032]The pFET and nFET transistors thus constructed and method of fabrication will now be described in greater detail by referring to the following description and drawings that accompany the present application. It is noted that the drawings of the present application are provided for illustrative purposes and, as such, they are not drawn to sc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More