Patents

Literature

61 results about "Dopant Activation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Dopant Activation is the process of obtaining the desired electronic contribution from impurity species in a semiconductor host. The term is often restricted to the application of thermal energy following the ion implantation of dopants. In the most common industrial example, rapid thermal processing is applied to silicon following the ion implantation of dopants such as phosphorus, arsenic and boron. Vacancies generated at elevated temperature (1200 °C) facilitate the movement of these species from interstitial to substitutional lattice sites while amorphization damage from the implantation process recrystallizes. A relatively rapid process, peak temperature is often maintained for less than one second to minimize unwanted chemical diffusion.

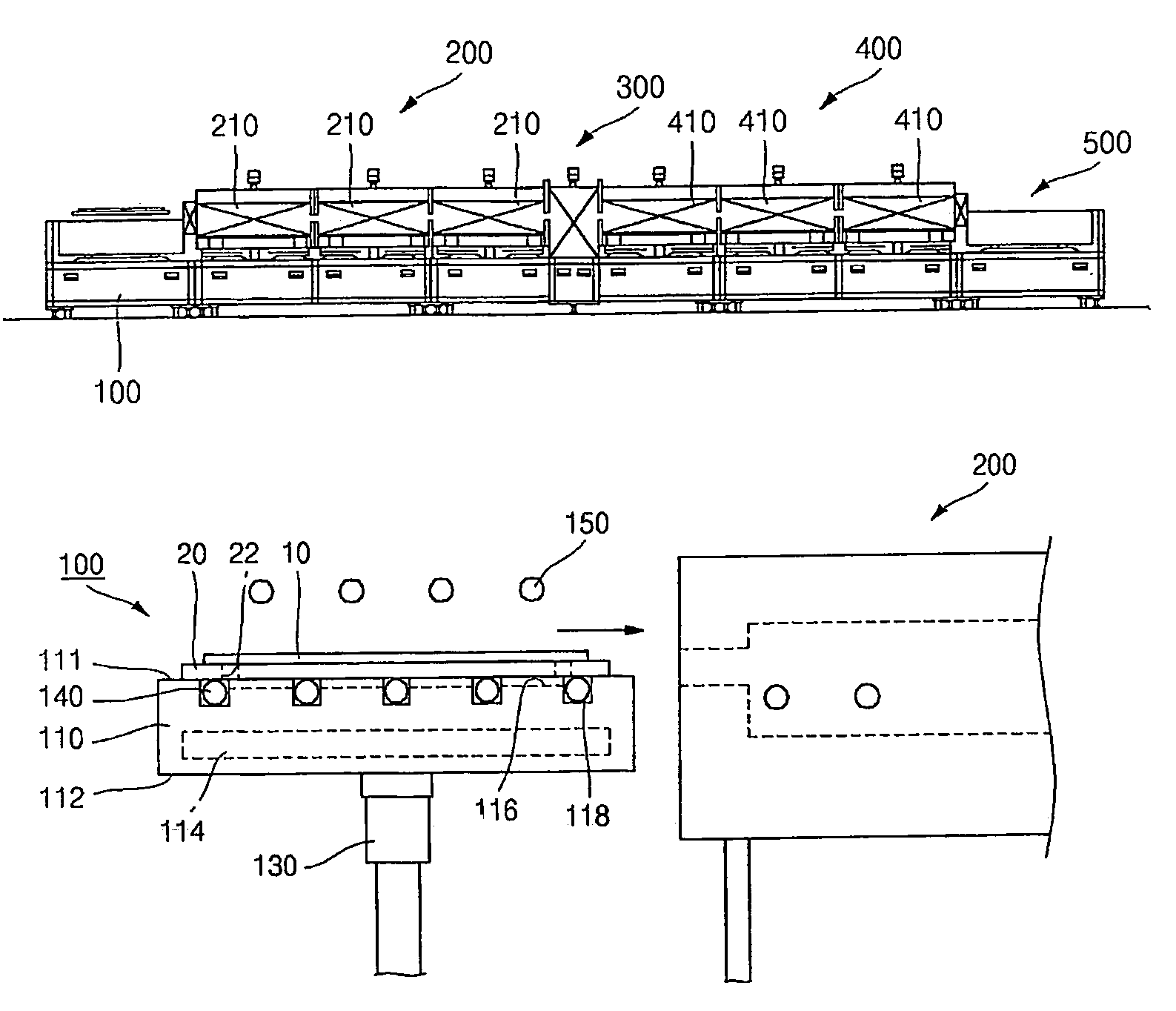

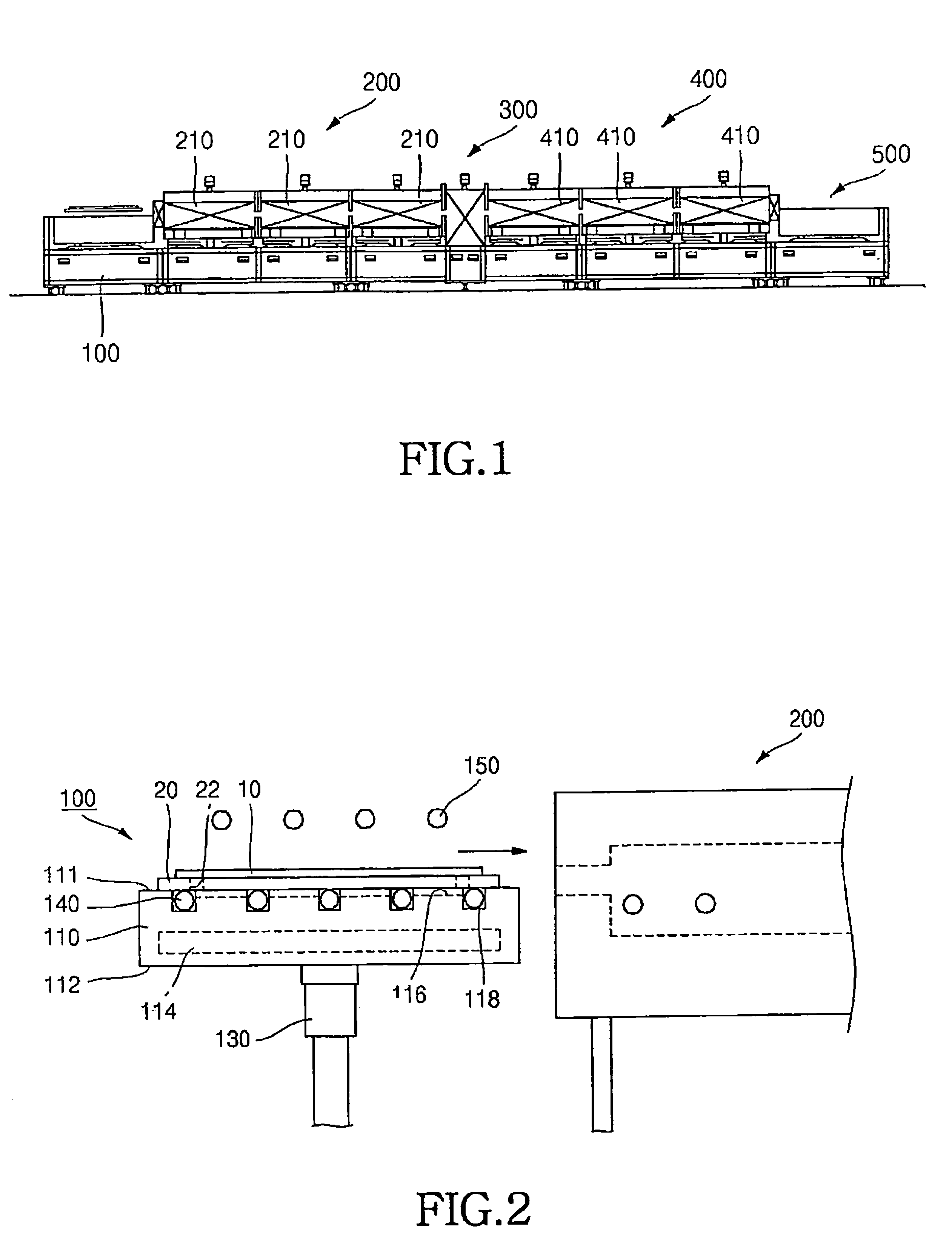

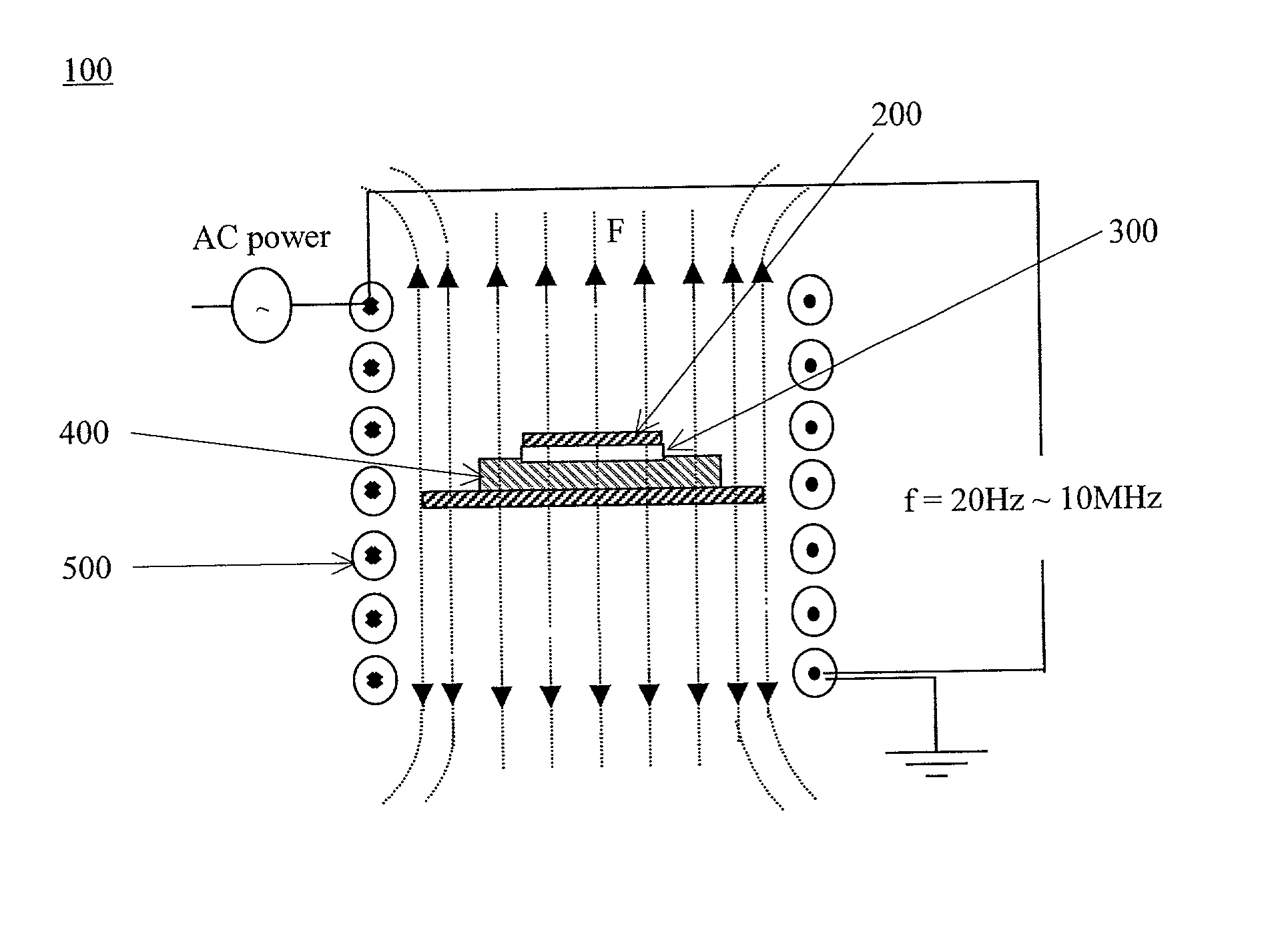

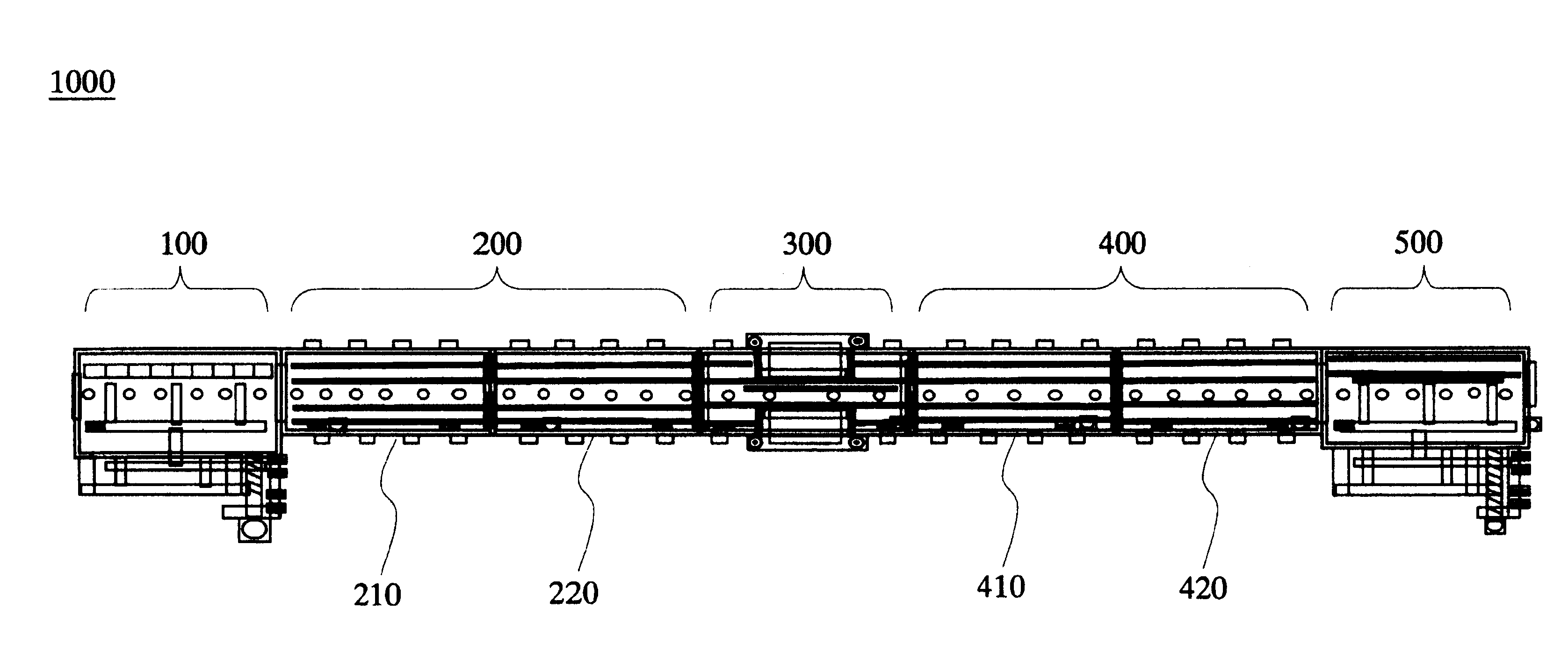

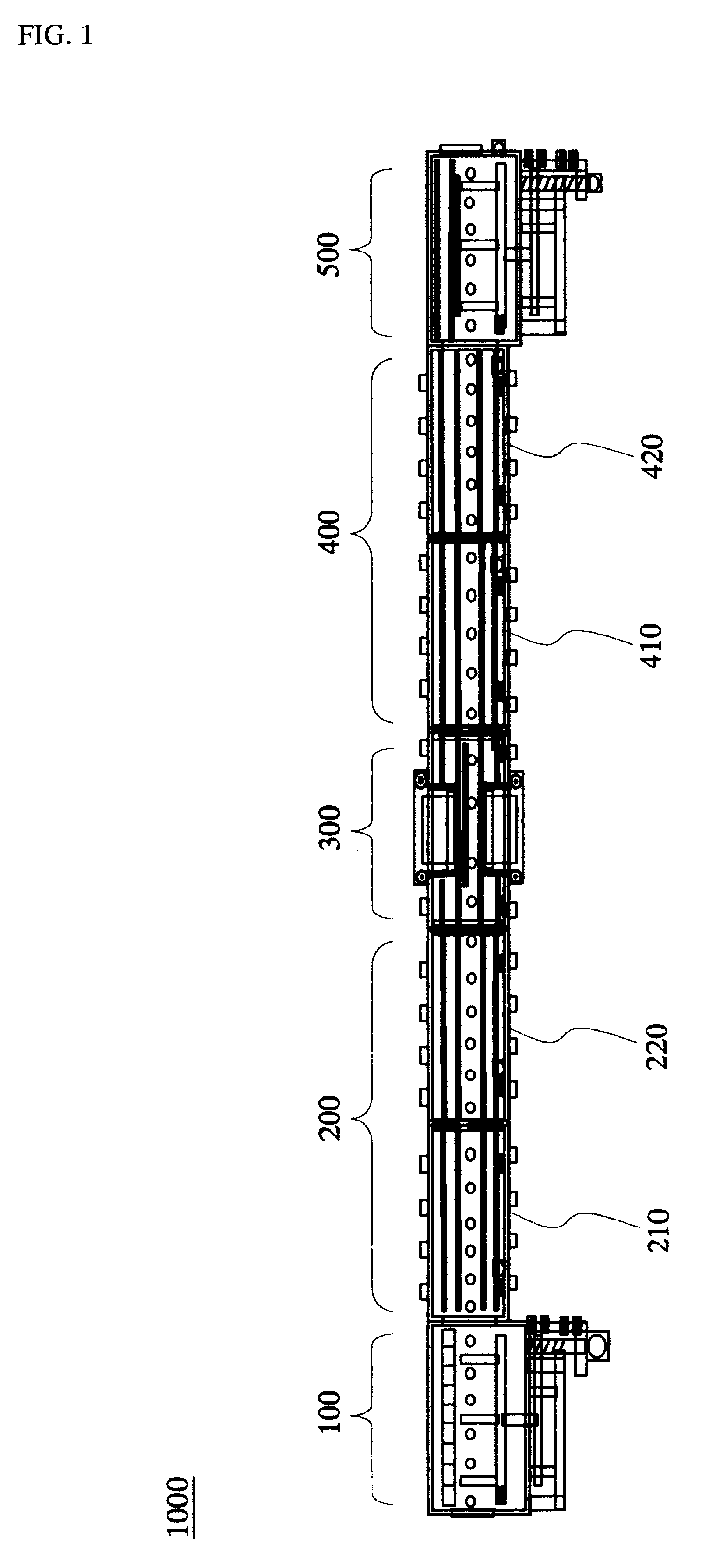

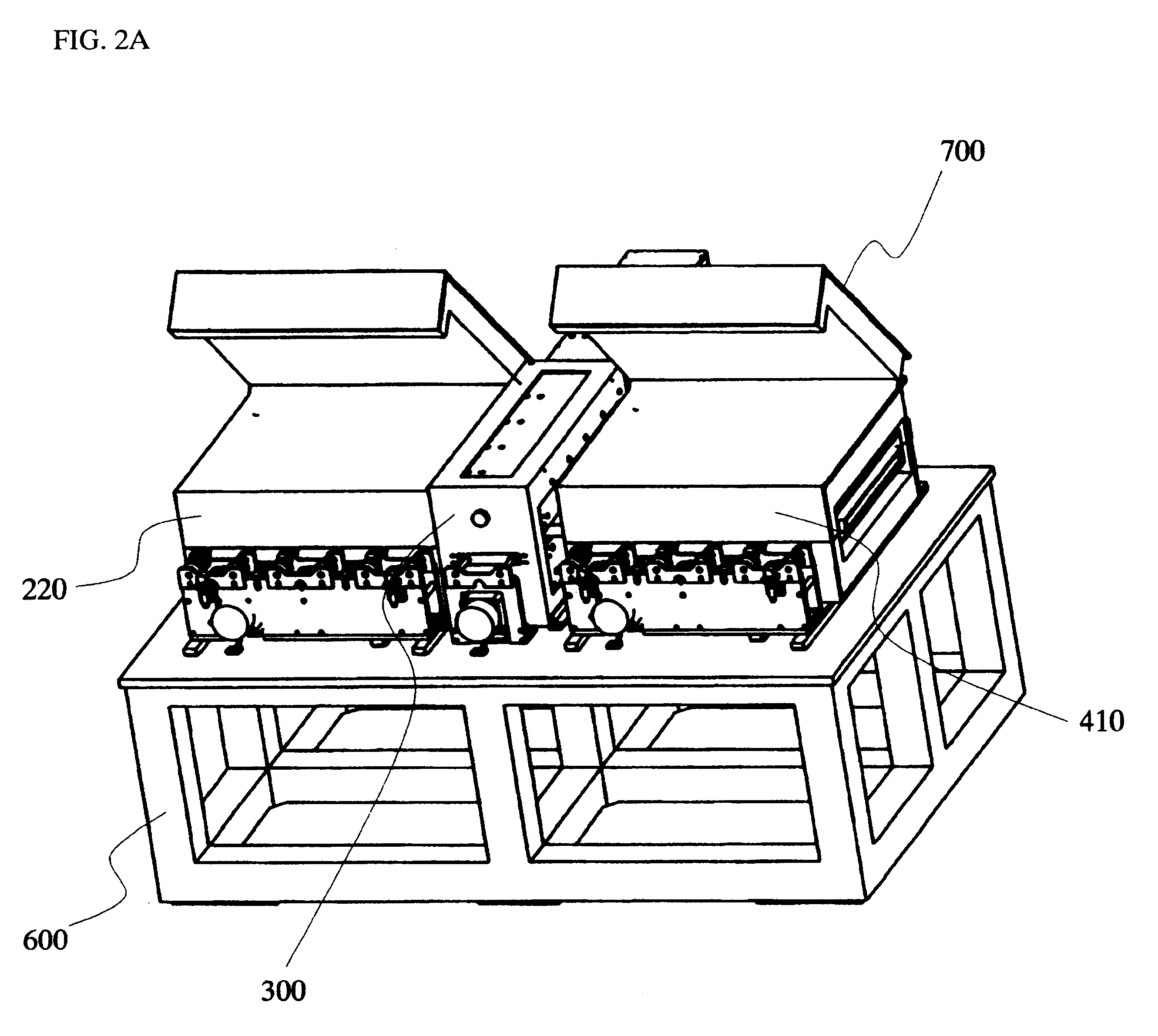

System for heat treatment of semiconductor device

InactiveUS7989736B2Avoid damageIncrease temperatureFurnaces without endless coreSemiconductor/solid-state device manufacturingElectromotive forceSilicon thin film

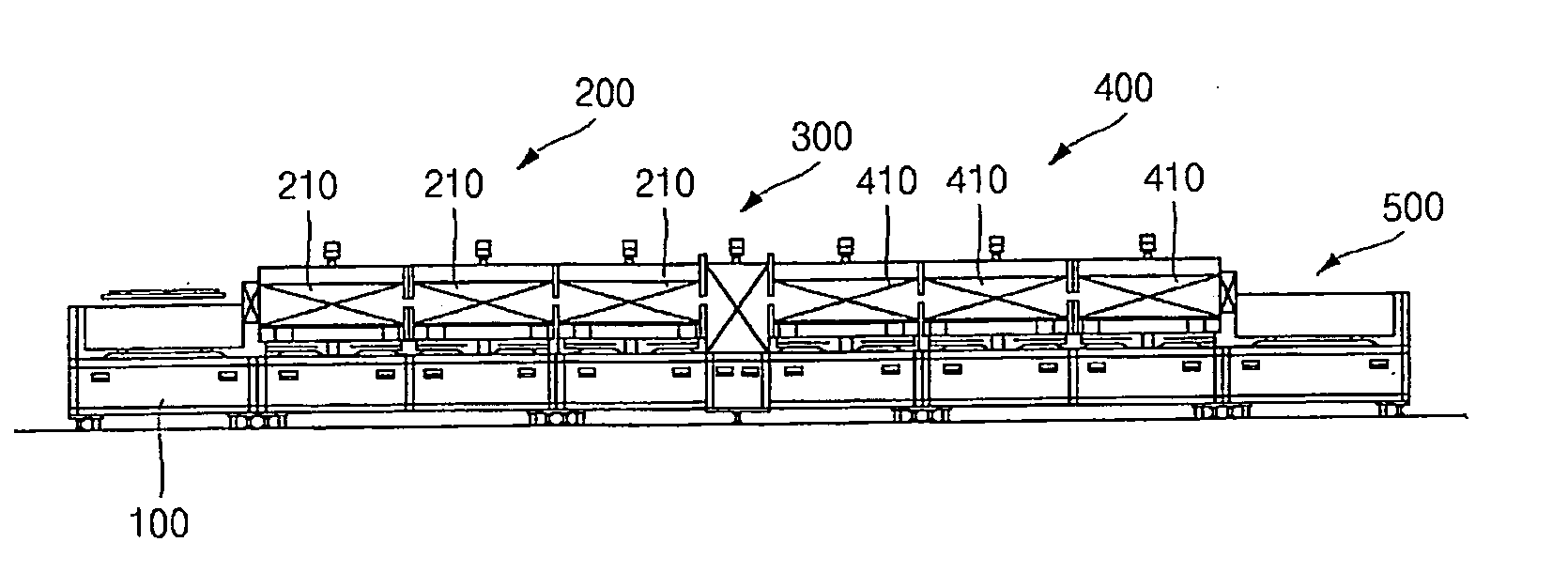

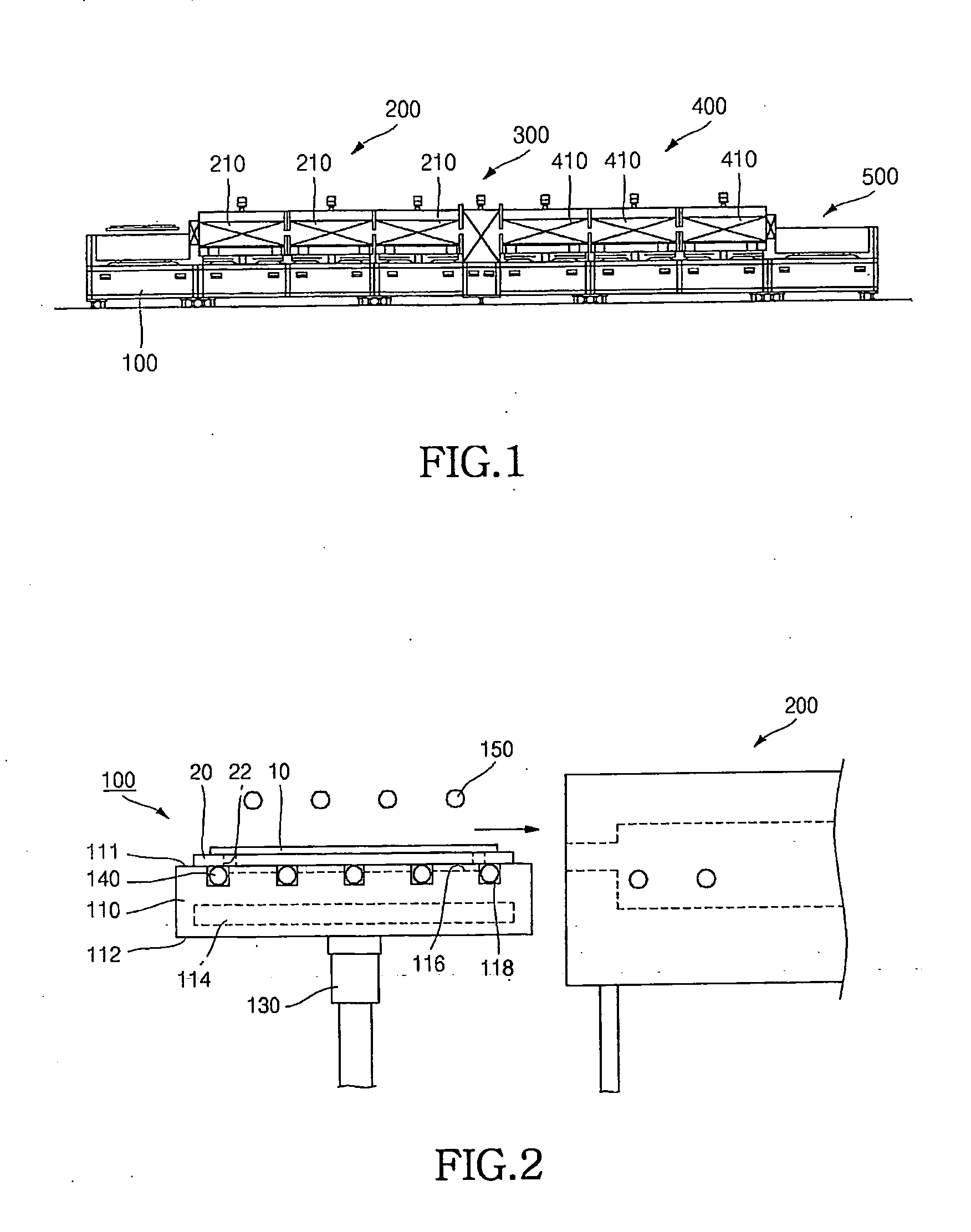

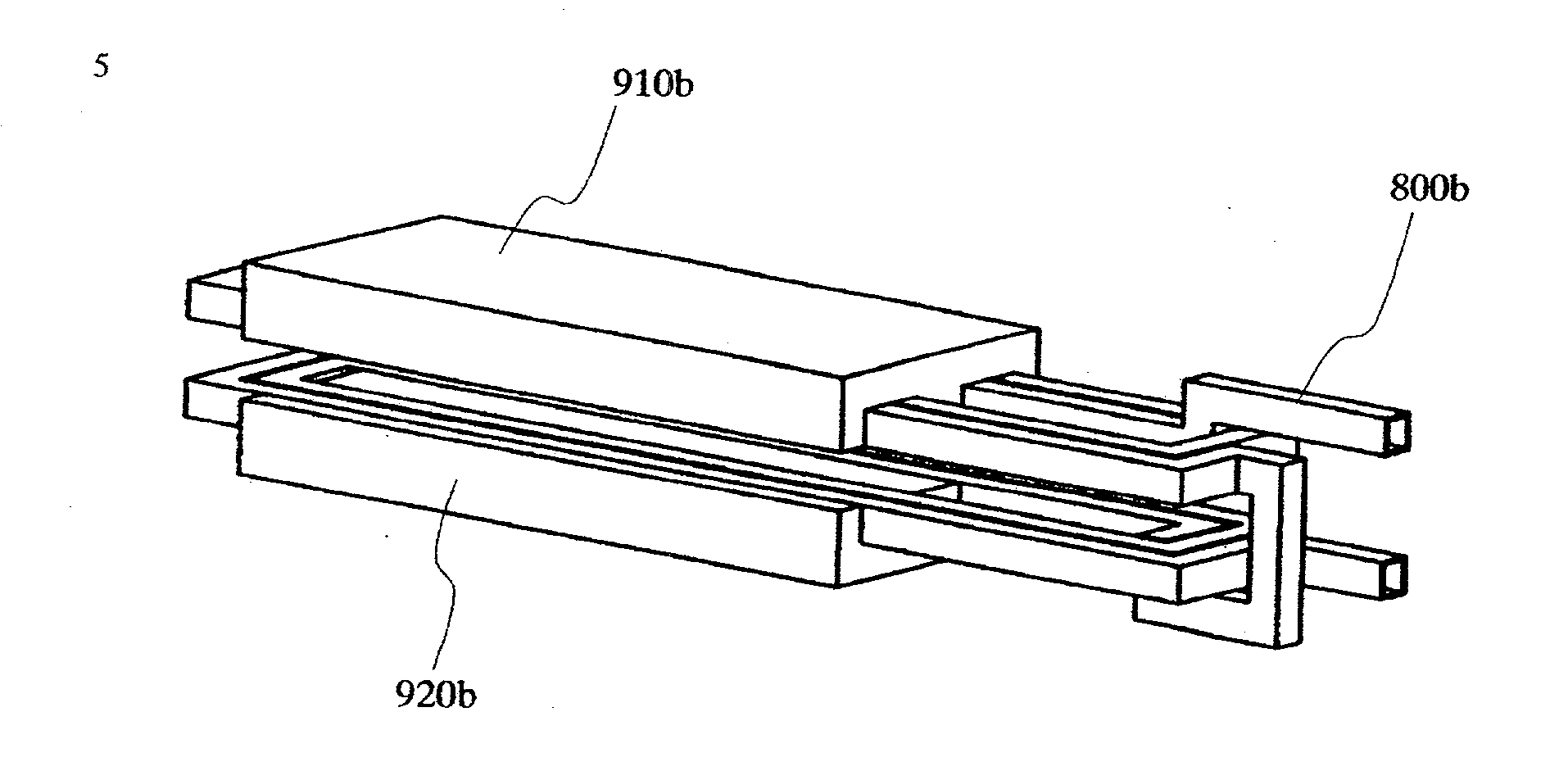

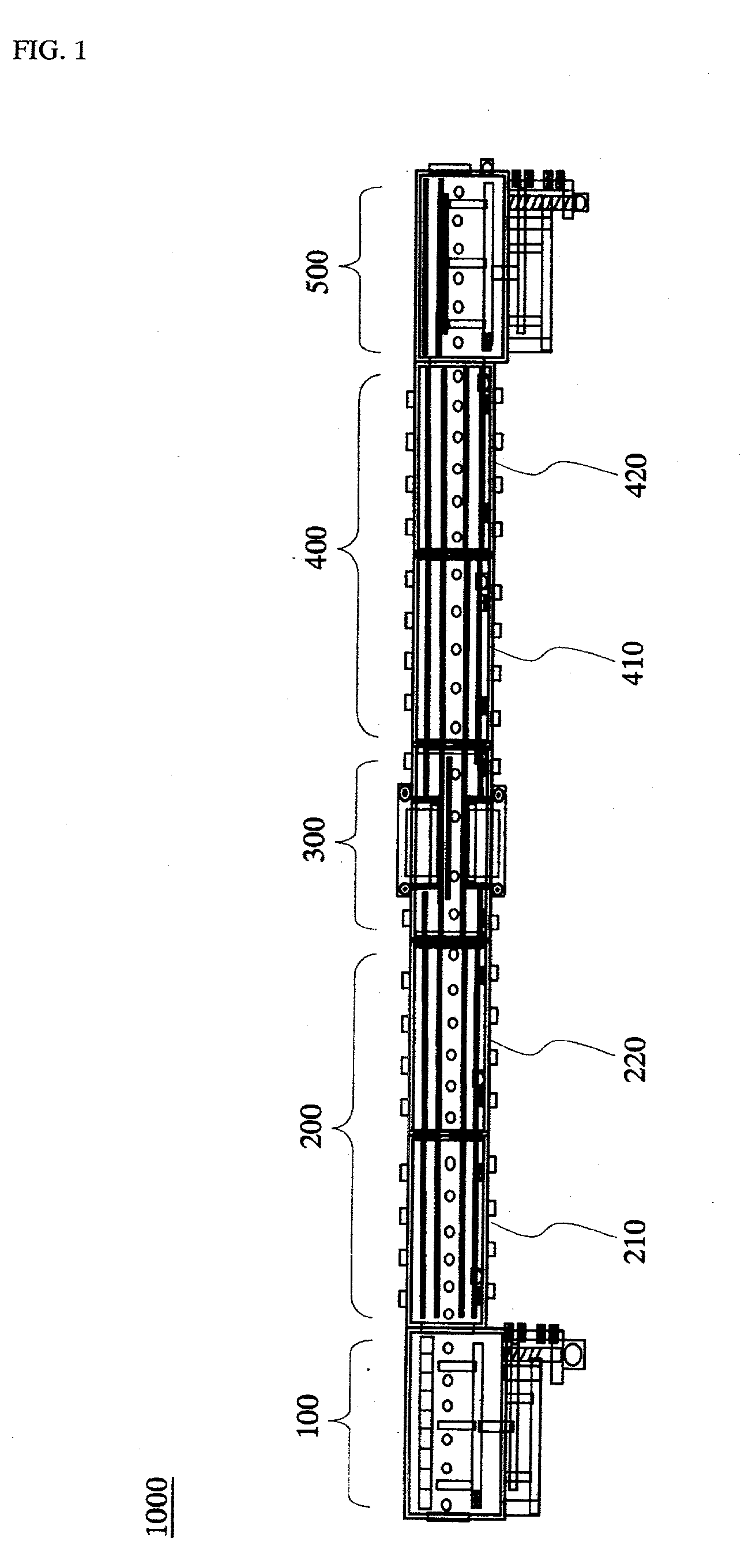

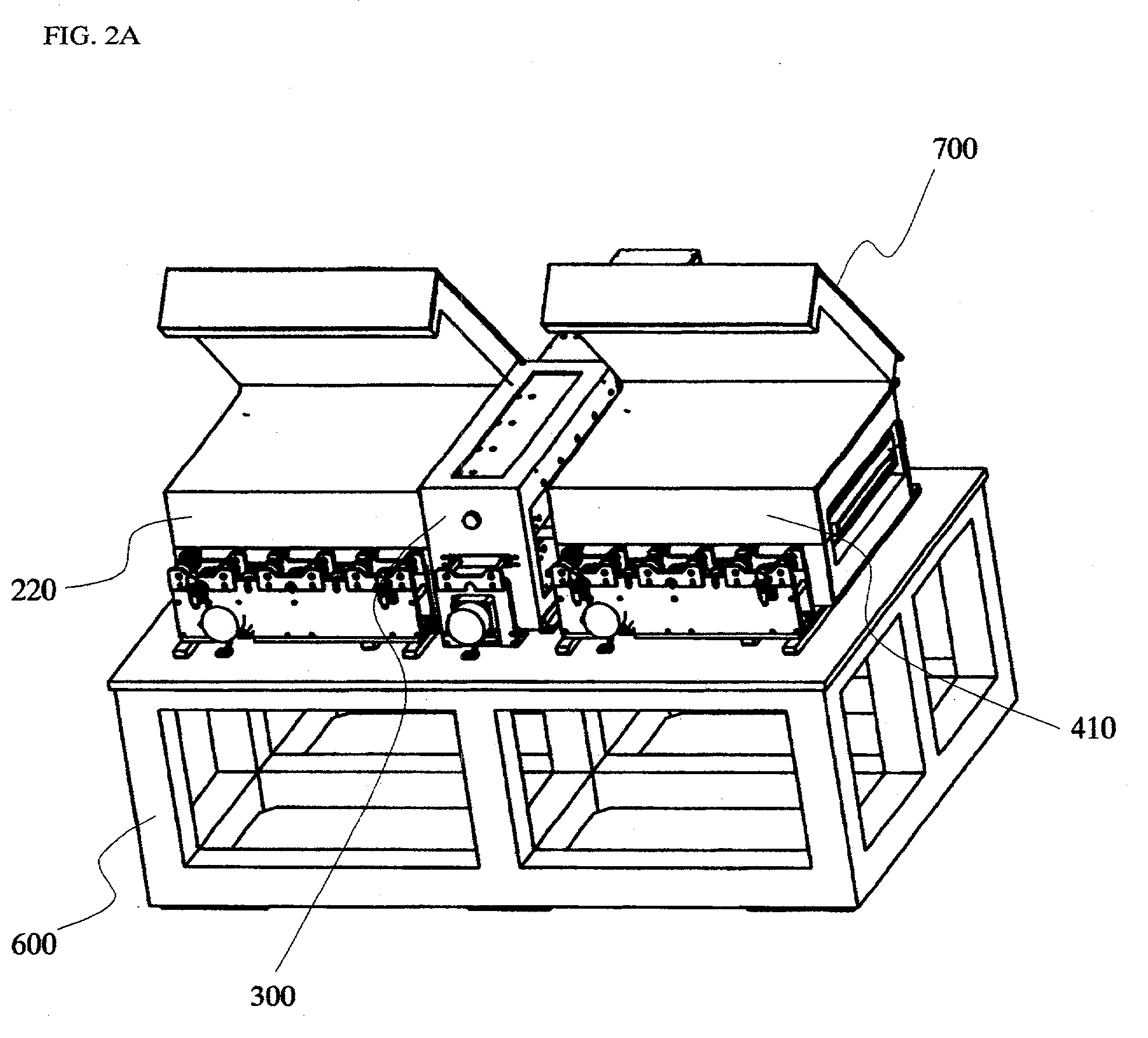

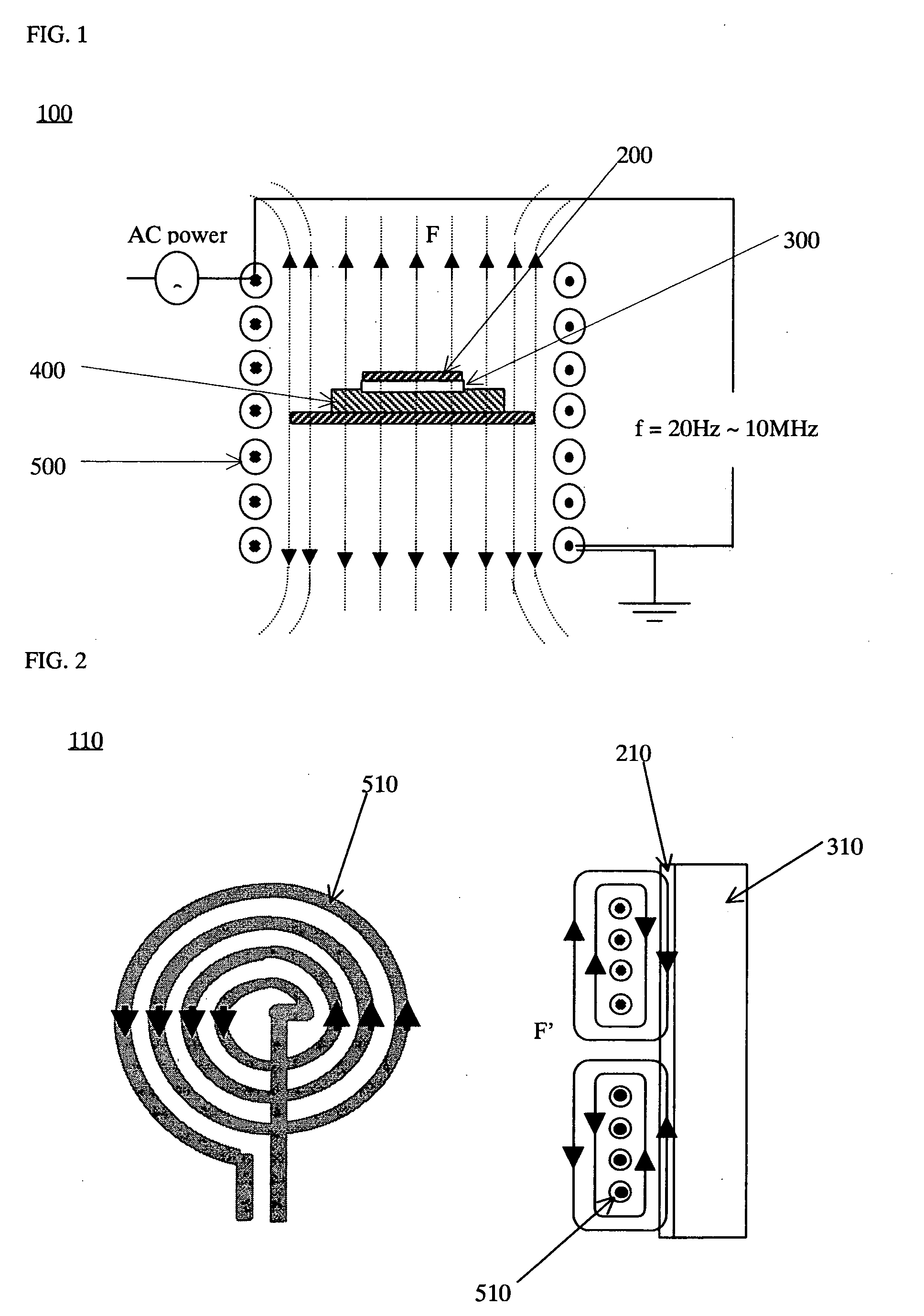

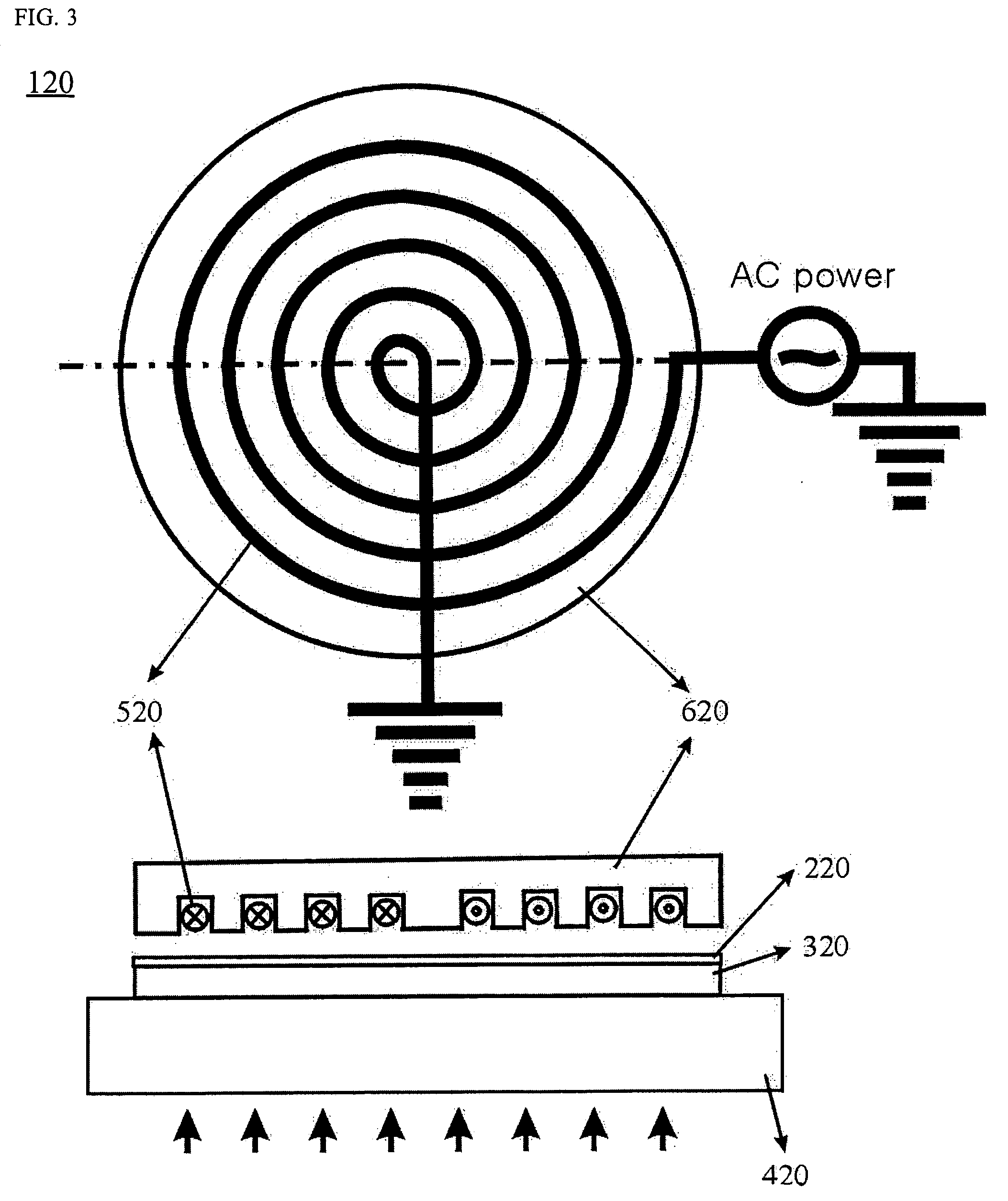

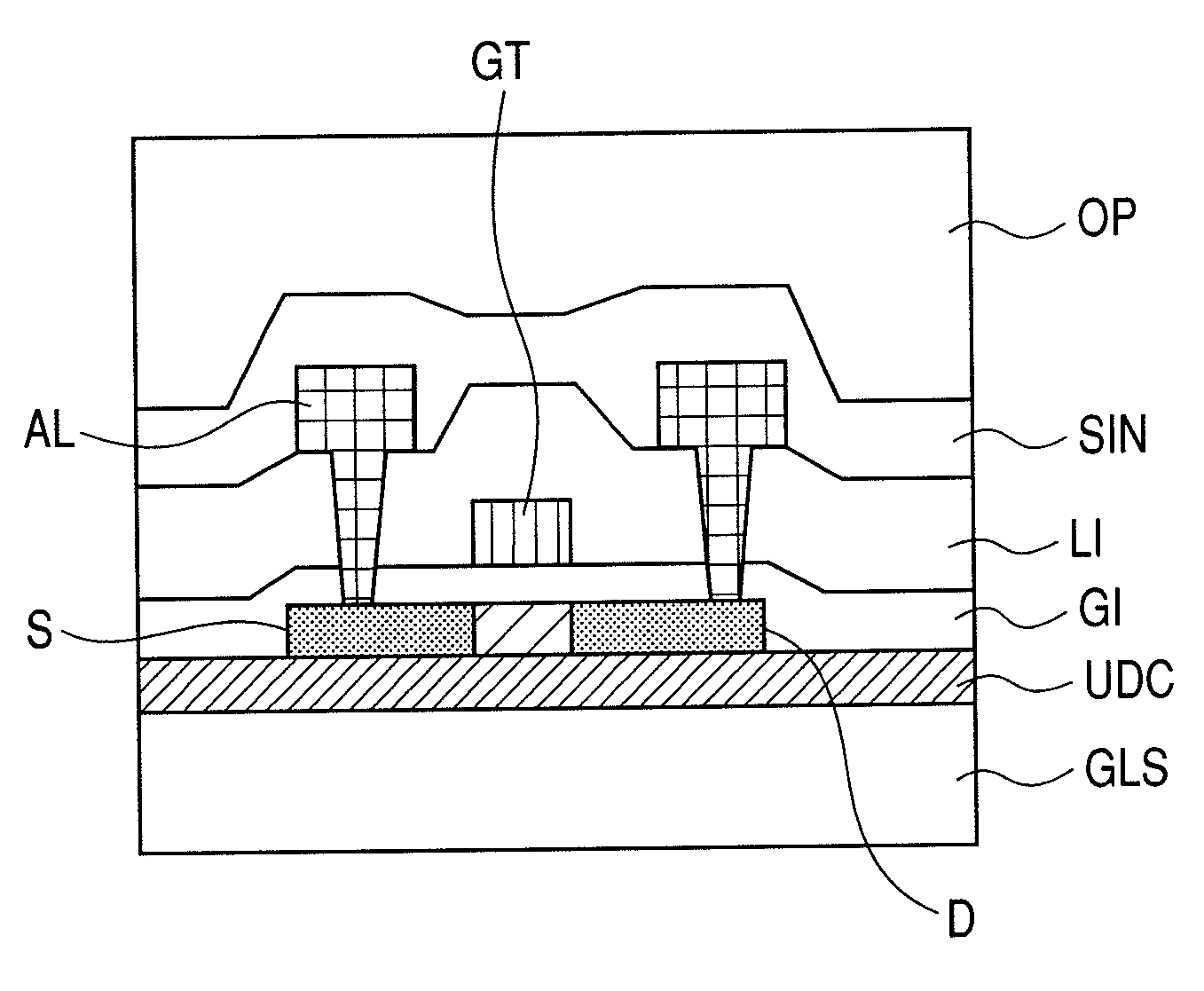

Disclosed is a heat treatment system for semiconductor devices. The heat treatment system is used in a heat treatment process for semiconductor devices, such as a crystallization process for an amorphous silicon thin film or a dopant activation process for a poly-crystalline silicon thin film formed on a surface of a glass substrate of a flat display panel including a liquid crystal display (LCD) or an organic light emitting device (OLED). The heat treatment system transfers a semiconductor device after uniformly preheating the semiconductor device in order to prevent deformation of the semiconductor device during the heat treatment process, rapidly performs the heat treatment process under the high temperature condition by heating the semiconductor device using a lamp heater and induction heat derived from induced electromotive force, and unloads the semiconductor device after uniformly cooling the semiconductor device such that the semiconductor device is prevented from being deformed when the heat treatment process has been finished. The heat treatment system rapidly performs the heat treatment process while preventing deformation of the semiconductor device by gradually heating or cooling the semiconductor device.

Owner:VIATRON TECH INC

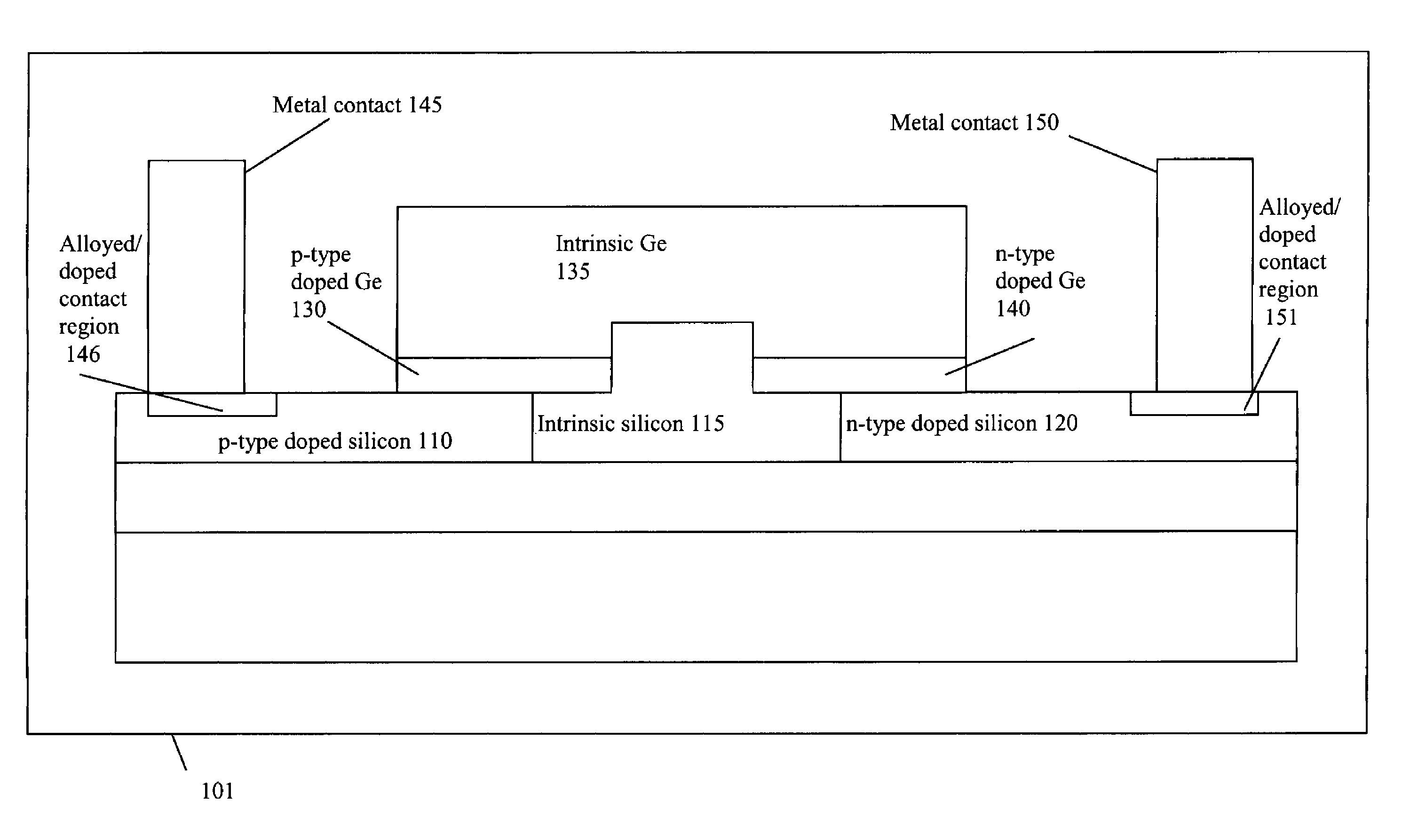

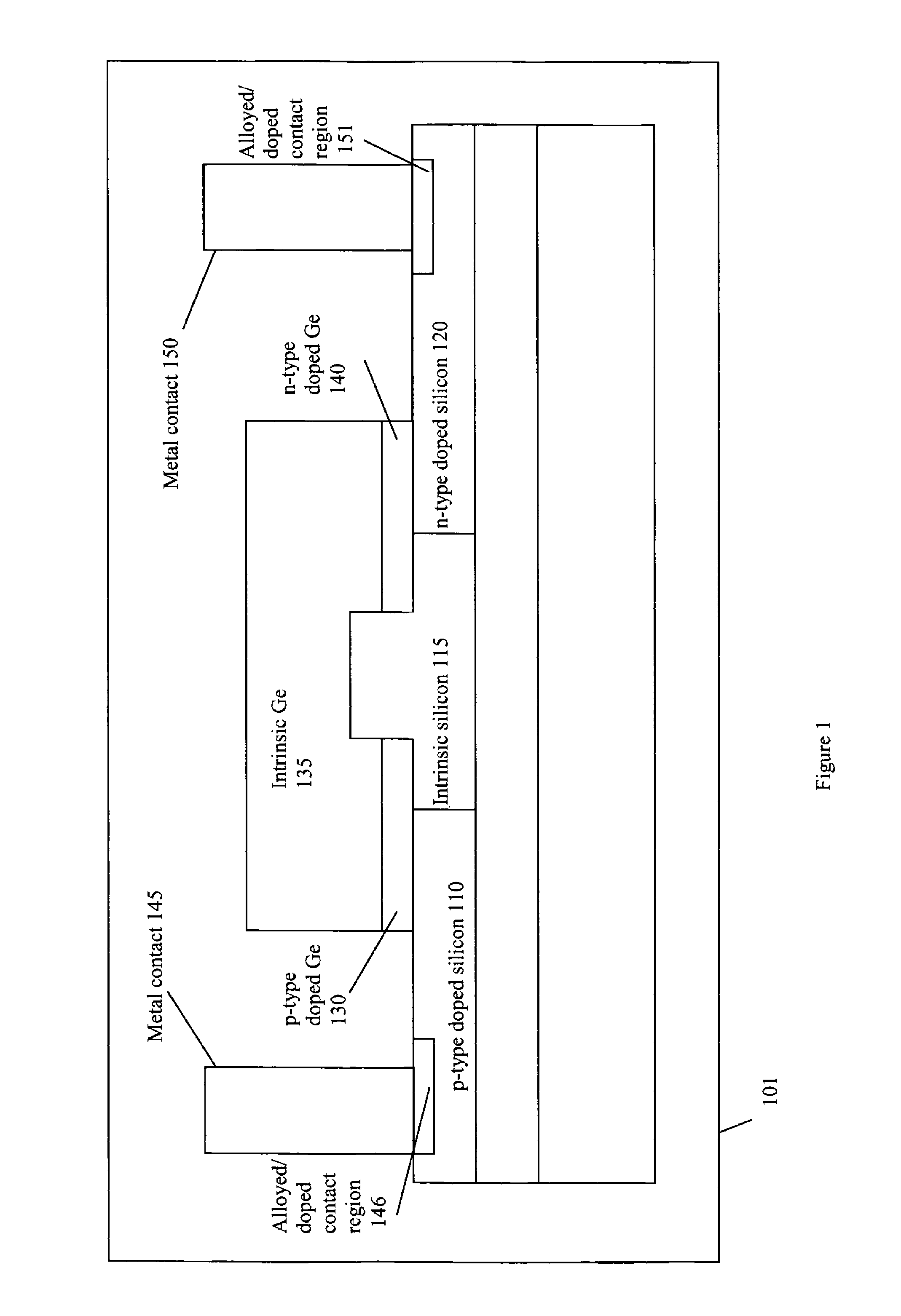

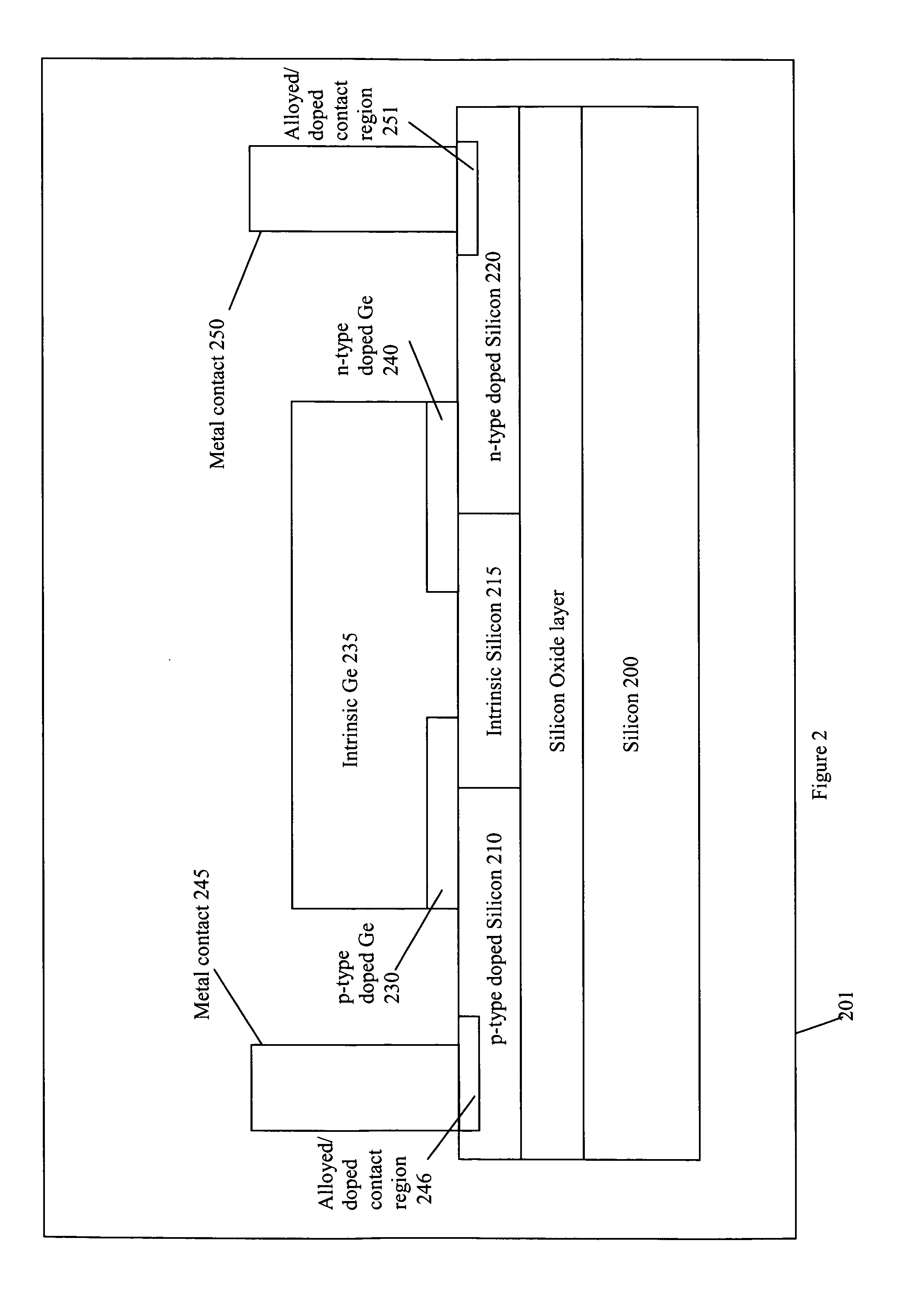

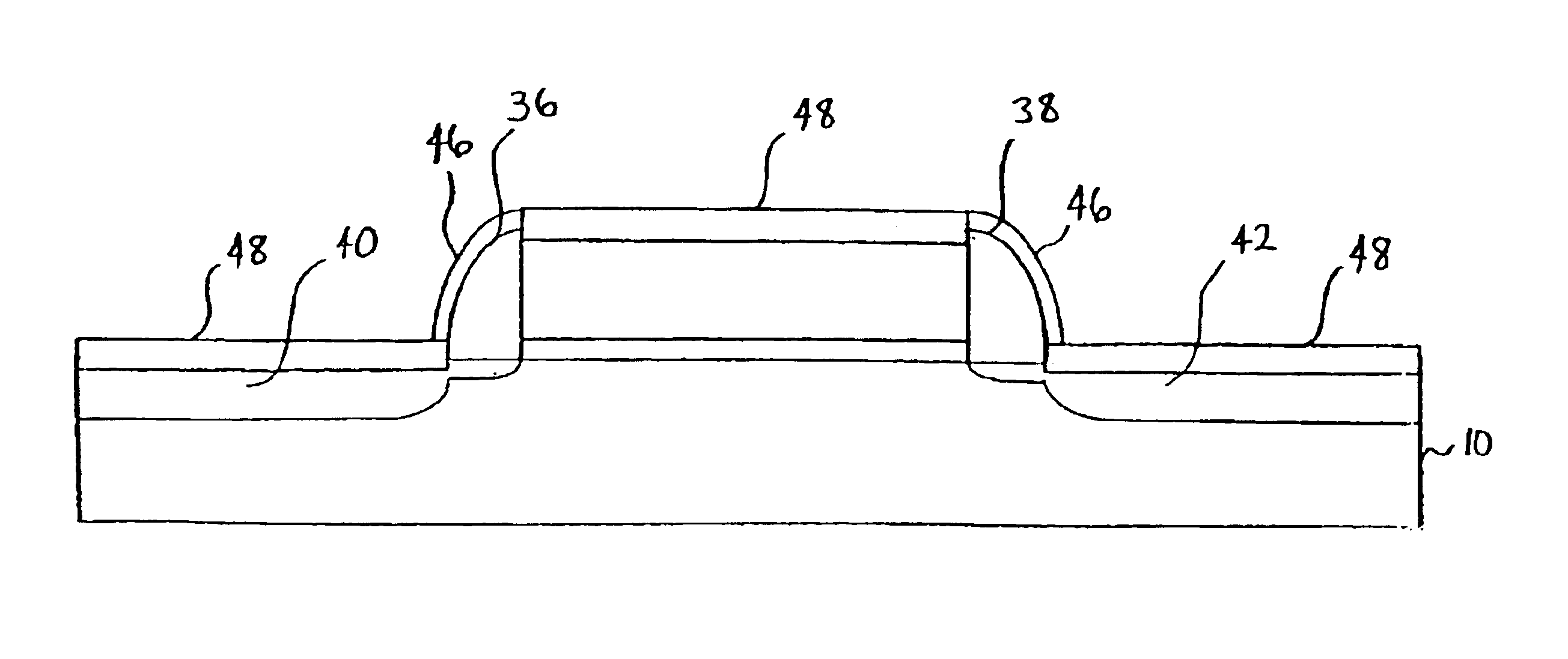

Germanium silicon heterostructure photodetectors

ActiveUS7397101B1Good electrical contactSemiconductor/solid-state device manufacturingPhotovoltaic energy generationPhotovoltaic detectorsPhotodetector

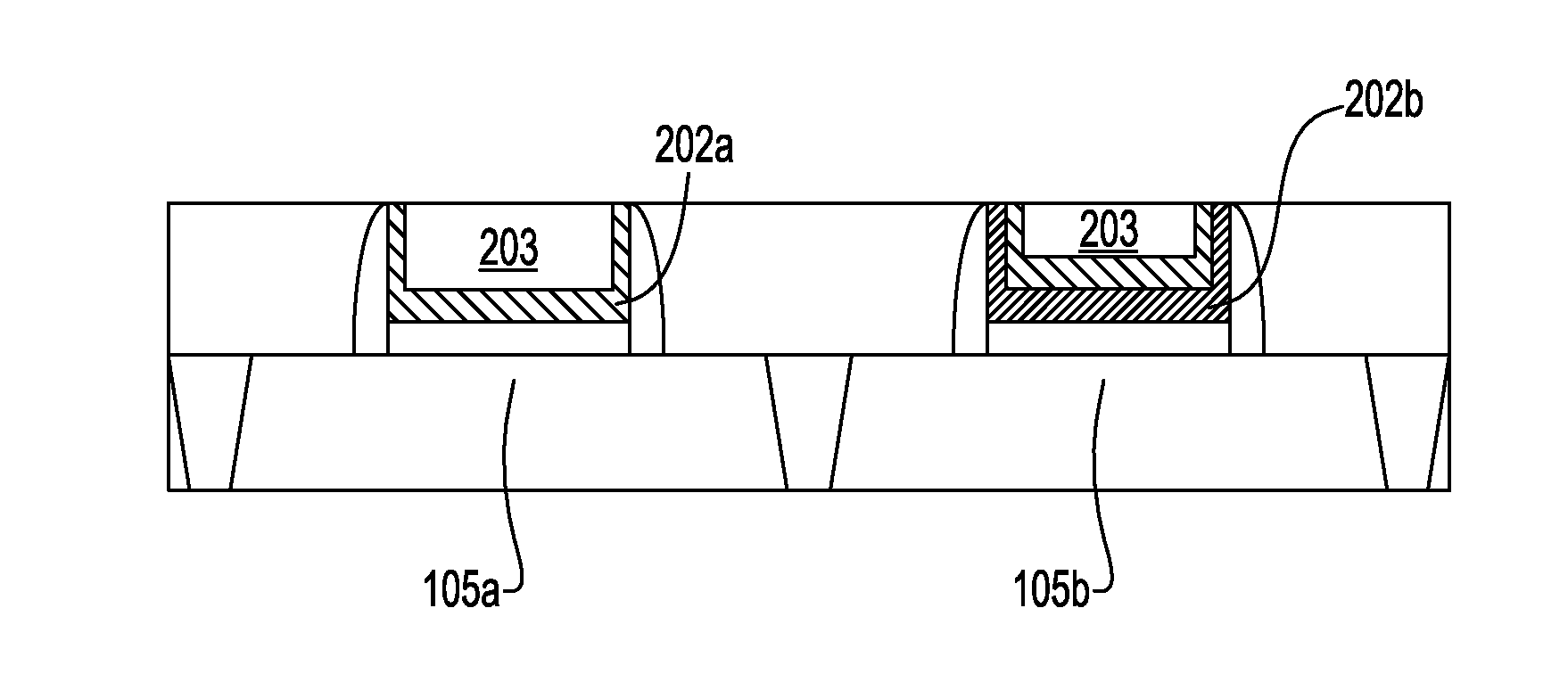

A horizontal germanium silicon heterostructure photodetector comprising a horizontal germanium p-i-n diode disposed over a horizontal parasitic silicon p-i-n diode uses silicon contacts for electrically coupling to the germanium p-i-n through the p-type doped and n-type doped regions in the silicon p-i-n without requiring direct physical contact to germanium material. The current invention may be optically coupled to on-chip and / or off-chip optical waveguide through end-fire or evanescent coupling. In some cases, the doping of the germanium p-type doped and / or n-type doped region may be accomplished based on out-diffusion of dopants in the doped silicon material of the underlying parasitic silicon p-i-n during high temperature steps in the fabrication process such as, the germanium deposition step(s), cyclic annealing, contact annealing and / or dopant activation.

Owner:CISCO TECH INC

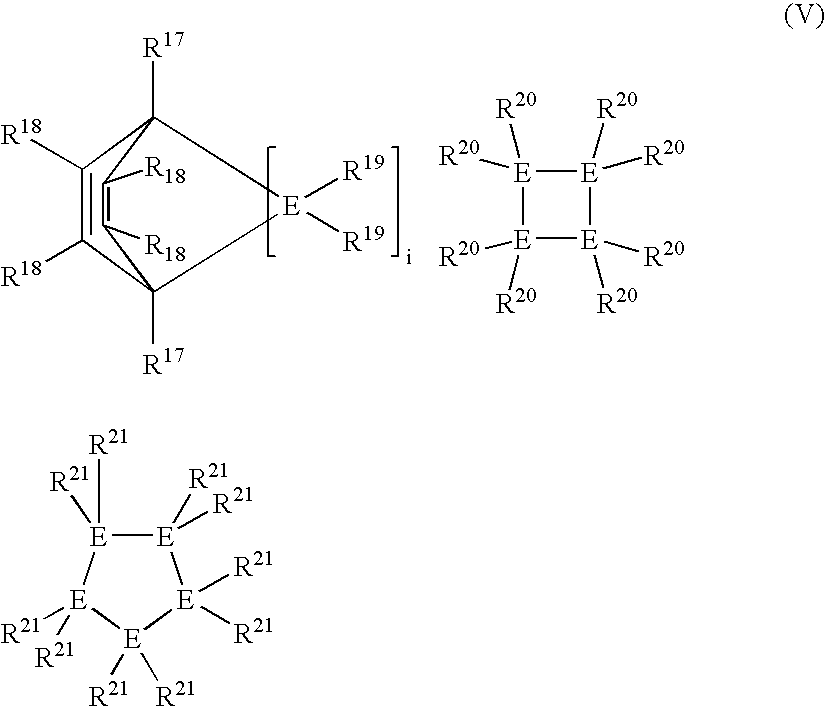

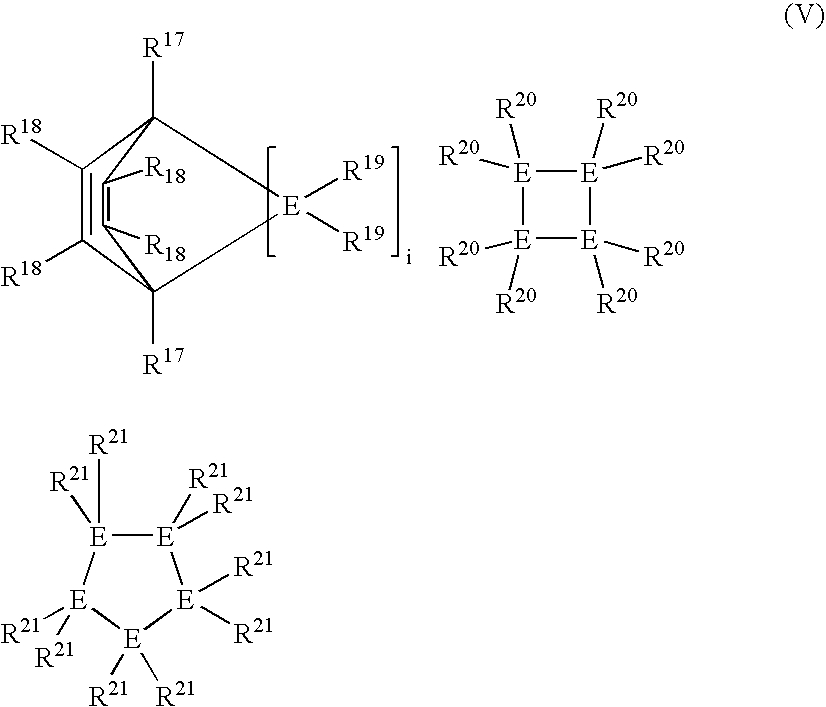

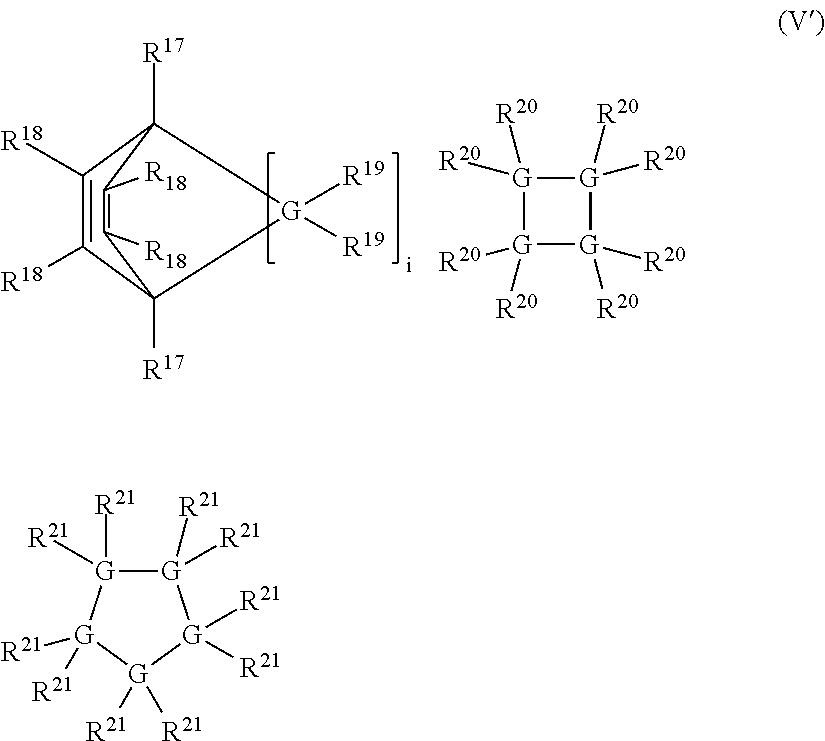

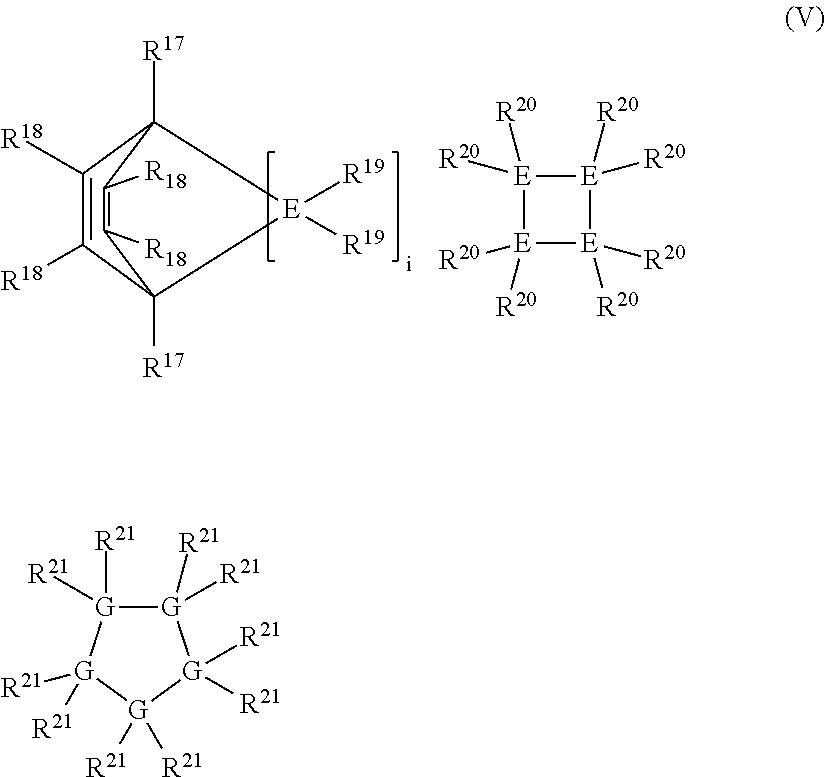

Linear and cross-linked high molecular weight polysilanes, polygermanes, and copolymers thereof, compositions containing the same, and methods of making and using such compounds and compositions

Methods are disclosed of making linear and cross-linked, HMW (high molecular weight) polysilanes and polygermanes, polyperhydrosilanes and polyperhydrogermanes, functional liquids containing the same, and methods of using the liquids in a range of desirable applications. The silane and germane polymers are generally composed of chains of Si and / or Ge substituted with R′ substituents, where each instance of R′ is, for example, independently hydrogen, halogen, alkenyl, alkynyl, hydrocarbyl, aromatic hydrocarbyl, heterocyclic aromatic hydrocarbyl, SiR″3, GeR″3, PR″2, OR″, NR″2, or SR″; where each instance of R″ is independently hydrogen or hydrocarbyl. The cross-linked polymers can be synthesized by dehalogenative coupling or dehydrocoupling. The linear polymers can be synthesized by ring-opening polymerization. The polymers can be further modified by halogenation and / or reaction with the source of hydride to furnish perhydrosilane and perhydrogermane polymers, which are used in liquid ink formulations. The synthesis allows for tuning of the liquid properties (e.g., viscosity, volatility, and surface tension). The liquids can be used for deposition of films and bodies by spincoating, inkjetting, dropcasting, etc., with or without the use of UV irradiation. The deposited films can be converted into amorphous and polycrystalline silicon or germanium, and silicon or germanium oxide or nitride by curing at 400-600 DEG C. and (optionally) laser- or heat-induced crystallization (and / or dopant activation, when dopant is present).

Owner:ENSURGE MICROPOWER ASA

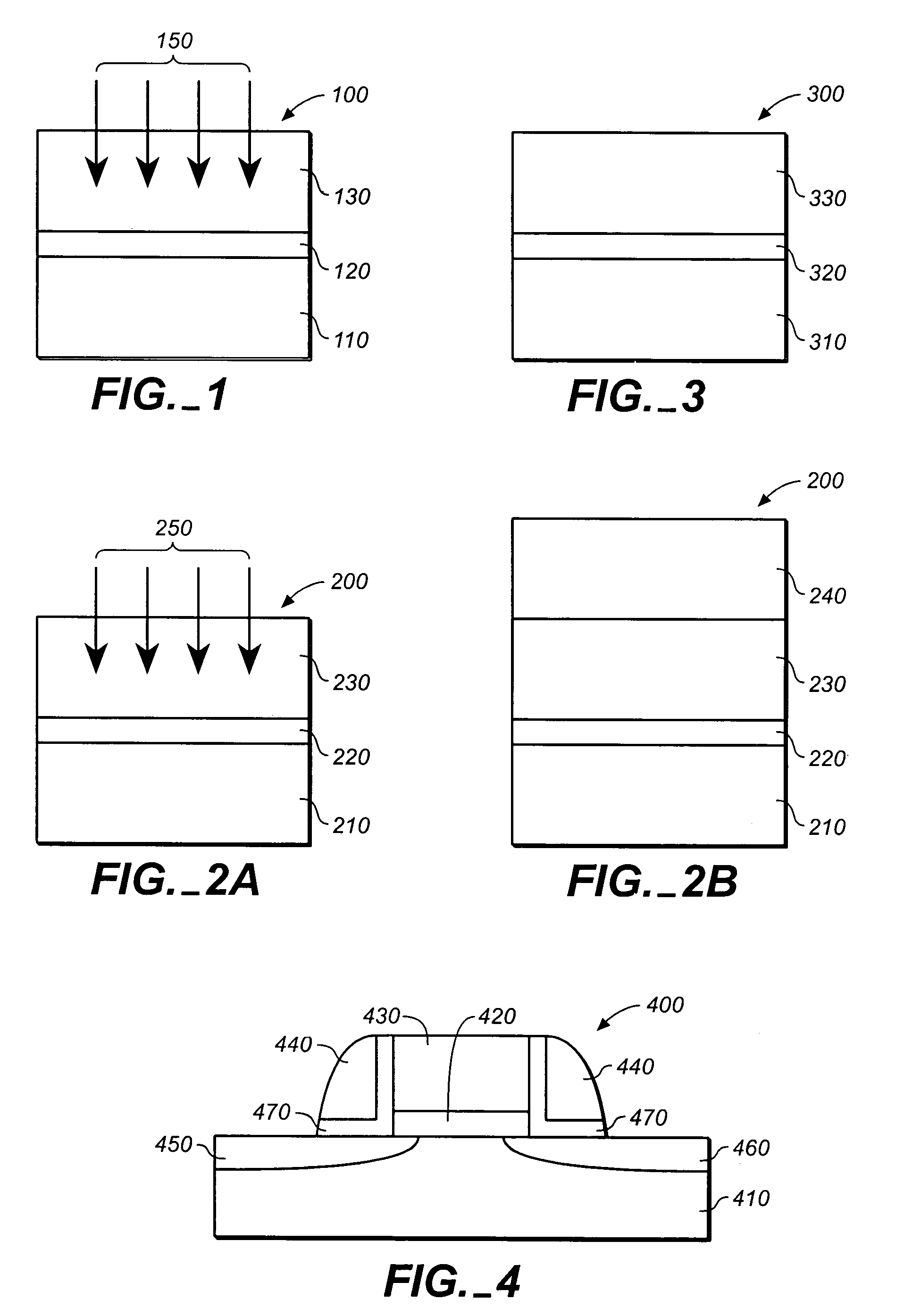

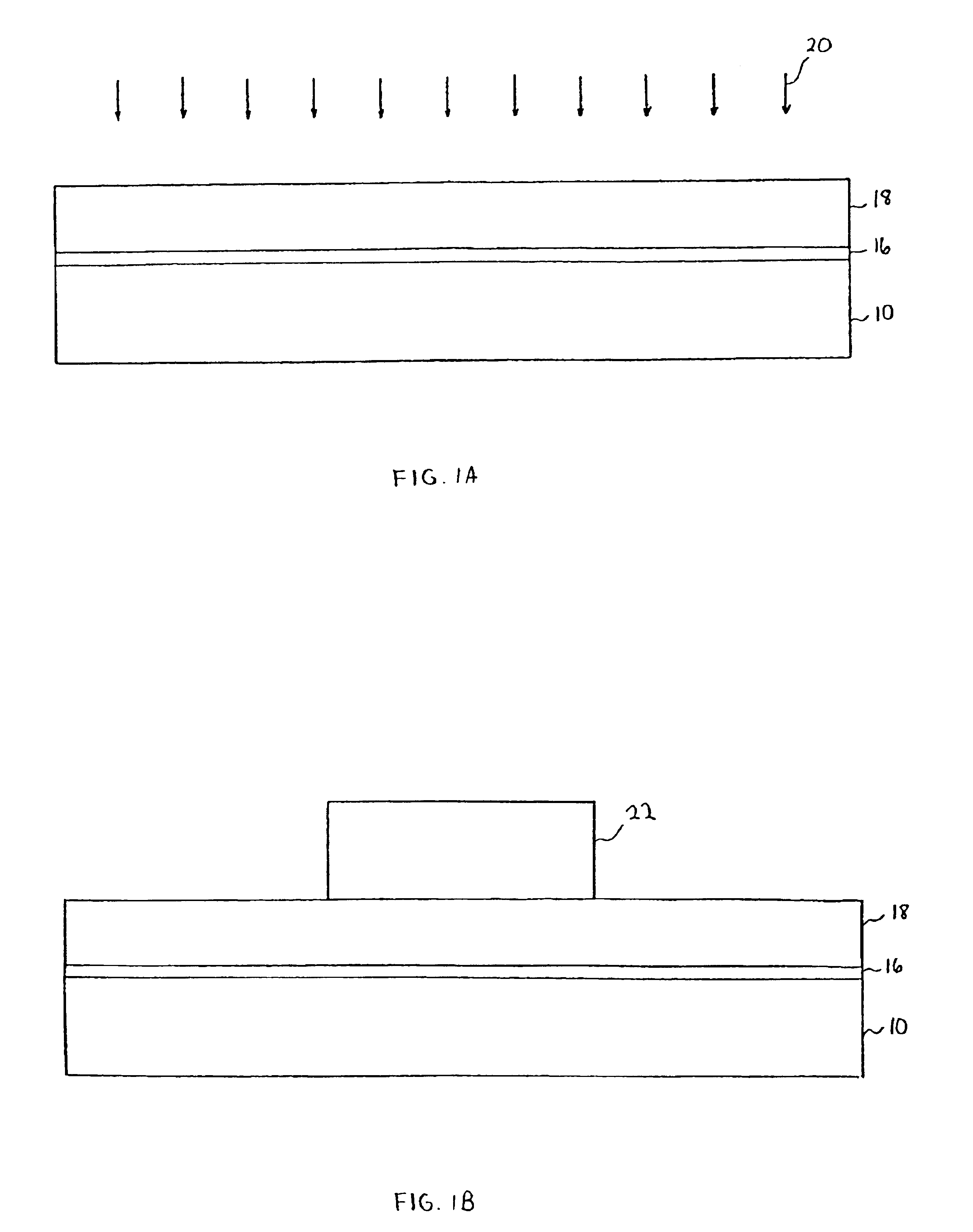

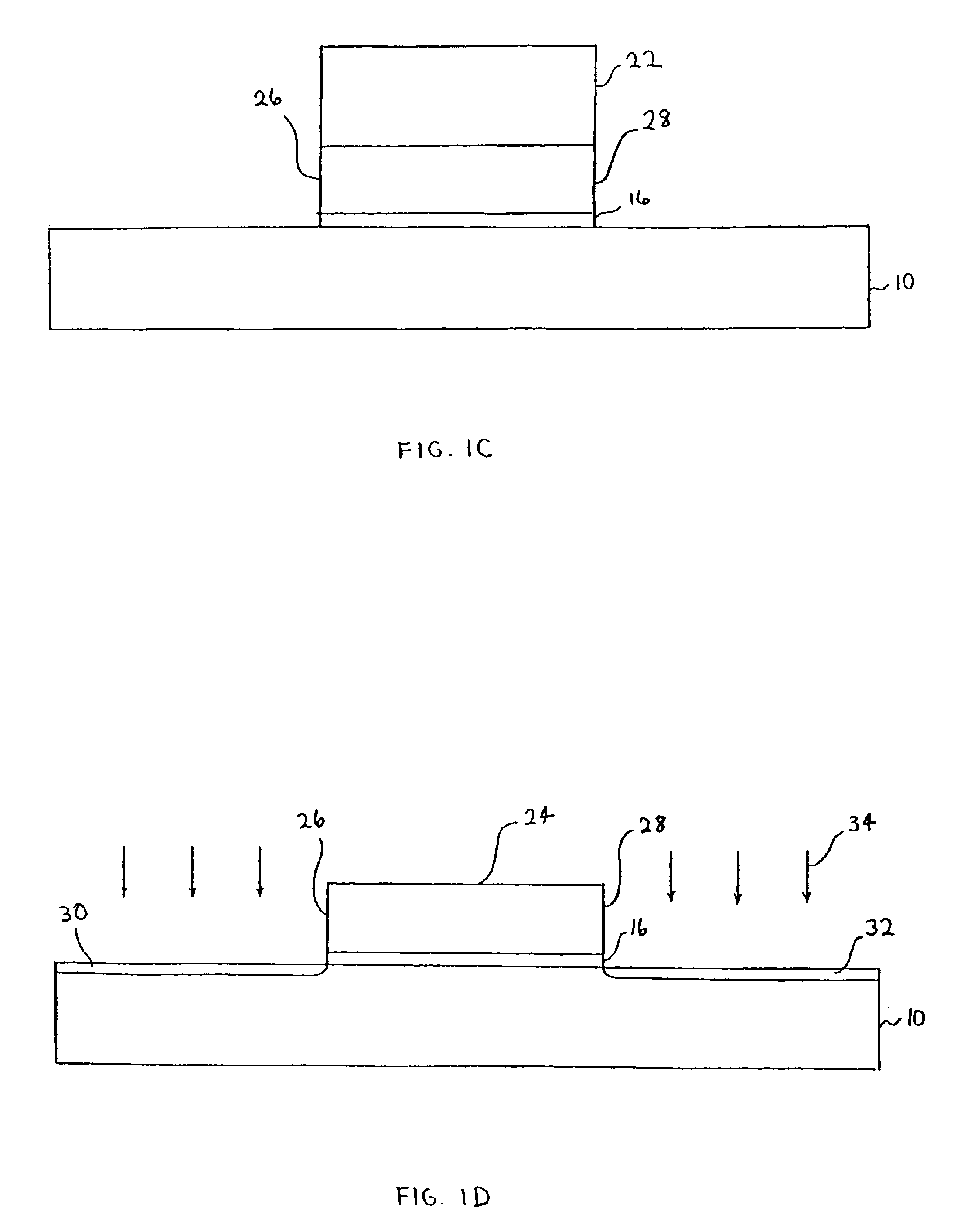

Ultra shallow junction formation by epitaxial interface limited diffusion

ActiveUS20060076627A1Maximizing dopant activationIncrease oxygen contentSemiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorOxygen content

A method of forming a field effect transistor creates shallower and sharper junctions, while maximizing dopant activation in processes that are consistent with current manufacturing techniques. More specifically, the invention increases the oxygen content of the top surface of a silicon substrate. The top surface of the silicon substrate is preferably cleaned before increasing the oxygen content of the top surface of the silicon substrate. The oxygen content of the top surface of the silicon substrate is higher than other portions of the silicon substrate, but below an amount that would prevent epitaxial growth. This allows the invention to epitaxially grow a silicon layer on the top surface of the silicon substrate. Further, the increased oxygen content substantially limits dopants within the epitaxial silicon layer from moving into the silicon substrate.

Owner:GLOBALFOUNDRIES US INC

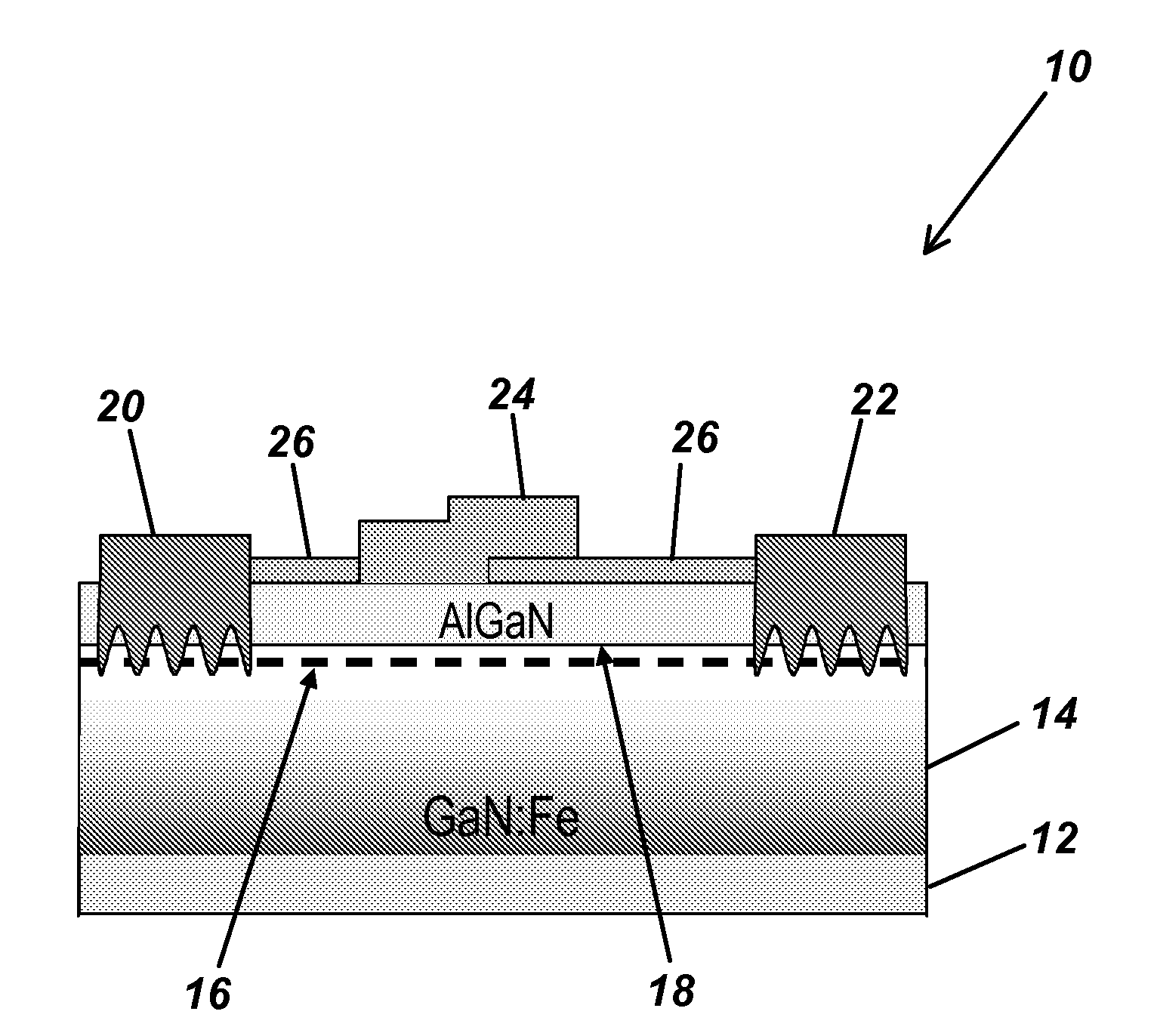

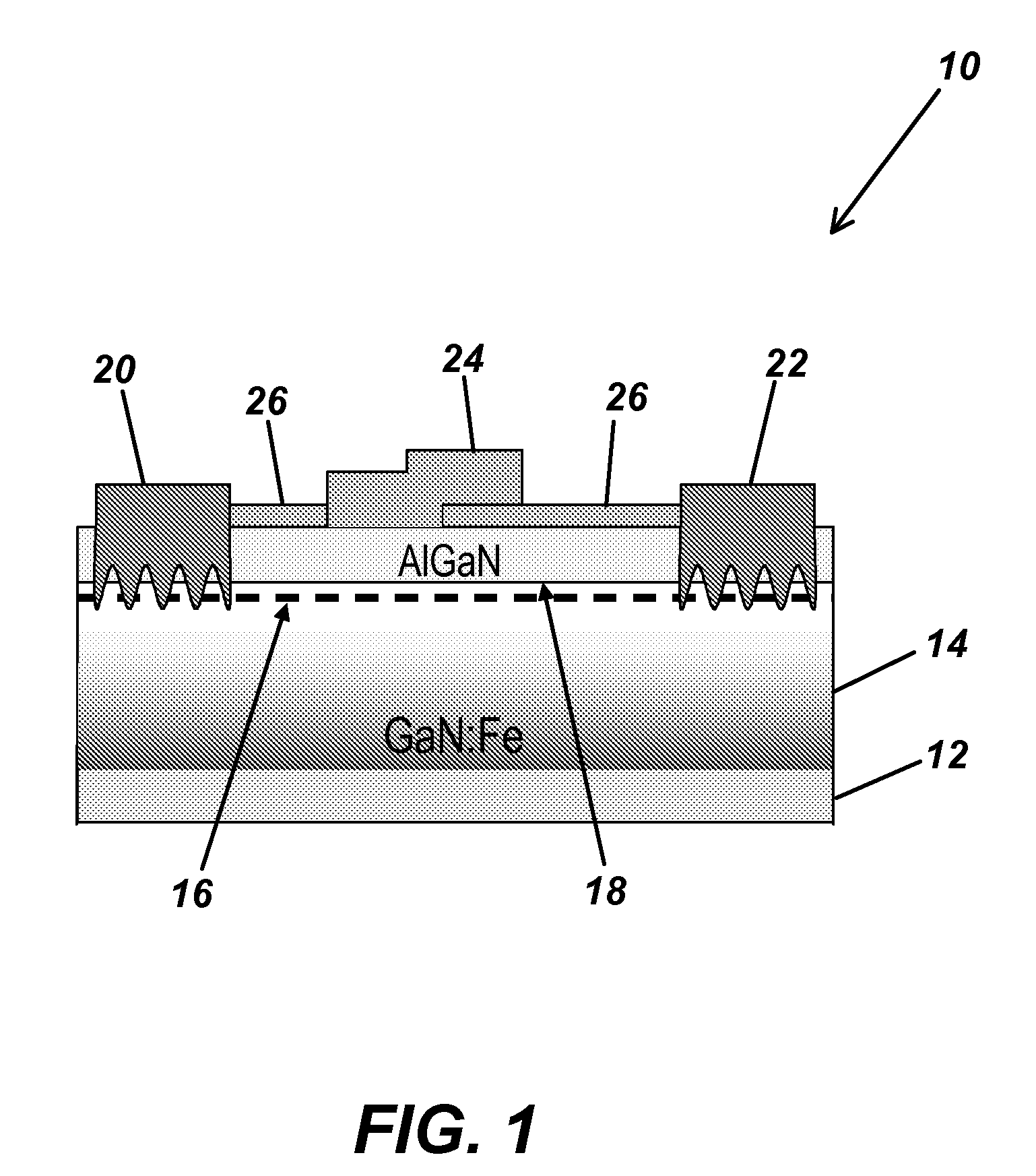

Method to fabricate iii-n field effect transistors using ion implantation with reduced dopant activation and damage recovery temperature

InactiveUS20080258150A1Reduce dopant activation temperatureIncrease temperatureSemiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorMaterials science

Structures to reduce dopant activation temperatures for ion implantation in III-N transistors, using low aluminum content layers in proximity to the conducting channel, are disclosed. A method to increase the temperature at which structures can be annealed by annealing in an active nitrogen ambient, for example, in NH3 in a metalorganic chemical vapor deposition (MOCVD) chamber, is also disclosed.

Owner:RGT UNIV OF CALIFORNIA

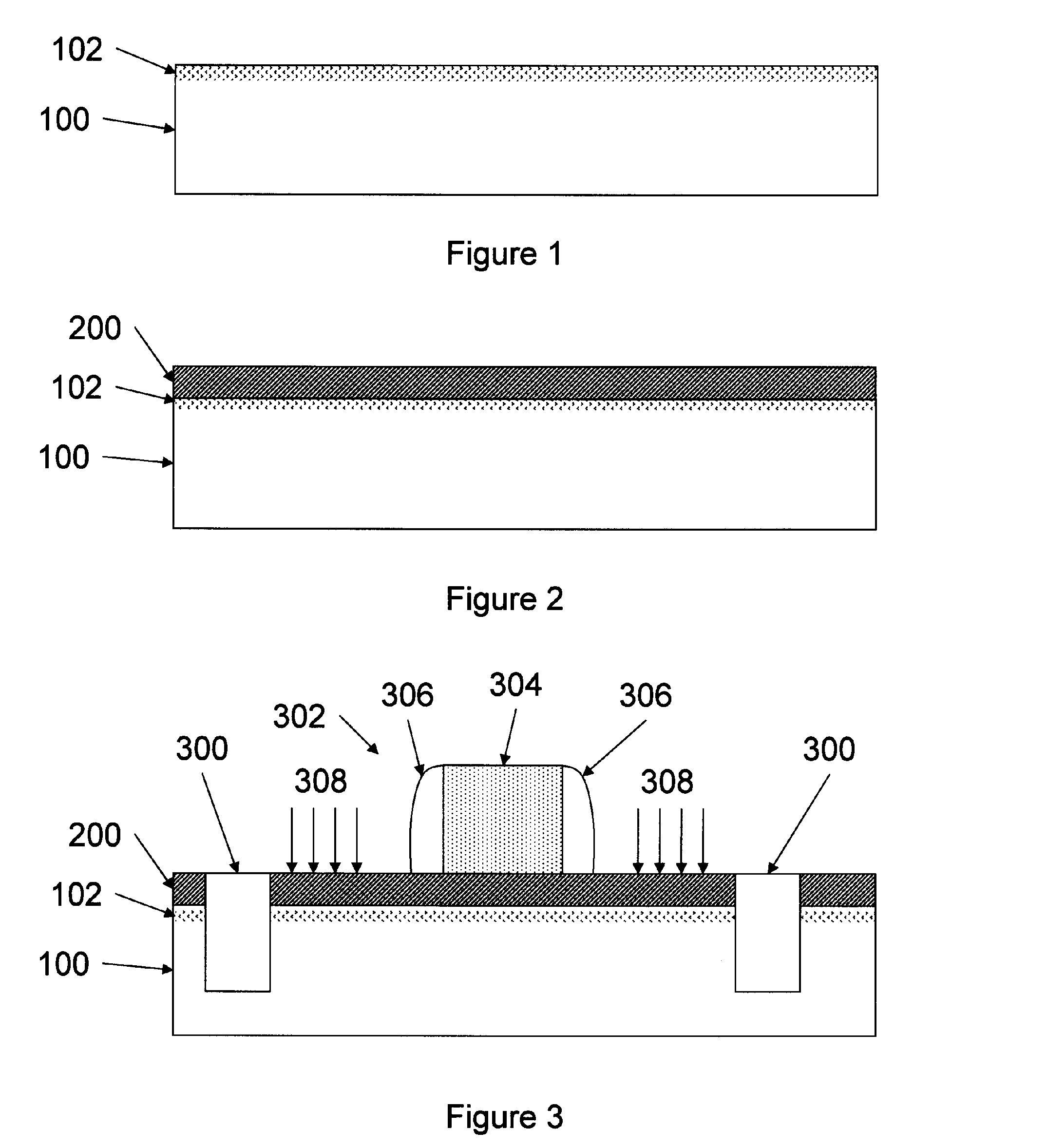

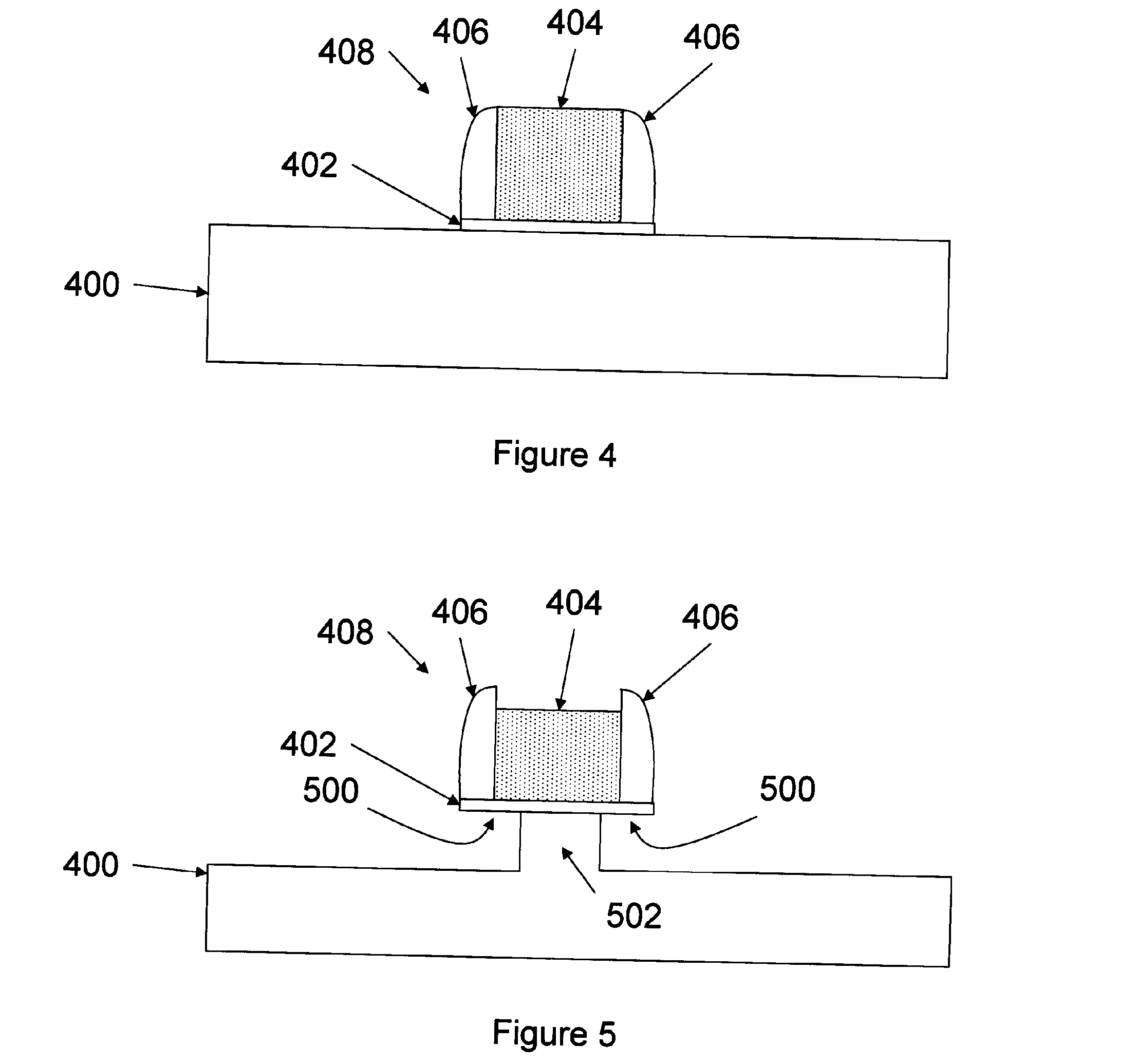

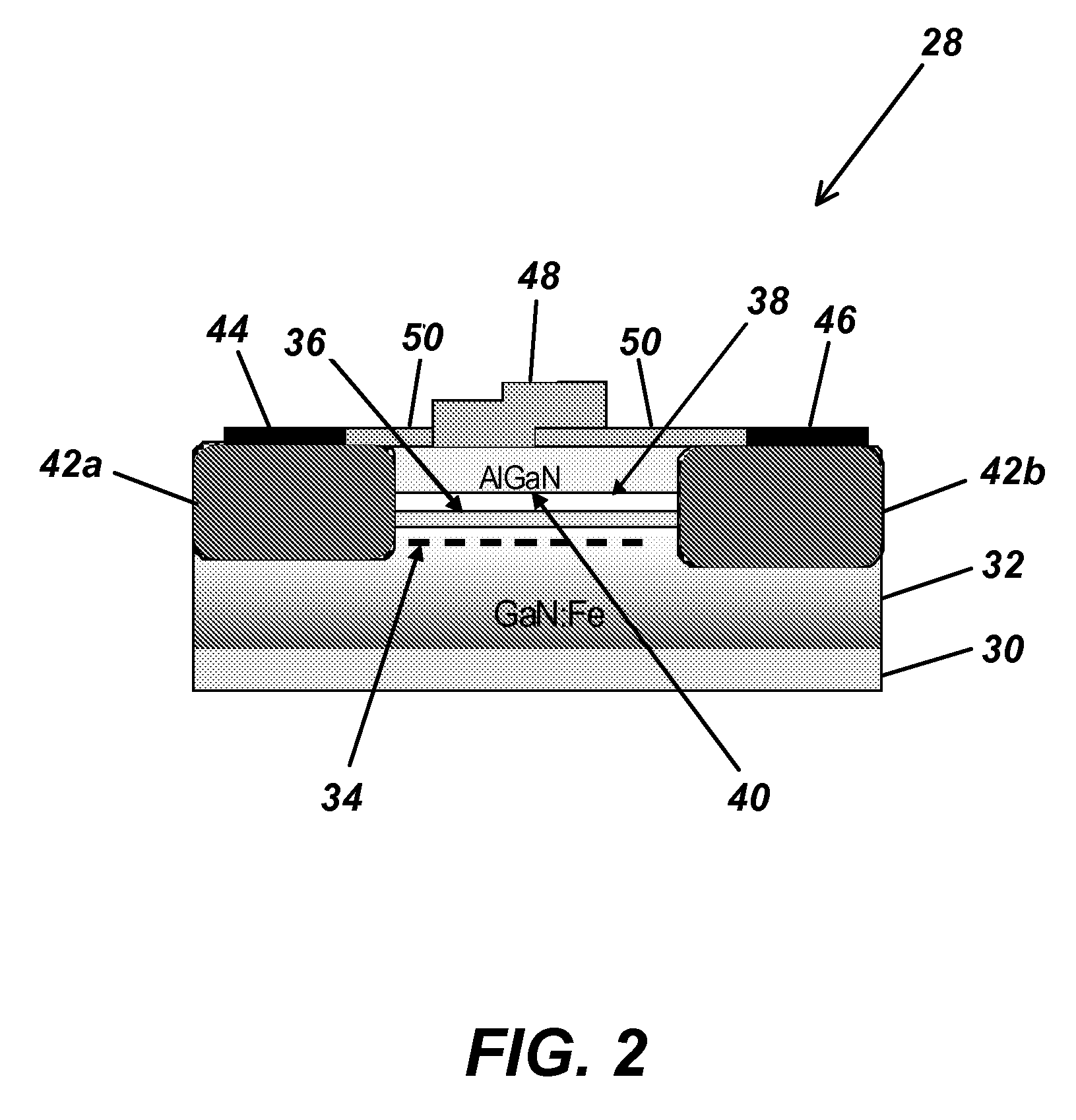

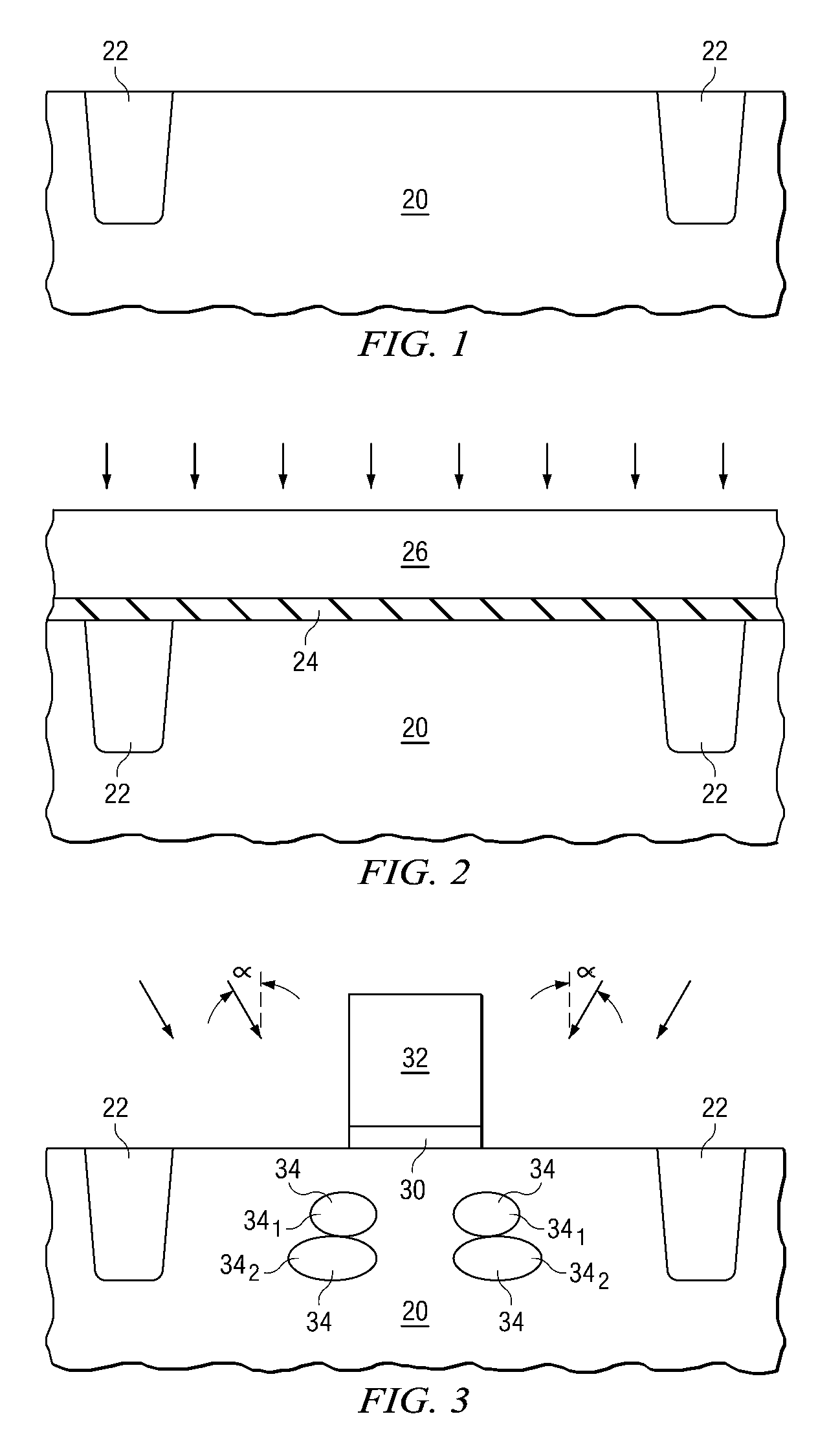

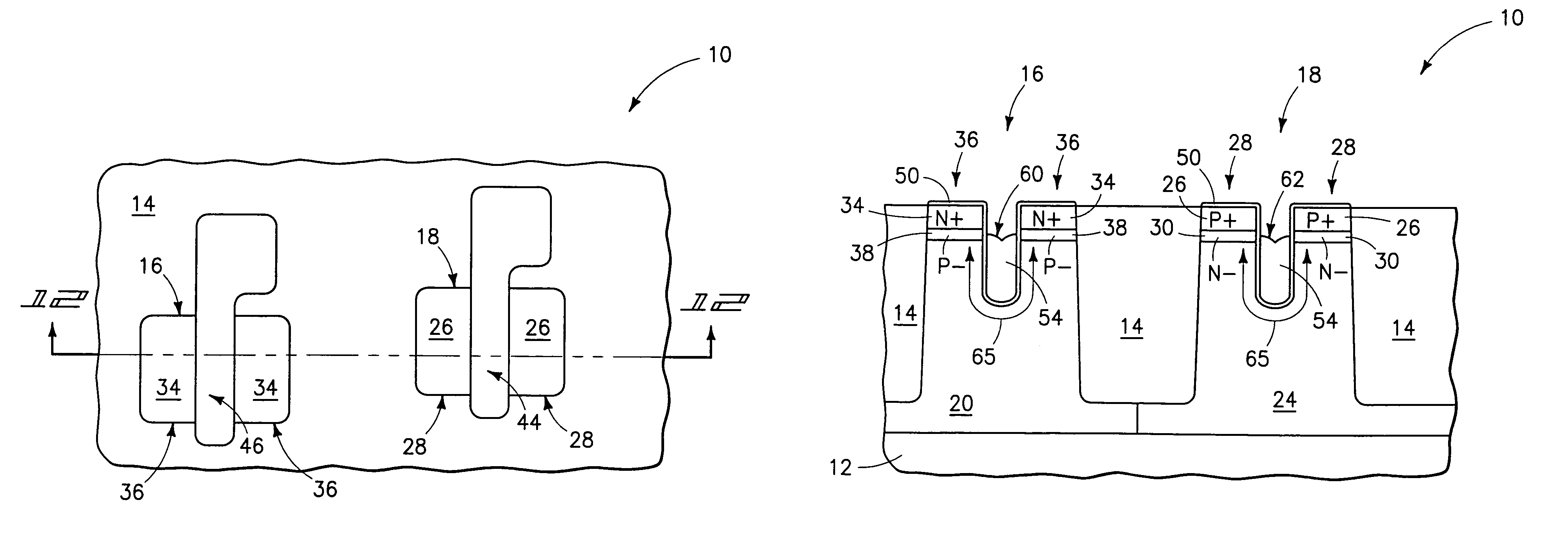

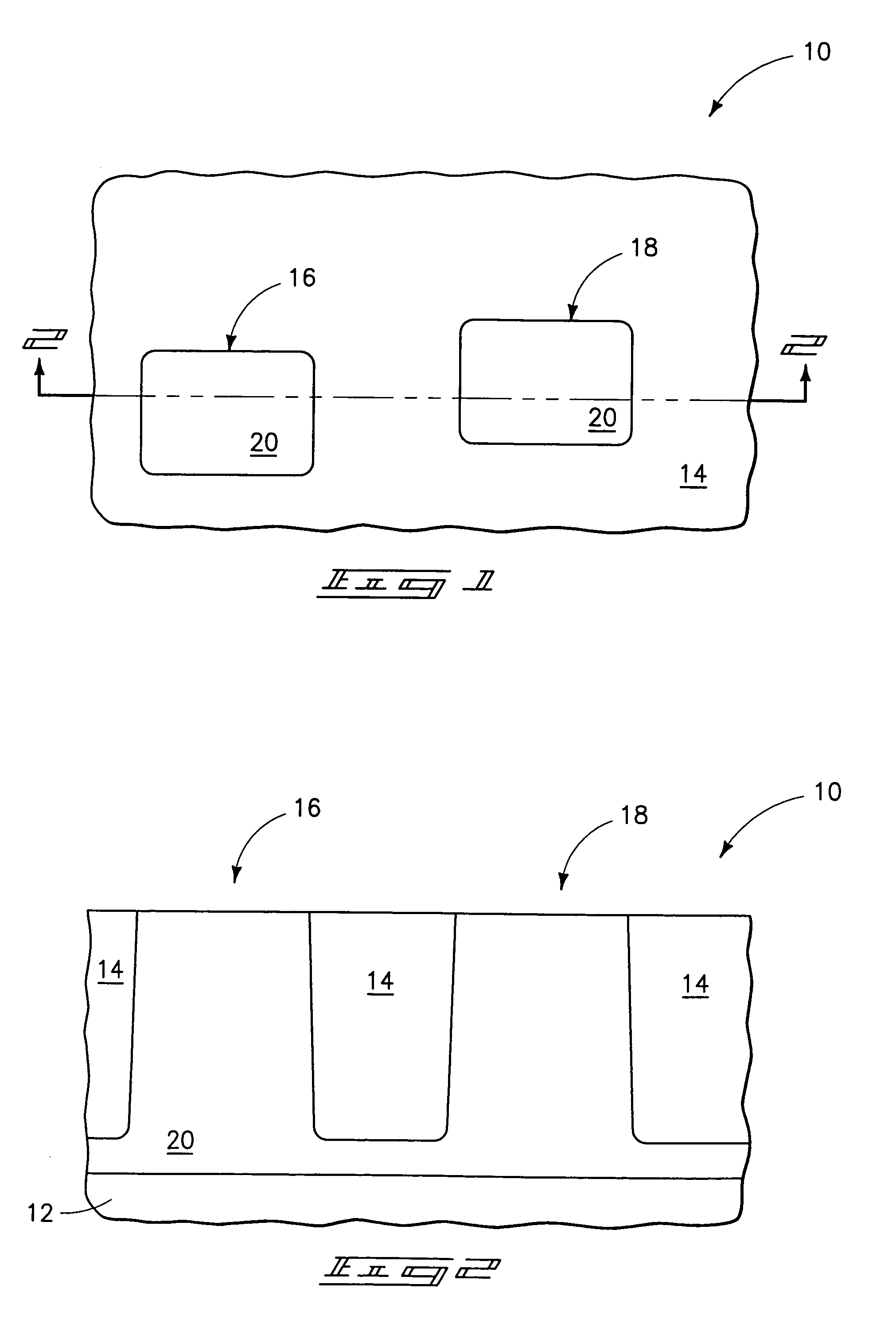

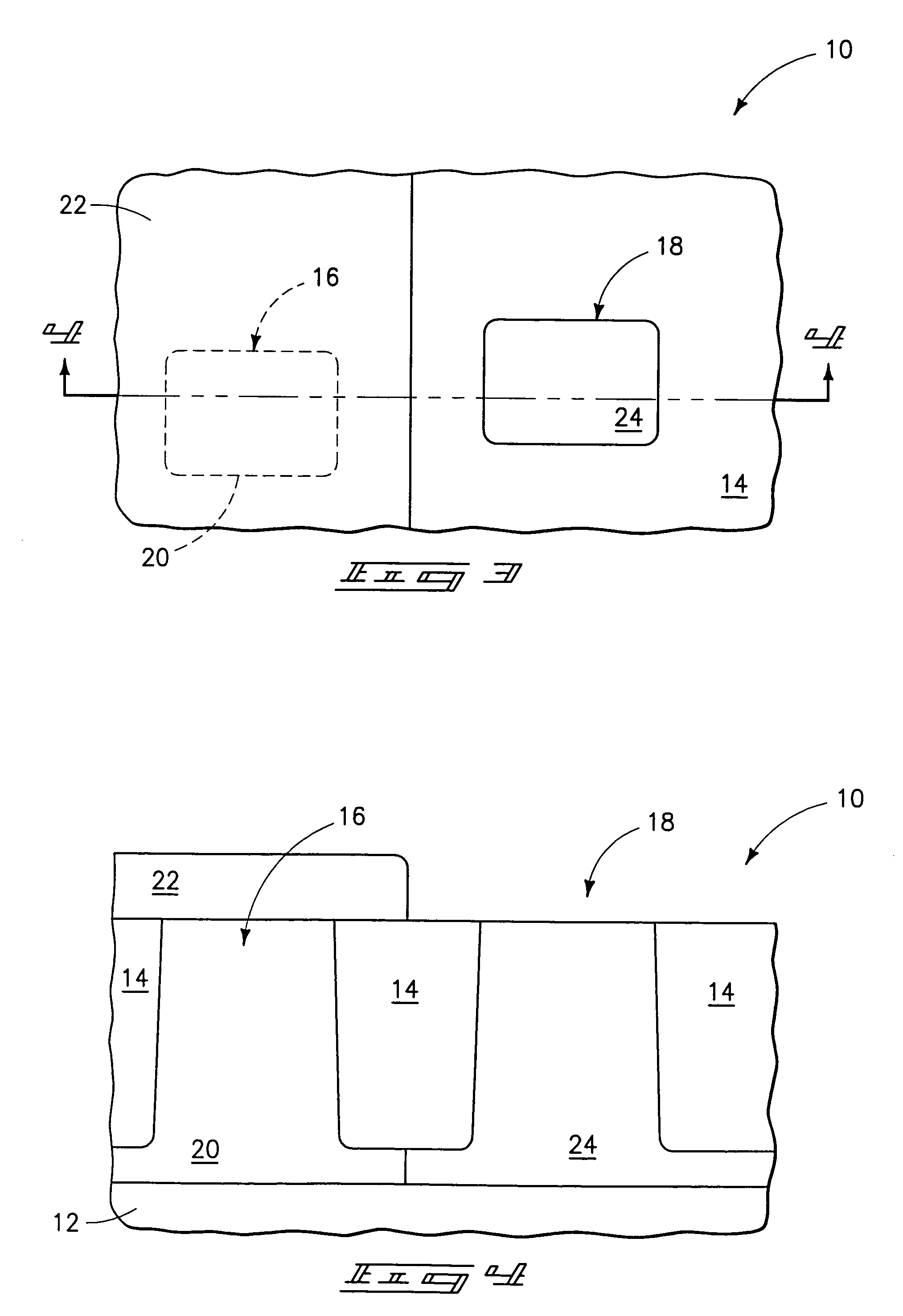

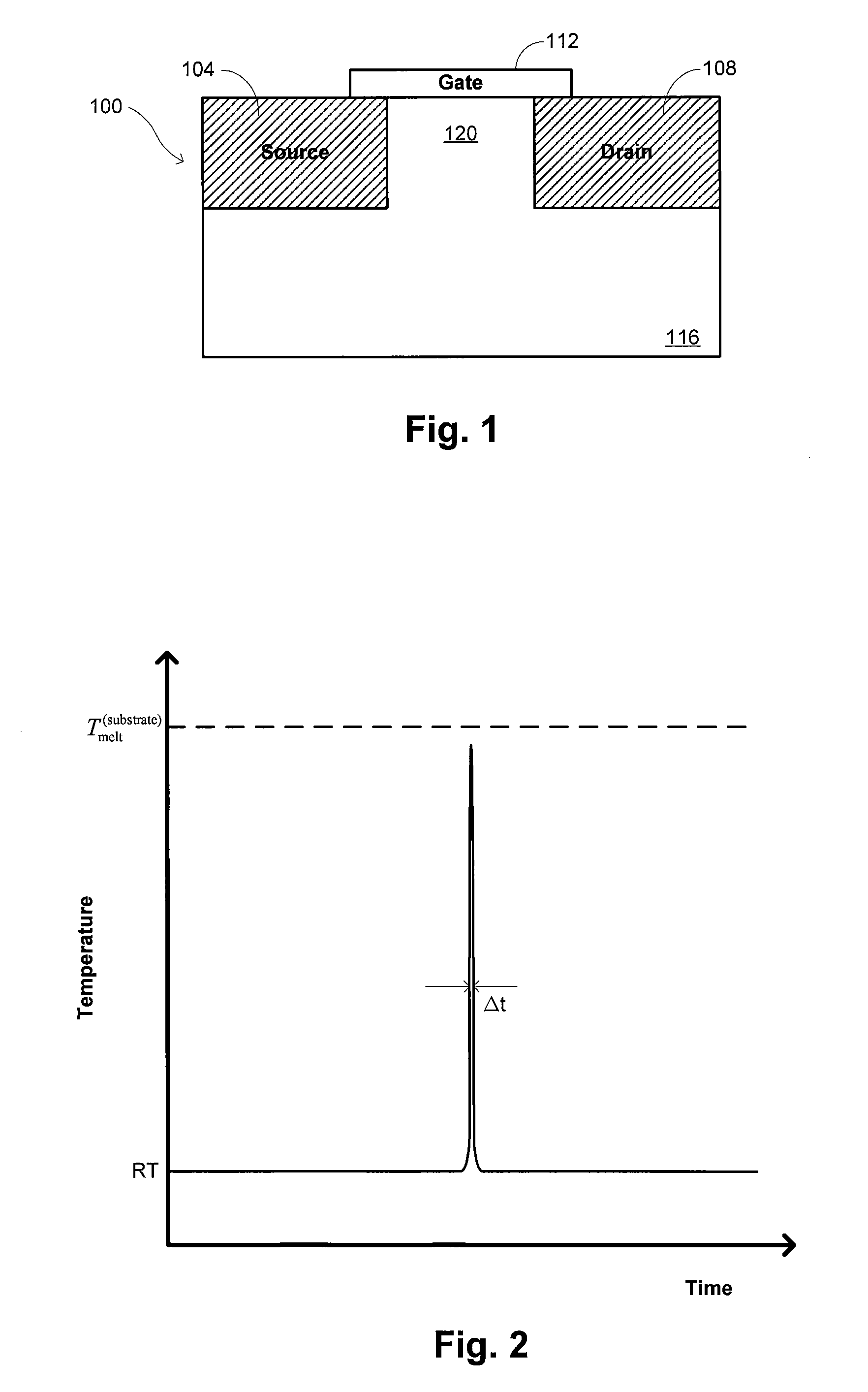

Methods of forming field effect transistors on substrates

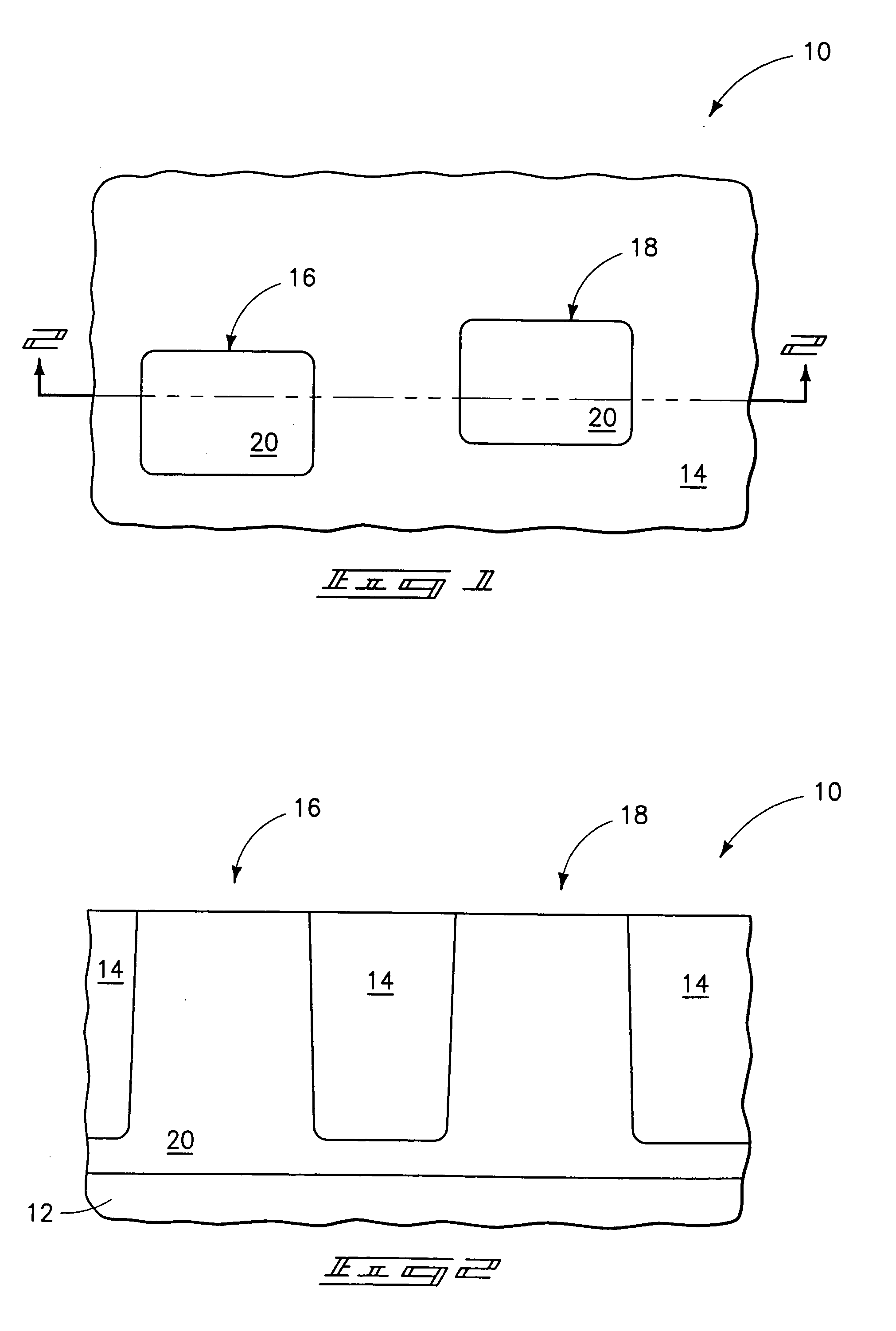

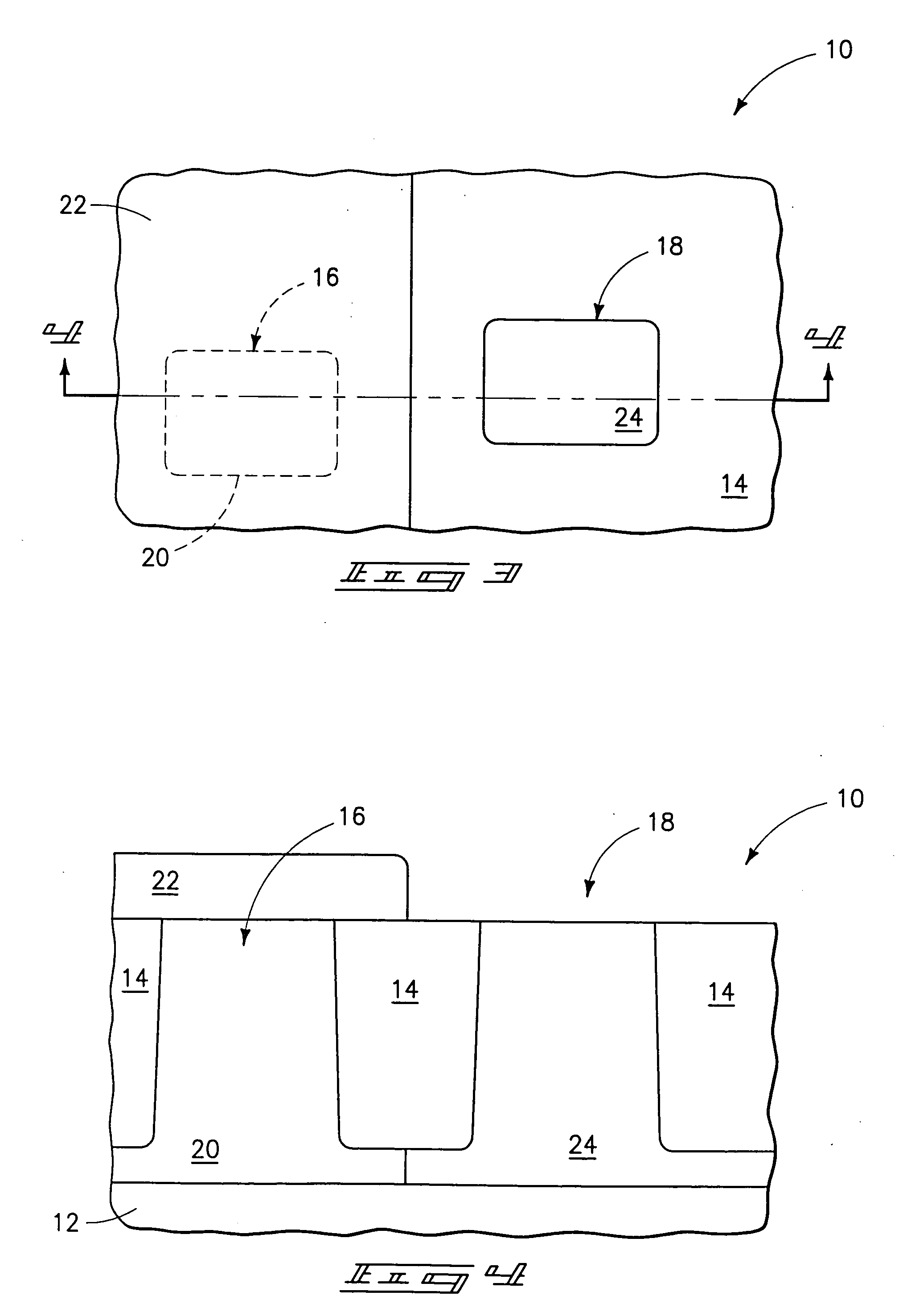

InactiveUS20070048942A1TransistorSemiconductor/solid-state device manufacturingField-effect transistorDopant Activation

The invention includes methods of forming field effect transistors. In one implementation, the invention encompasses a method of forming a field effect transistor on a substrate, where the field effect transistor comprises a pair of conductively doped source / drain regions, a channel region received intermediate the pair of source / drain regions, and a transistor gate received operably proximate the channel region. Such implementation includes conducting a dopant activation anneal of the pair of source / drain regions prior to depositing material from which a conductive portion of the transistor gate is made. Other aspects and implementations are contemplated.

Owner:MICRON TECH INC

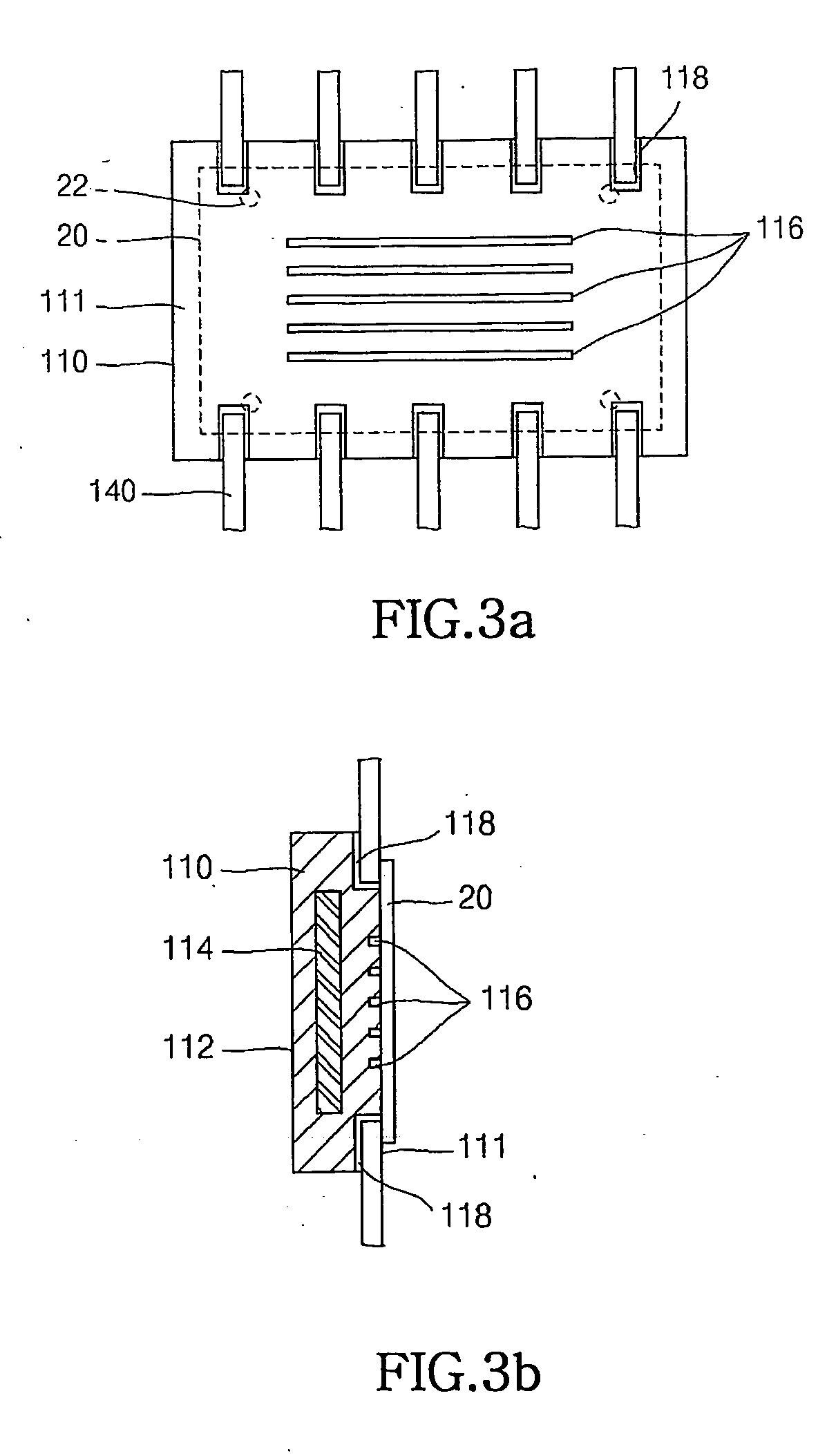

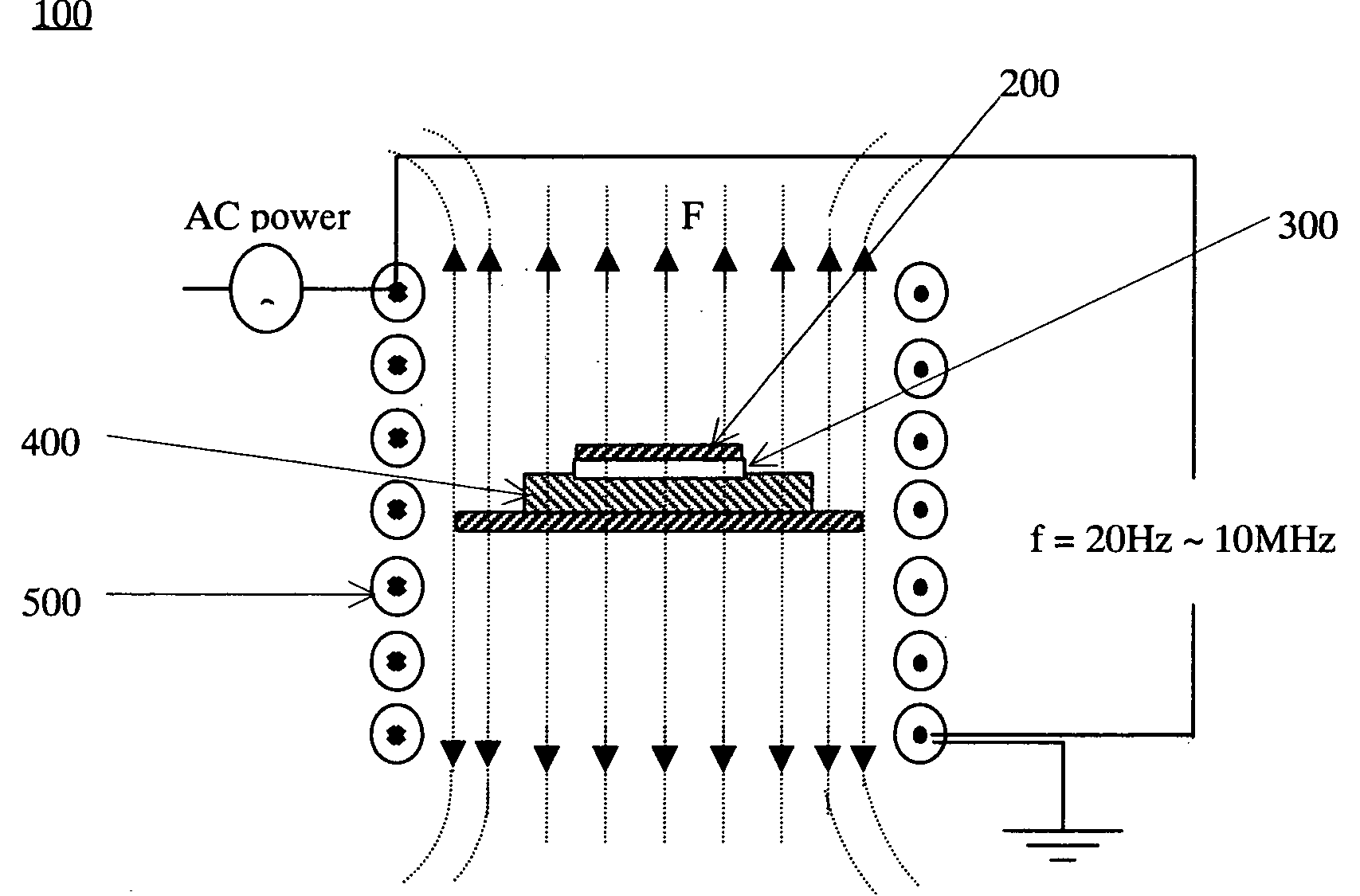

System for heat treatment of semiconductor device

InactiveUS20070122936A1Avoid damageIncrease temperatureFurnaces without endless coreSemiconductor/solid-state device manufacturingDevice materialElectromotive force

Disclosed is a heat treatment system for semiconductor devices. The heat treatment system is used in a heat treatment process for semiconductor devices, such as a crystallization process for an amorphous silicon thin film or a dopant activation process for a poly-crystalline silicon thin film formed on a surface of a glass substrate of a flat display panel including a liquid crystal display (LCD) or an organic light emitting device (OLED). The heat treatment system transfers a semiconductor device after uniformly preheating the semiconductor device in order to prevent deformation of the semiconductor device during the heat treatment process, rapidly performs the heat treatment process under the high temperature condition by heating the semiconductor device using a lamp heater and induction heat derived from induced electromotive force, and unloads the semiconductor device after uniformly cooling the semiconductor device such that the semiconductor device is prevented from being deformed when the heat treatment process has been finished. The heat treatment system rapidly performs the heat treatment process while preventing deformation of the semiconductor device by gradually heating or cooling the semiconductor device.

Owner:VIATRON TECH INC

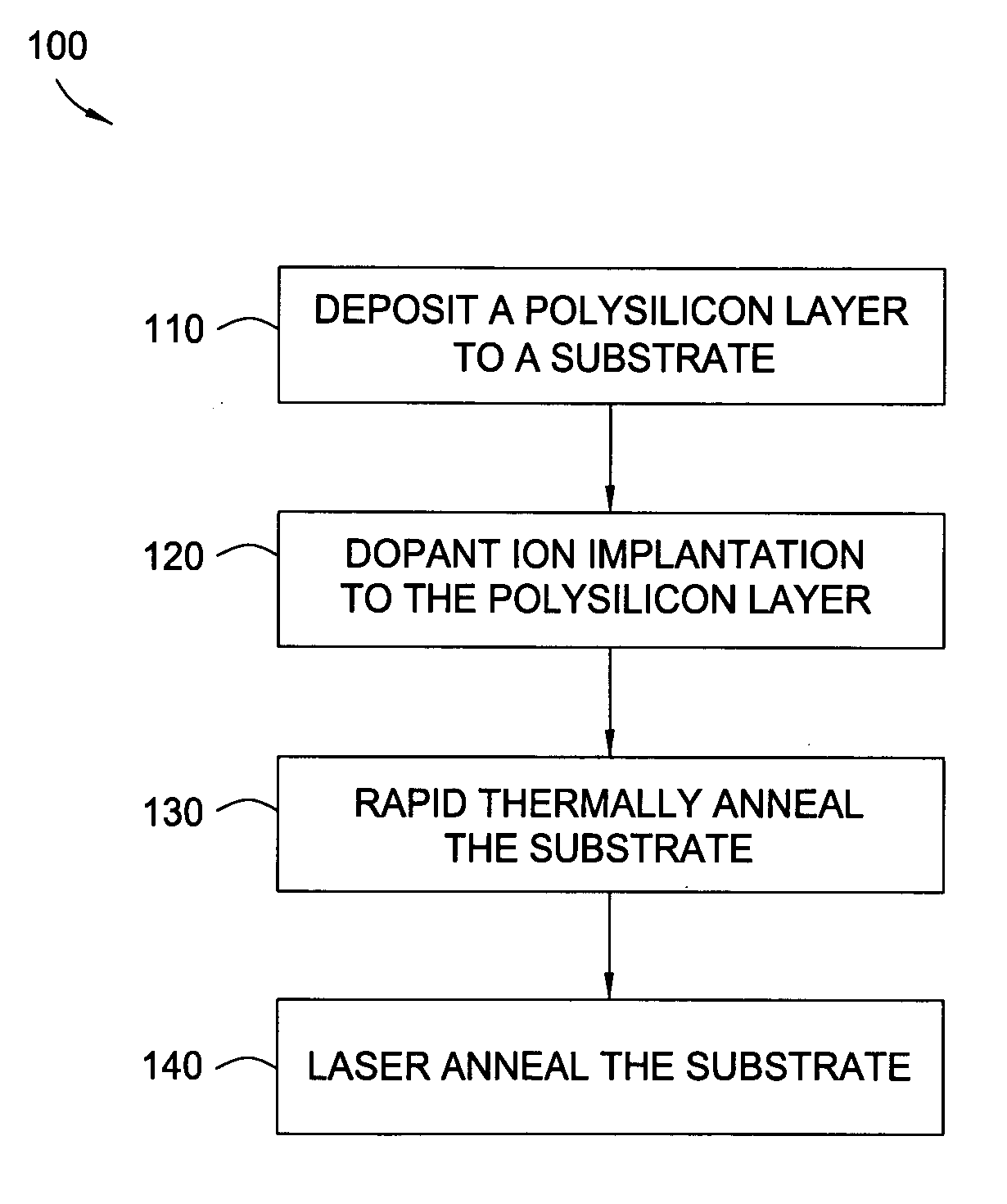

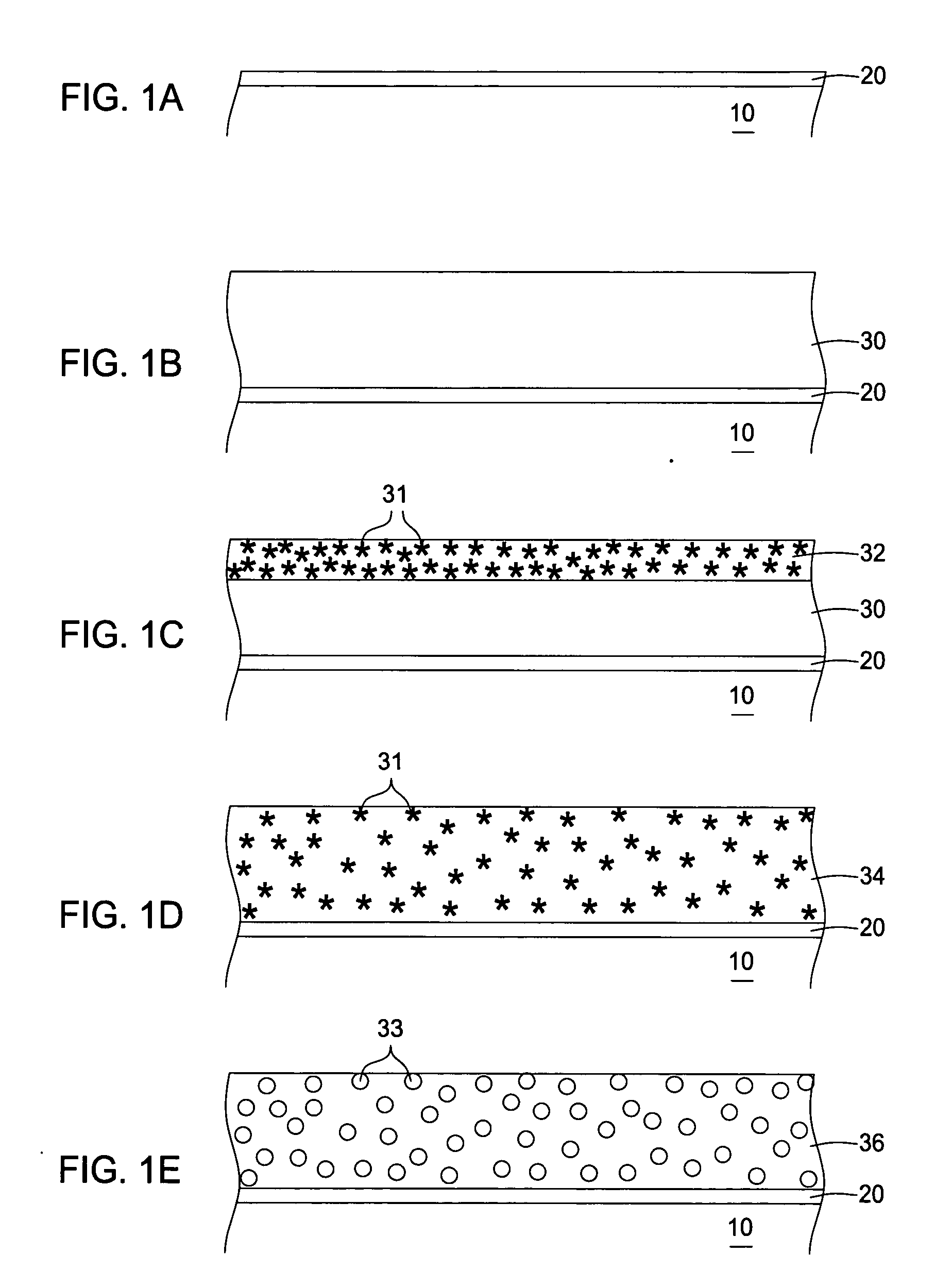

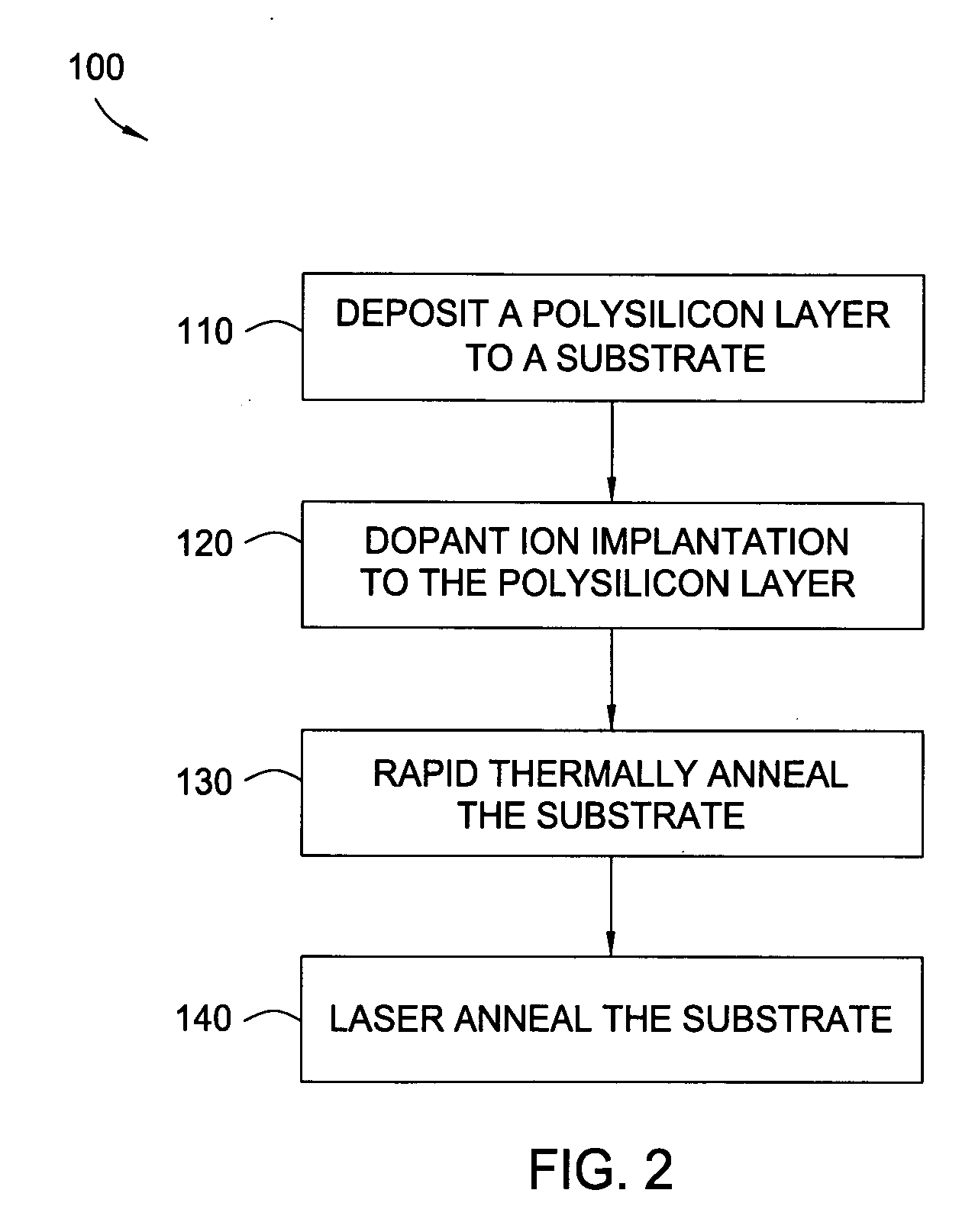

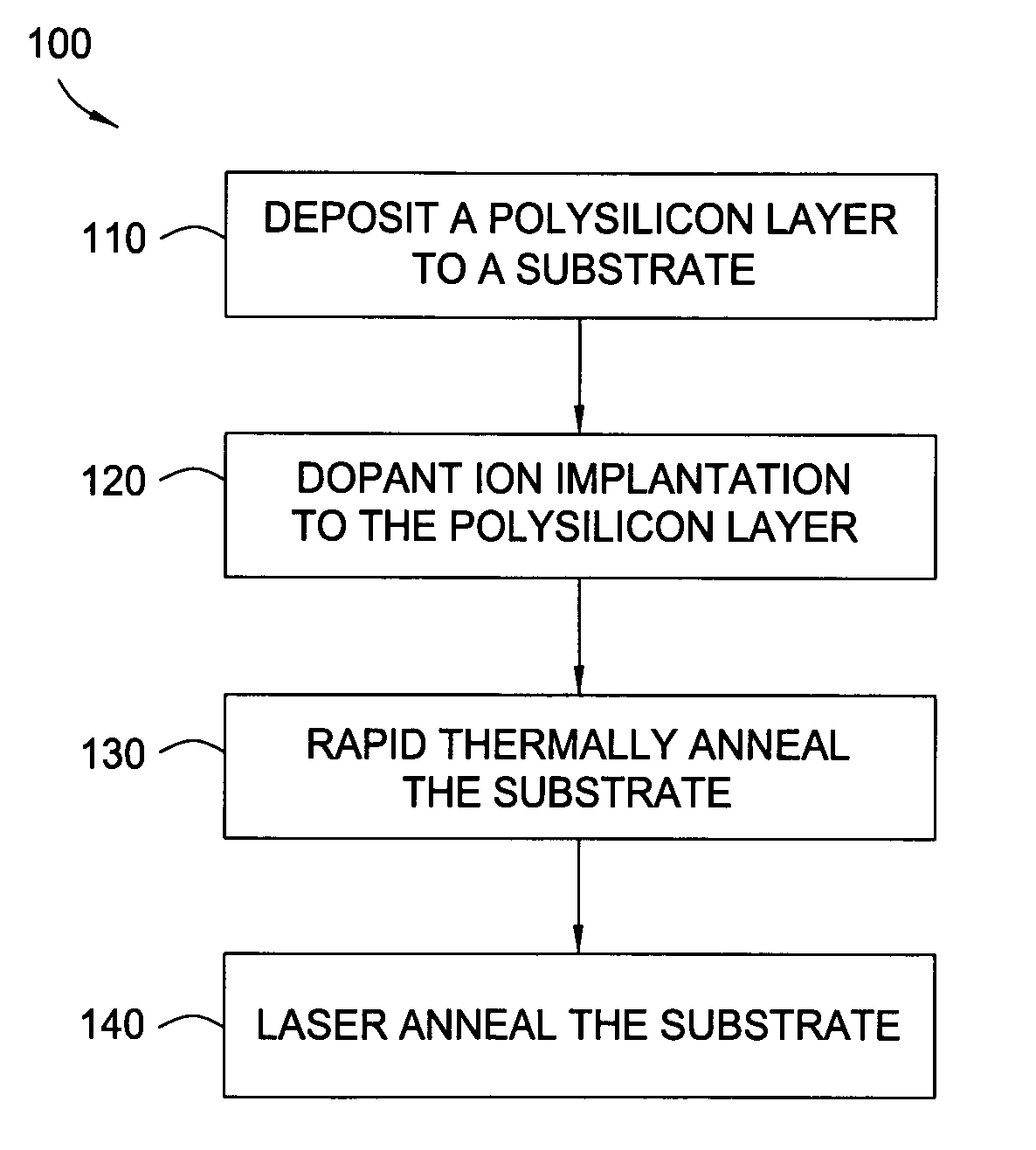

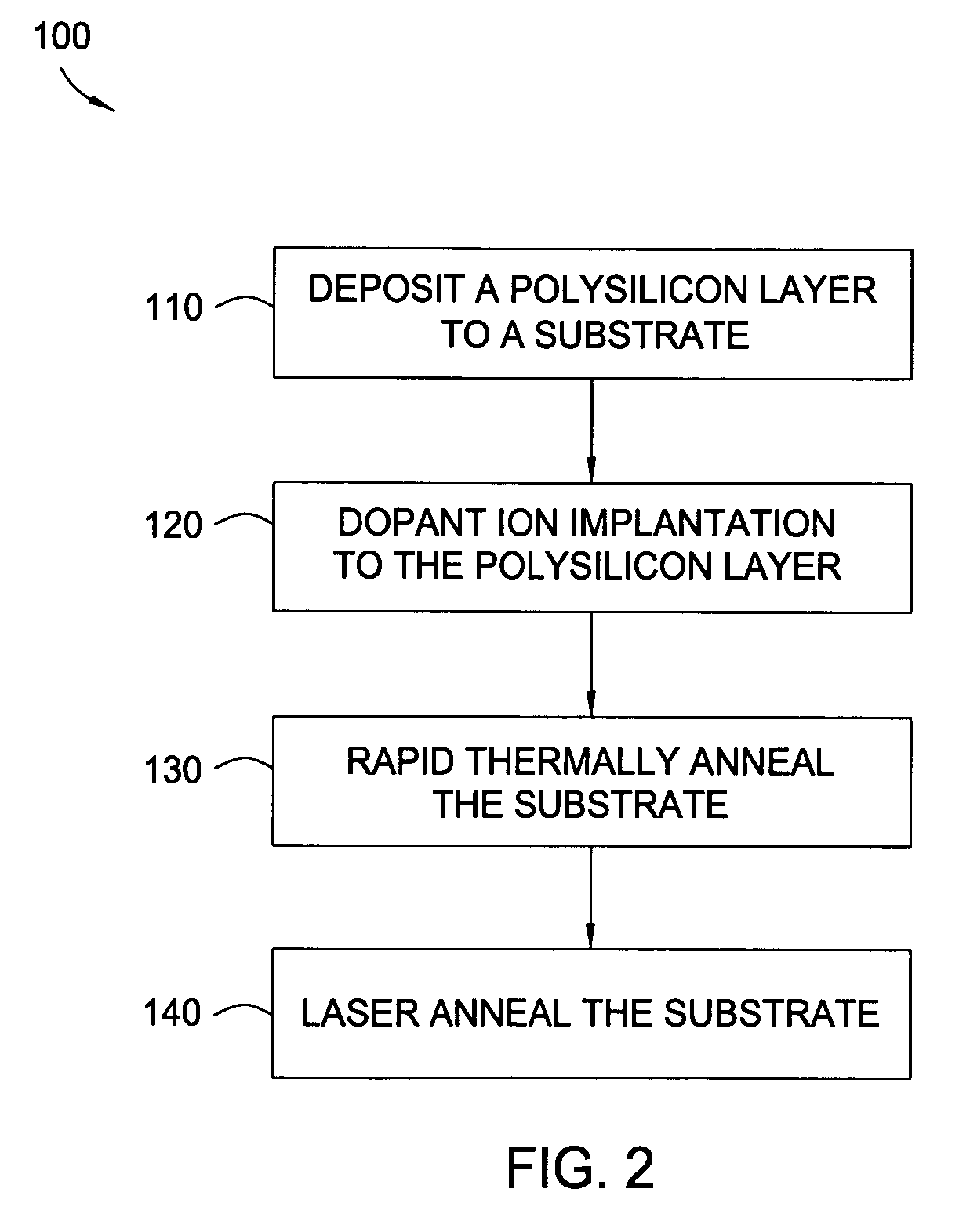

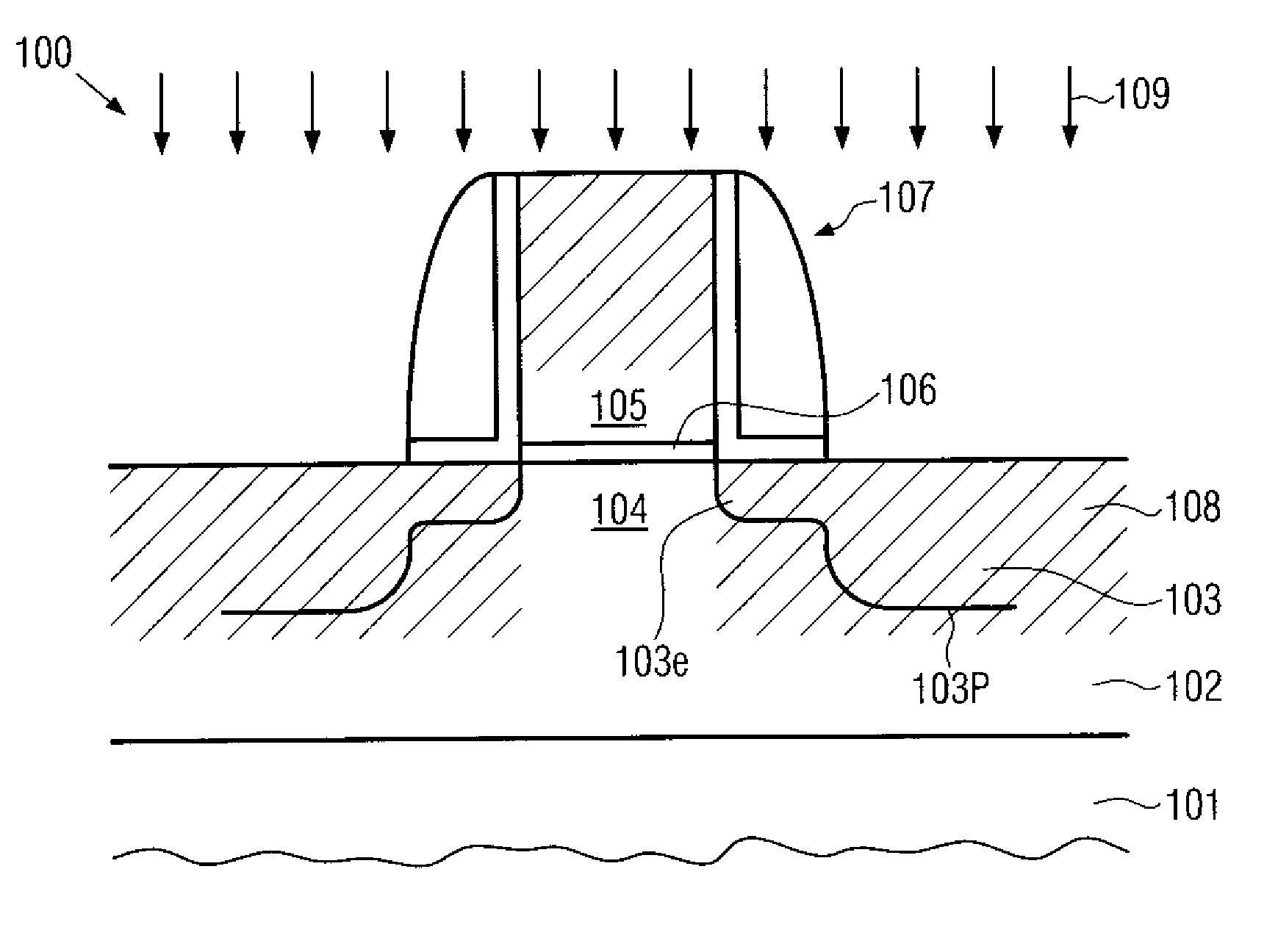

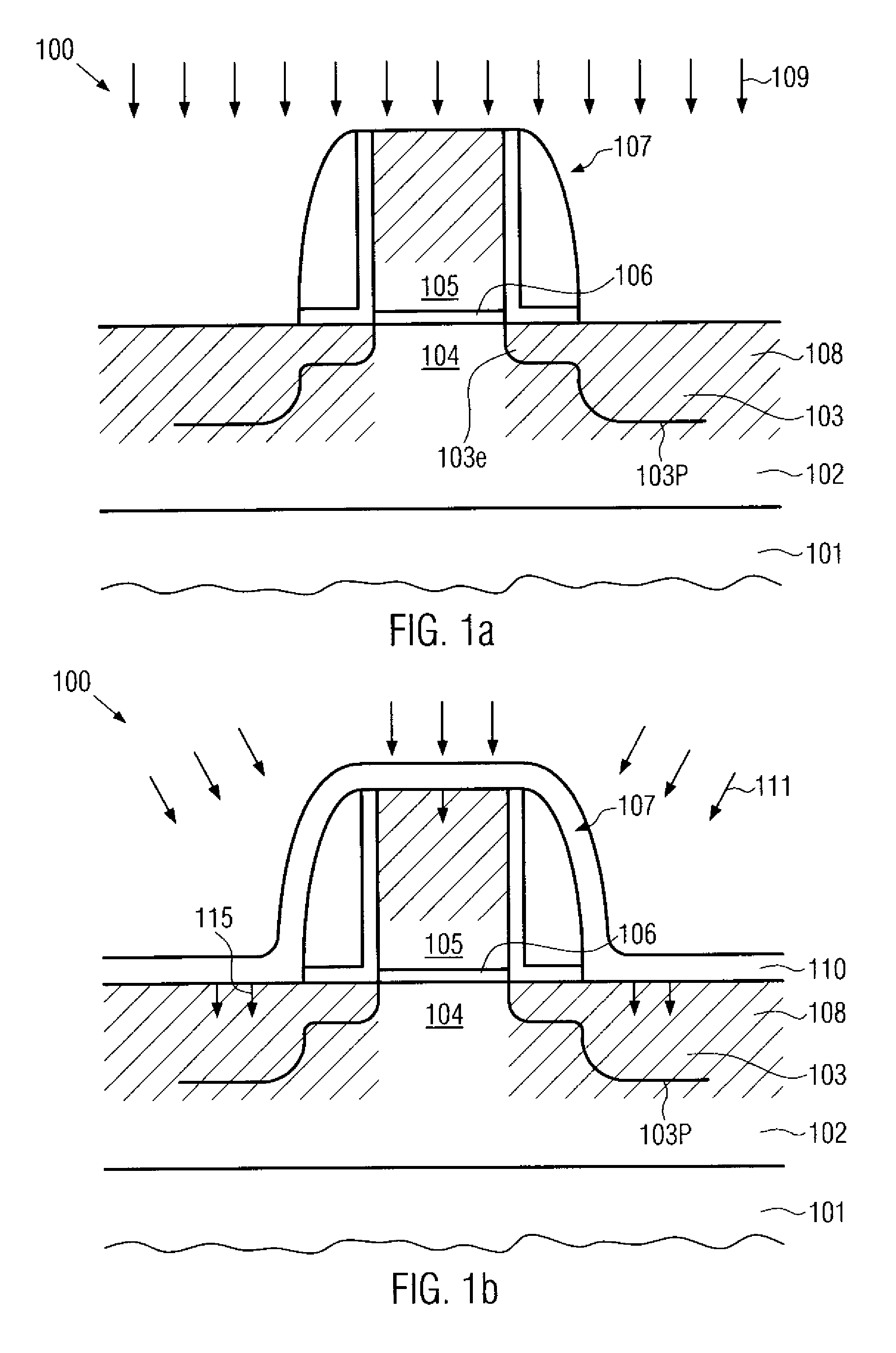

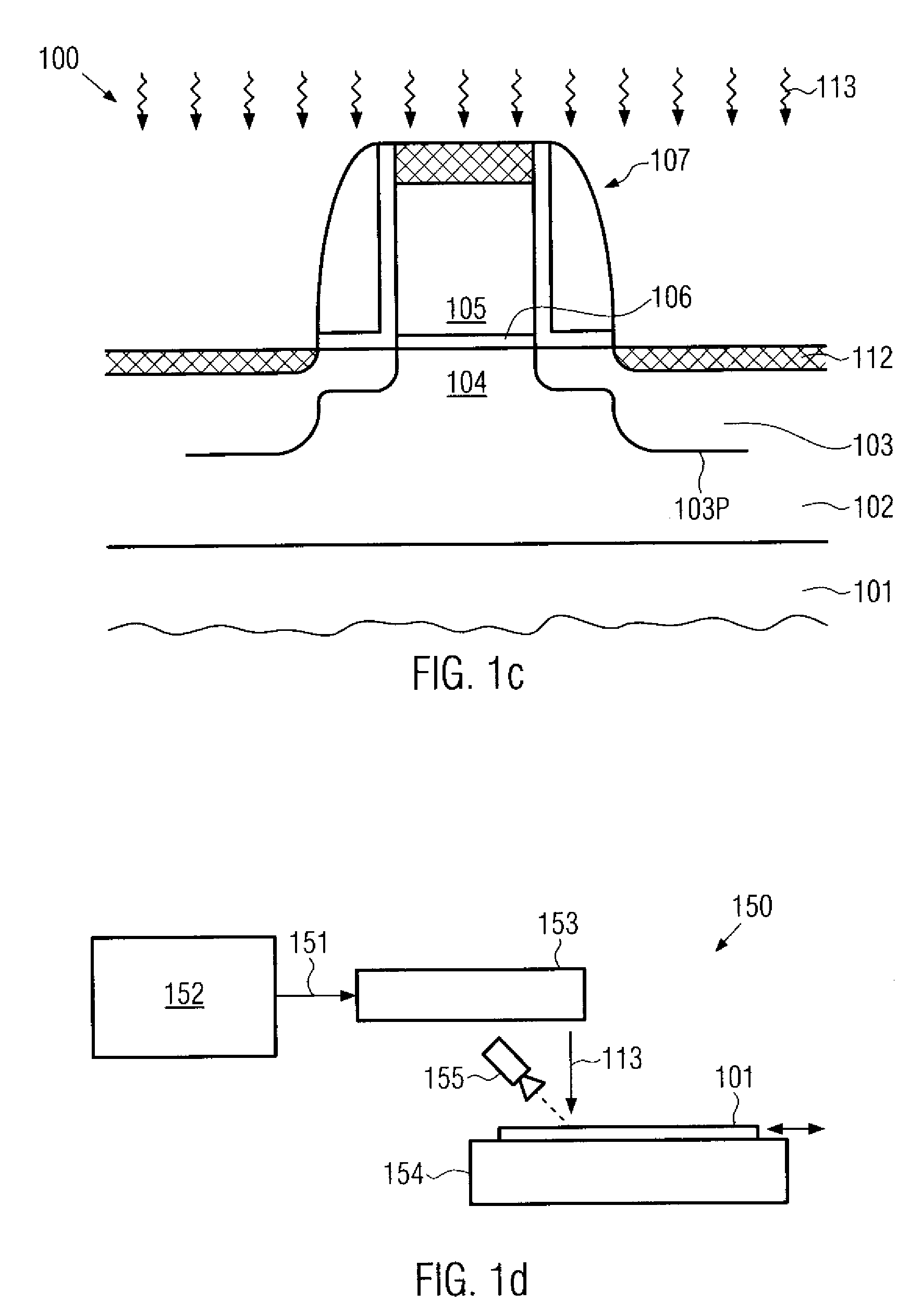

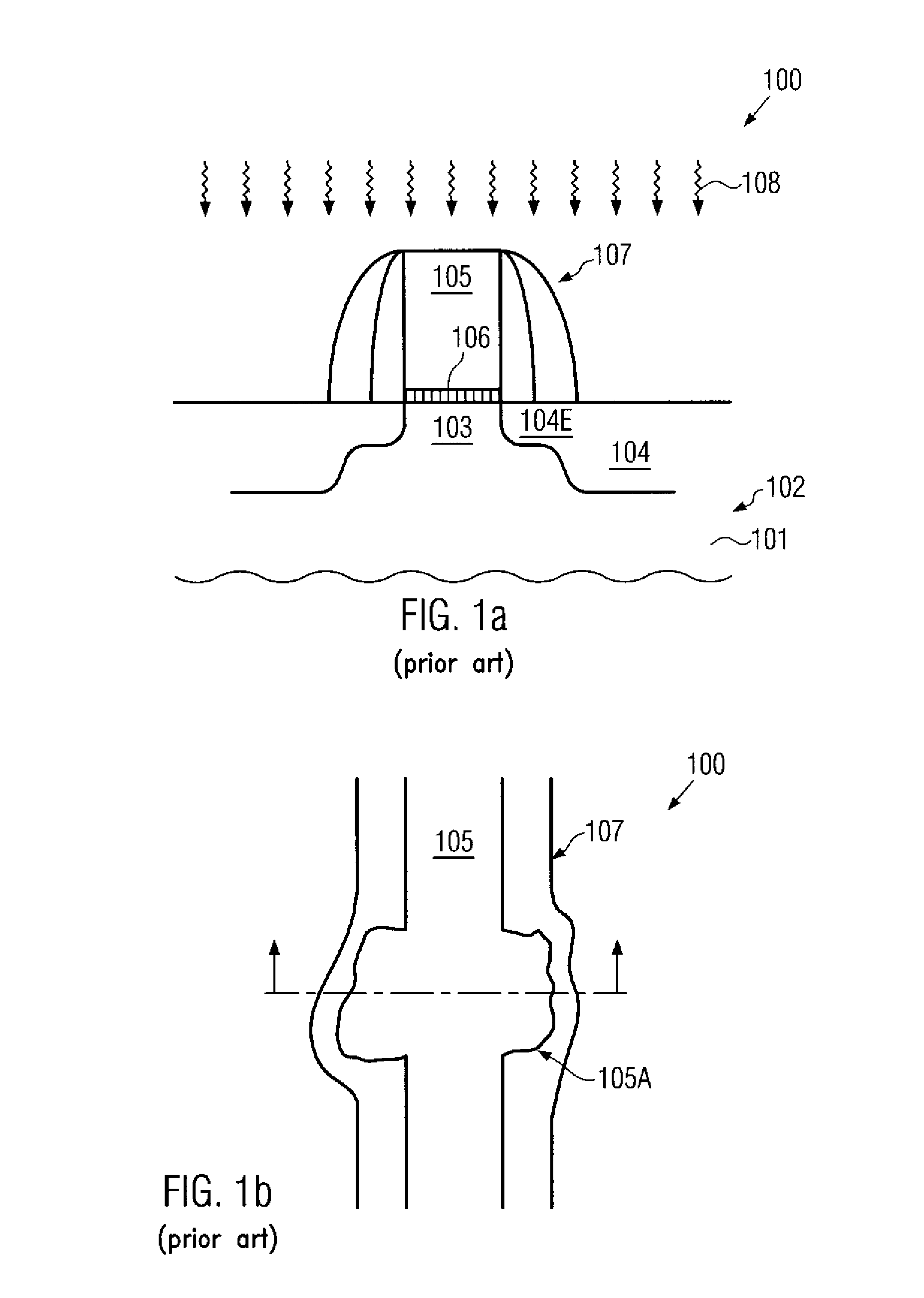

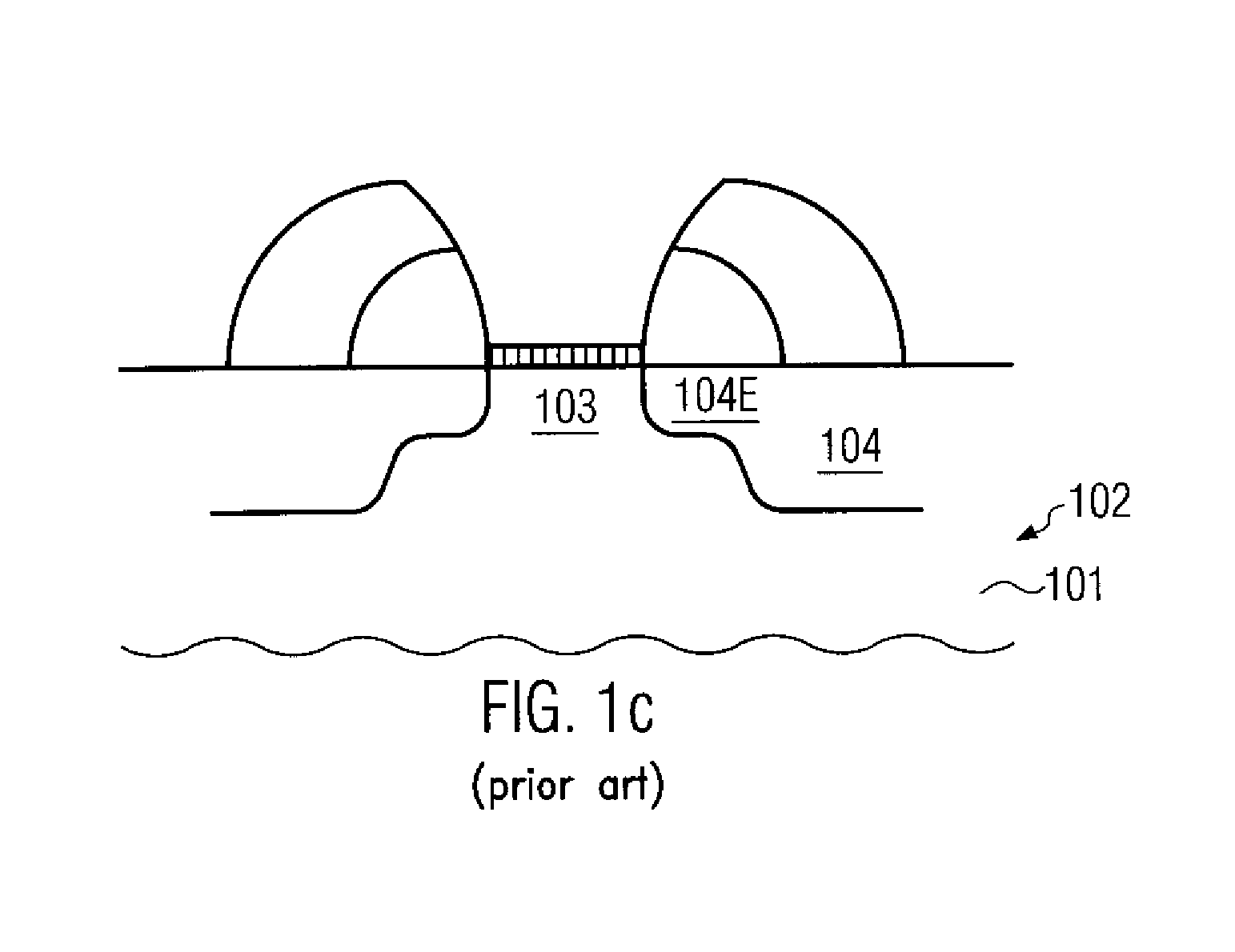

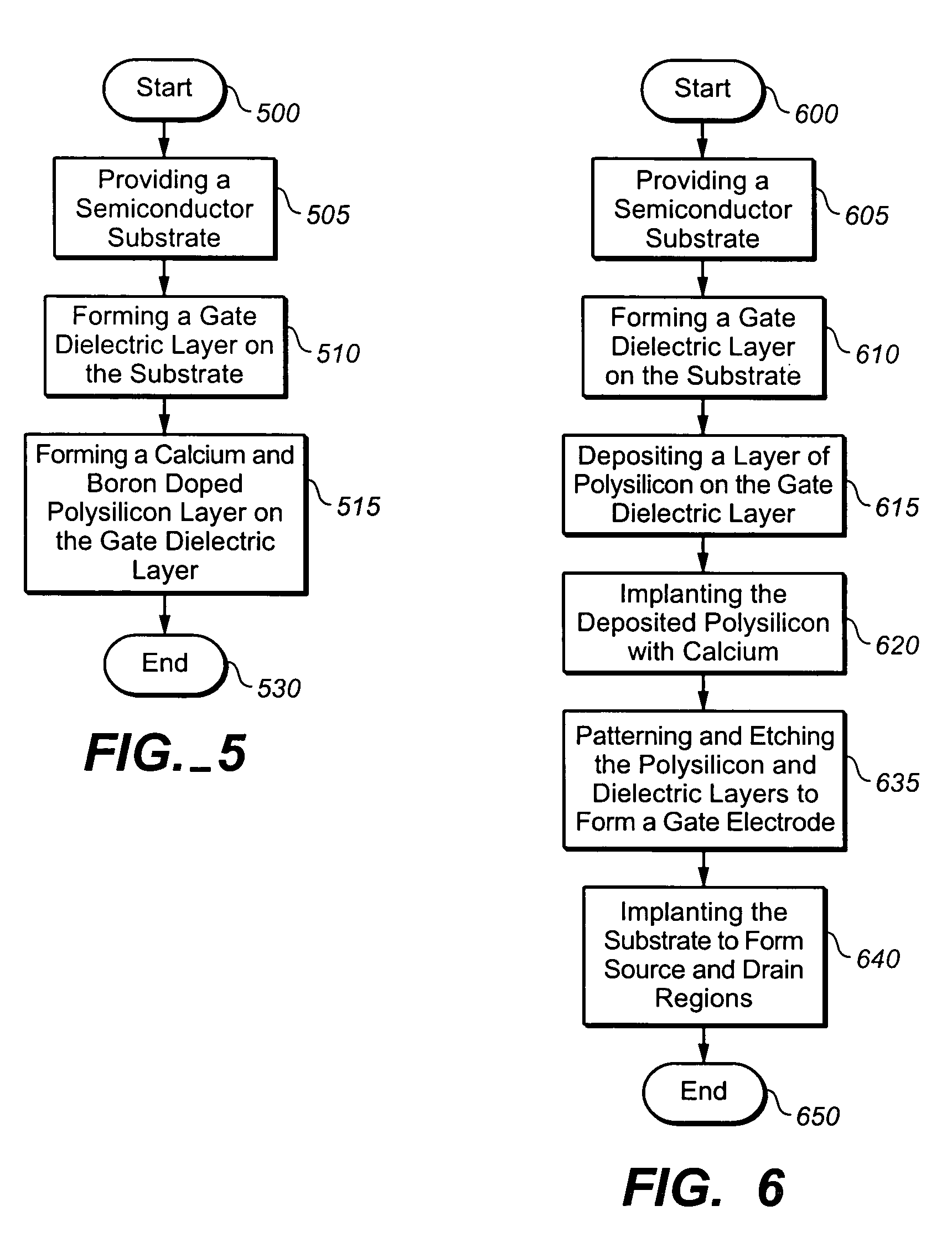

Gate electrode dopant activation method for semiconductor manufacturing

ActiveUS20050186765A1From solid stateSemiconductor/solid-state device manufacturingLaser annealingDopant Activation

In one embodiment, the invention generally provides a method for annealing a doped layer on a substrate including depositing a polycrystalline layer to a gate oxide layer and implanting the polycrystalline layer with a dopant to form a doped polycrystalline layer. The method further includes exposing the doped polycrystalline layer to a rapid thermal anneal to readily distribute the dopant throughout the polycrystalline layer. Subsequently, the method includes exposing the doped polycrystalline layer to a laser anneal to activate the dopant in an upper portion of the polycrystalline layer.

Owner:APPLIED MATERIALS INC

Methods and apparatuses for heat treatment of semiconductor films upon thermally susceptible non-conducting substrates

InactiveUS20030010775A1Improve uniformityMaximize goalFurnaces without endless coreTransistorEngineeringSolar cell

The present invention relates to methods and apparatuses for heat treatment of semiconductor films upon thermally susceptible non-conducting substrates at a minimum thermal budget are required, and more particularly, to a polycrystalline silicon thin-film transistors (poly-Si TFTs) and PN diodes on glass substrates for various applications of liquid crystal displays (LCDs), organic light emitting diodes (OLEDs), and solar cells. According to the methods and apparatus of the present invention, the semiconductor films can be heat-treated without damaging the thermally susceptible substrates; e.g., crystallization of amorphous silicon films at the minimum thermal budget acceptable for the use of glass, enhancing kinetics of dopant activation at the minimum thermal budget acceptable for the use of glass.

Owner:KIM HYOUNG JUNE

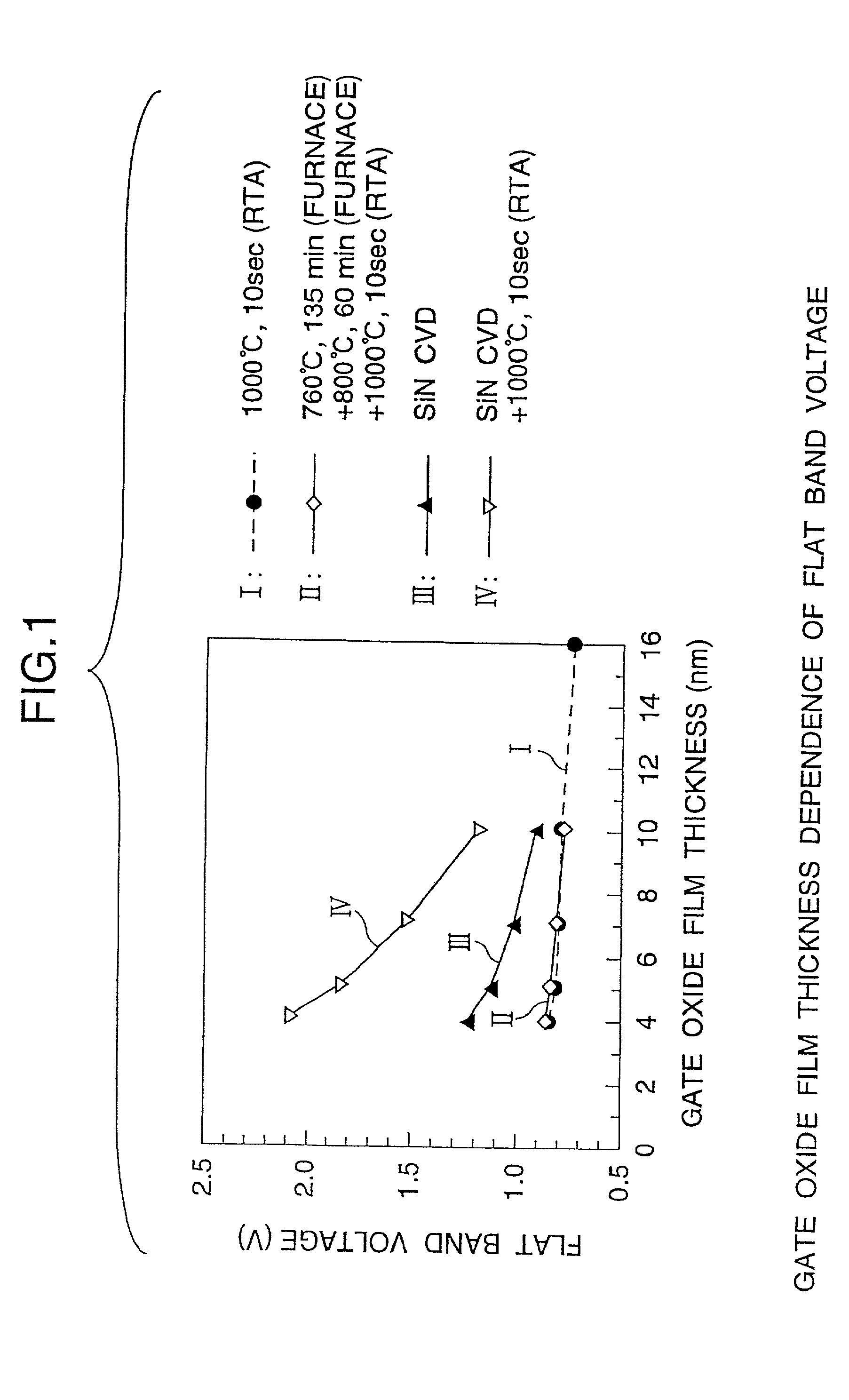

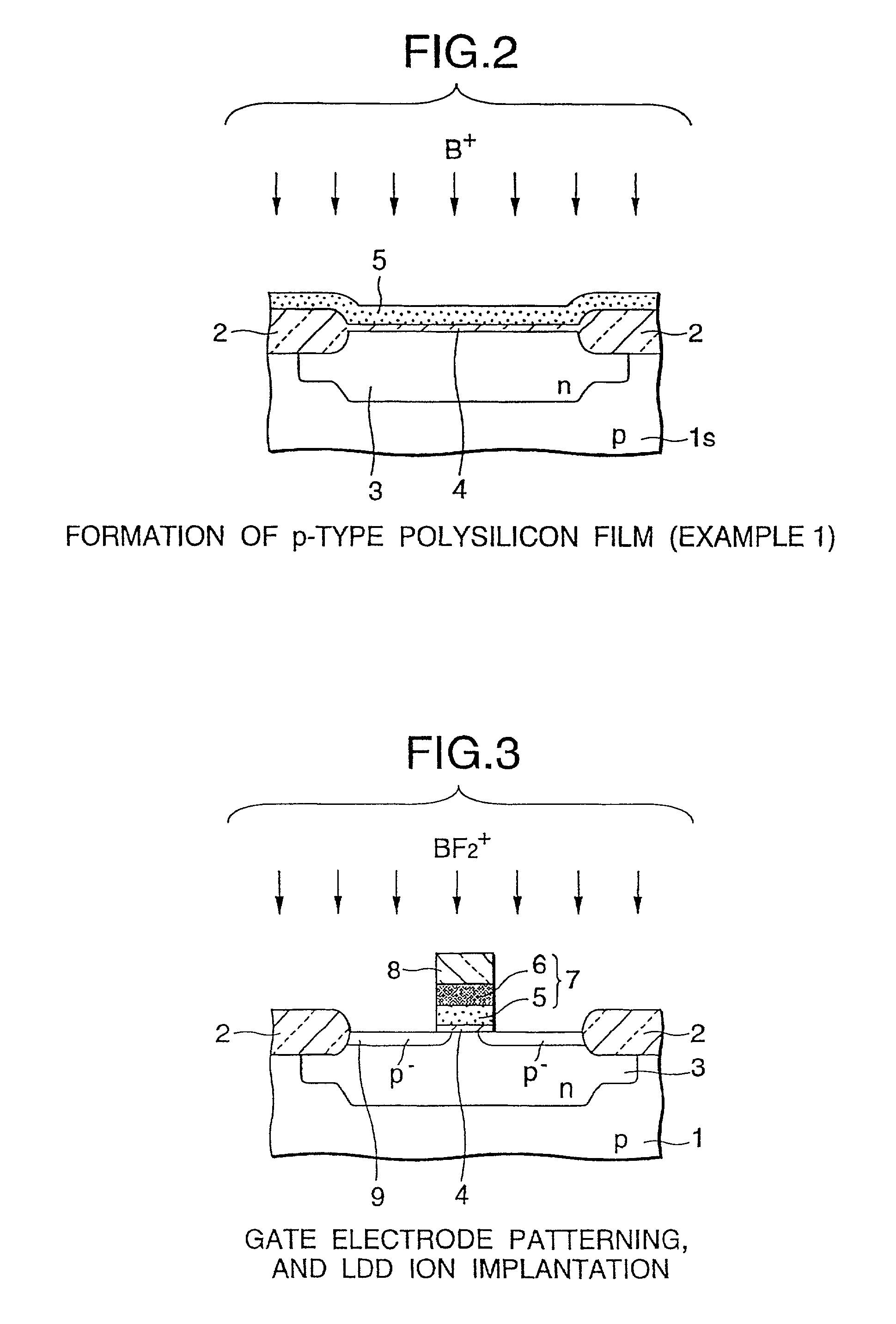

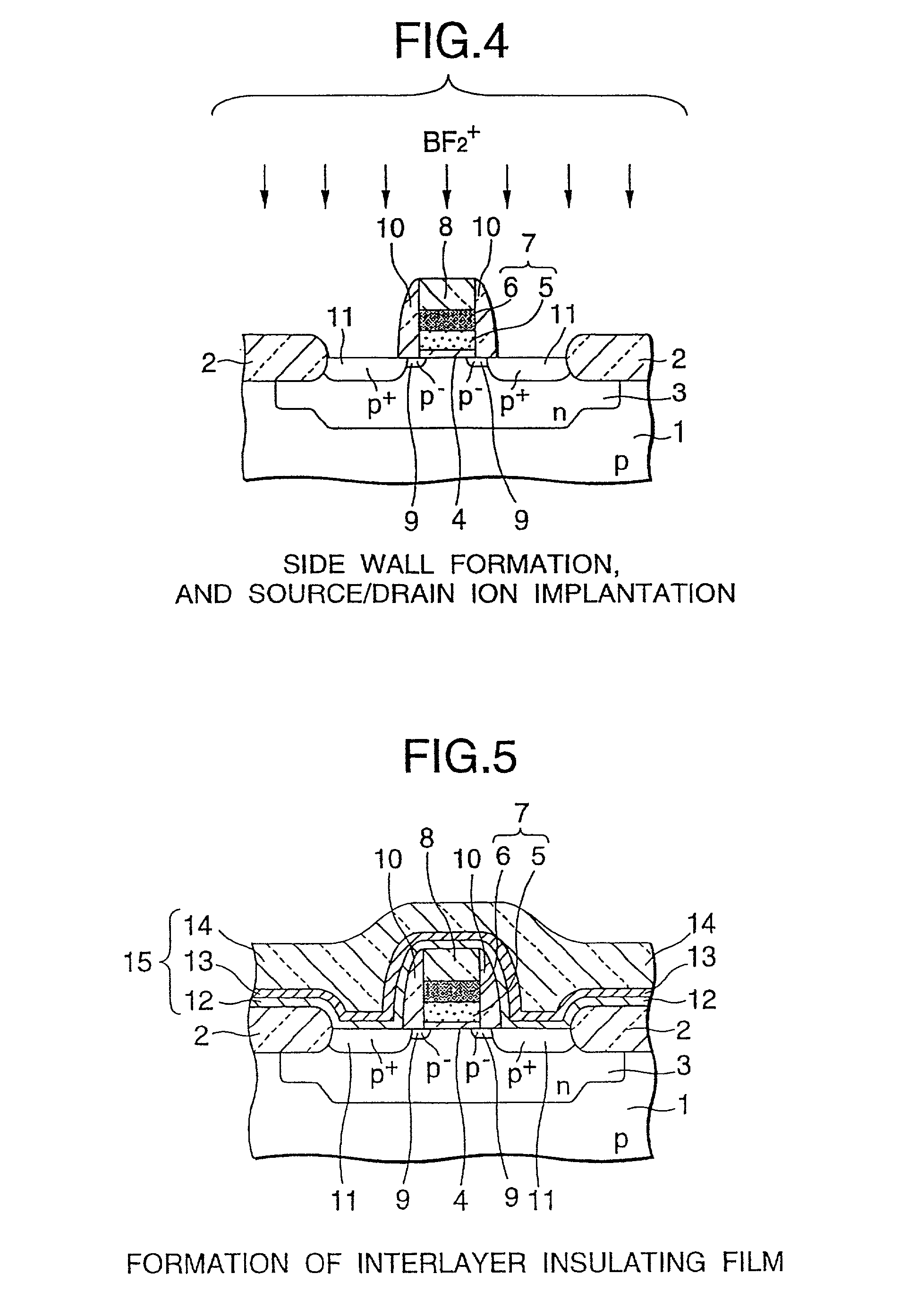

Method for fabricating mos transistors

InactiveUS20010012653A1Inhibited DiffusionTransistorSemiconductor/solid-state device manufacturingHydrogenPunching

In PMOS having a gate electrode 7 of a p-type polysilicon film 5 along with a silicon nitride film 13, boron diffusion from the p-type polysilicon film 5 and boron punching through the gate oxide film 4 are prevented, thereby stabilizing the properties of the PMOS. Hydrogen existing in the silicon nitride film 13 accelerates boron diffusion from the film 5. To prevent it, all subsequent steps after the step of forming the silicon nitride film 13 are effected within a temperature range within which the boron diffusion is not accelerated by hydrogen. Forming the silicon oxide film 14 through reduced pressure CVD is effected in a furnace at a temperature lower than 850.degree. C. Annealing for dopant activation in the compensation region 17 to be formed on the substrate in the bottom of the contact hole 16 is effected in a manner of RTA (rapid thermal annealing) at a temperature lower than 1000.degree. C.

Owner:SONY CORP

Gate electrode dopant activation method for semiconductor manufacturing including a laser anneal

ActiveUS7078302B2Semiconductor/solid-state device manufacturingSemiconductor devicesGate oxideDopant Activation

In one embodiment, the invention generally provides a method for annealing a doped layer on a substrate including depositing a polycrystalline layer to a gate oxide layer and implanting the polycrystalline layer with a dopant to form a doped polycrystalline layer. The method further includes exposing the doped polycrystalline layer to a rapid thermal anneal to readily distribute the dopant throughout the polycrystalline layer. Subsequently, the method includes exposing the doped polycrystalline layer to a laser anneal to activate the dopant in an upper portion of the polycrystalline layer.

Owner:APPLIED MATERIALS INC

Method of increasing transistor performance by dopant activation after silicidation

InactiveUS20070281472A1Improve transistor characteristicsReduce process complexityTransistorSemiconductor/solid-state device manufacturingSalicideMetal silicide

Owner:GLOBALFOUNDRIES INC

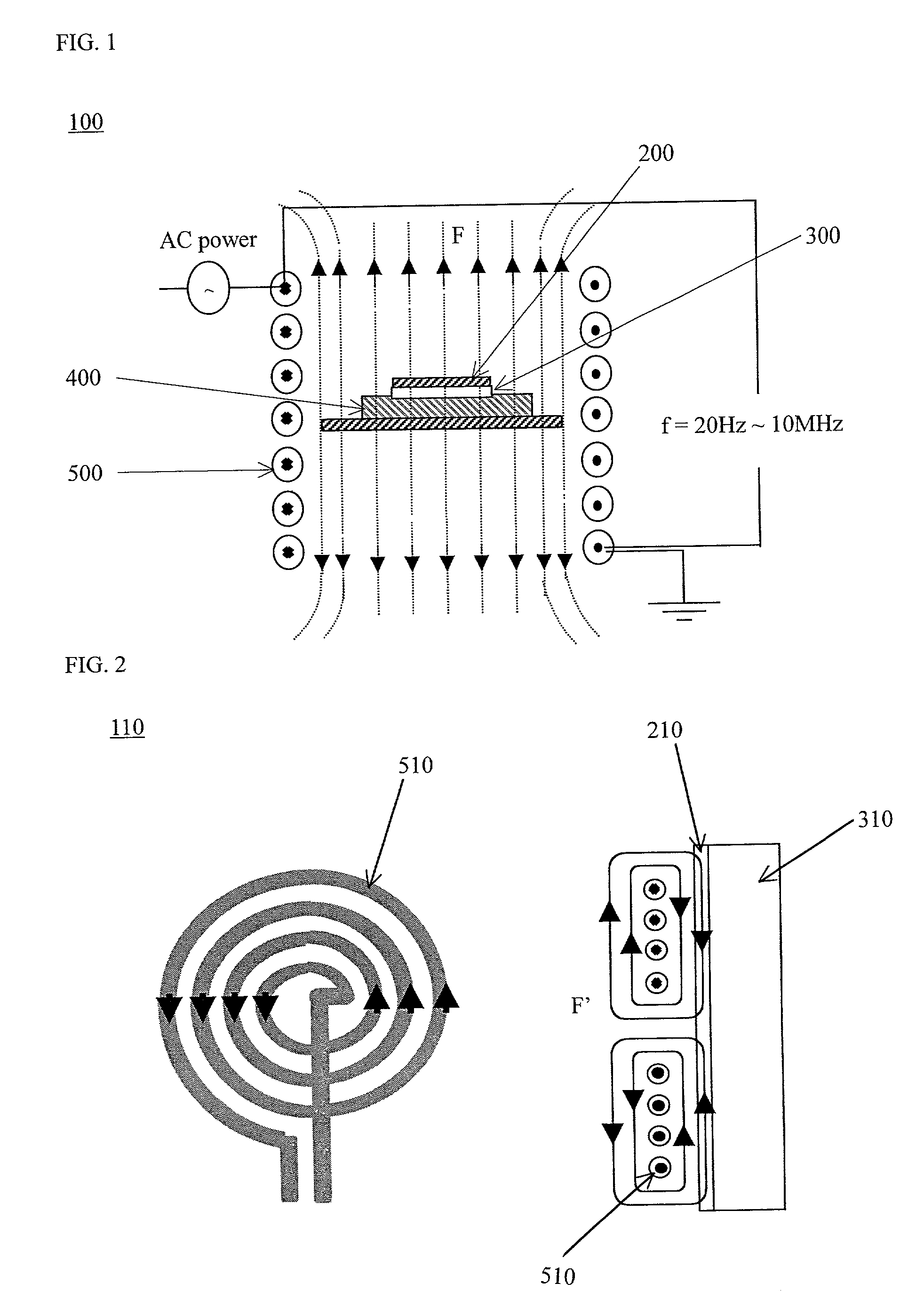

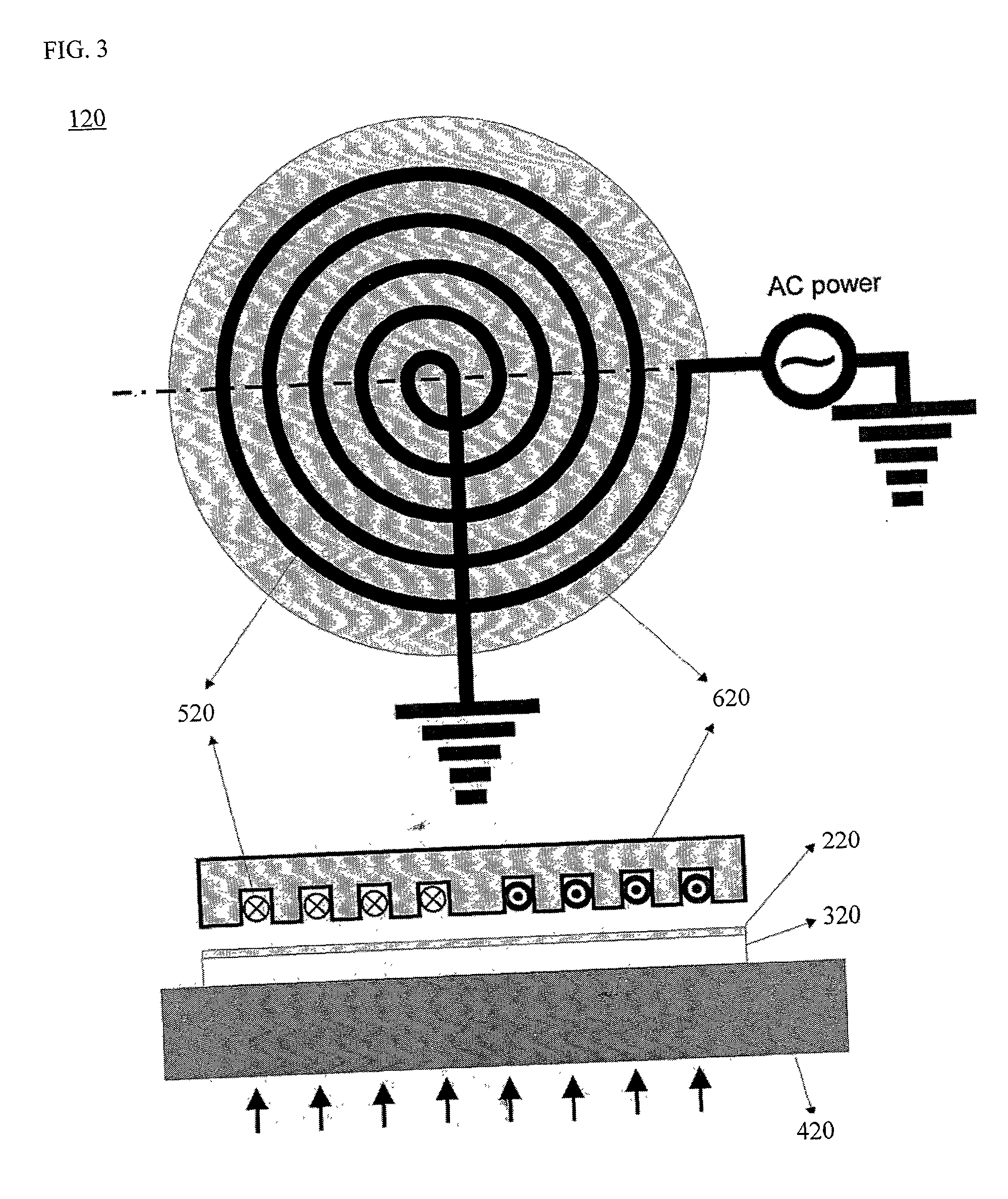

Apparatuses for heat-treatment of semiconductor films under low temperature

InactiveUS20030197007A1Increase the magnetic field strengthEfficient heat treatmentCoil arrangementsSemiconductor/solid-state device manufacturingHeat sensitiveSolar cell

Owner:VIATRON TECH INC

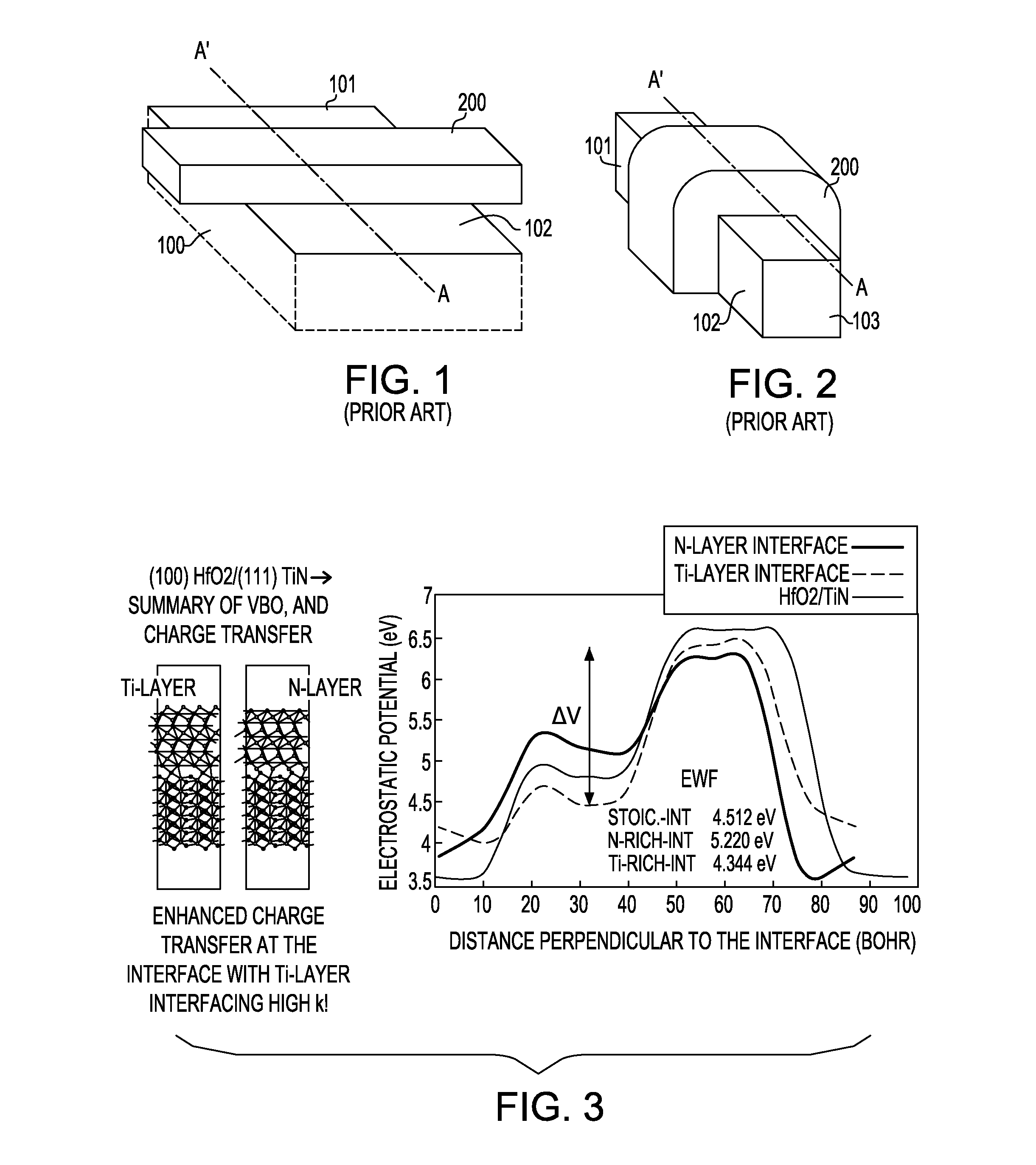

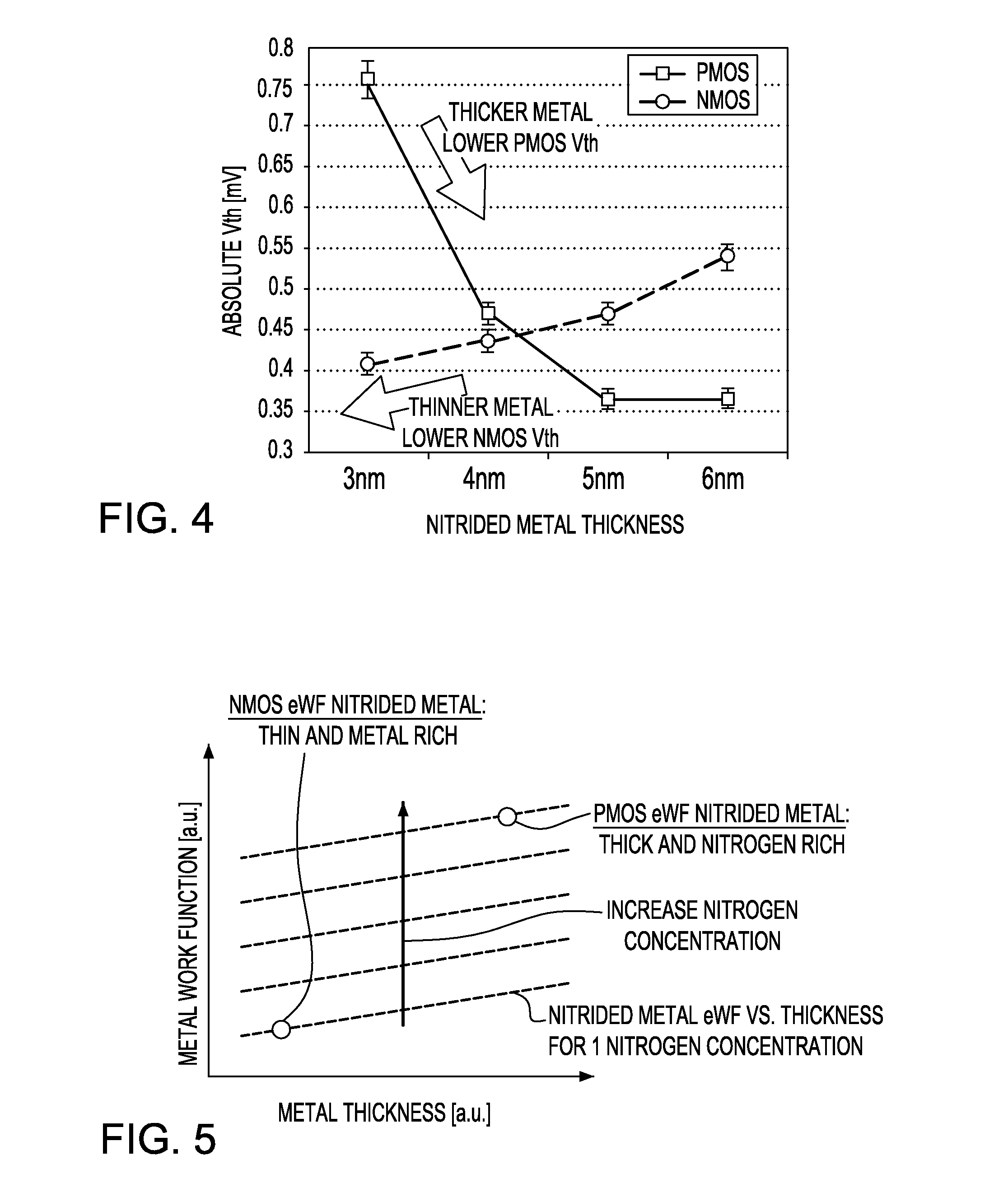

Effective Work Function Modulation by Metal Thickness and Nitrogen Ratio for a Last Approach CMOS Gate

InactiveUS20130087856A1High budgetDecreases eWFTransistorSemiconductor/solid-state device manufacturingCMOSThin metal

A CMOS structure is formed on a semiconductor substrate that includes first and second regions having an nFET and a pFET respectively formed thereon. Each nFET and pFET device is provided with a gate, a source and drain, and a channel formed on the substrate. A high permittivity dielectric layer formed on top of the channel is superimposed to the permittivity dielectric layer. The pFET gate includes a thick metal nitride alloy layer or rich metal nitride alloy or carbon metal nitride layer that provides a controlled WF. Superimposed to the permittivity dielectric layer, the nFET gate is provided with a thin metal nitride alloy layer, enabling to control the WF. A metal deposition is formed on top of the respective nitride layers. The gate last approach characterized by having a high thermal budget smaller than 500° C. used for post metal deposition, following the dopant activation anneal.

Owner:GLOBALFOUNDRIES INC

Apparatuses for heat-treatment of semiconductor films under low temperature

InactiveUS6747254B2Improved kineticsHeat-treated continuously and efficientlyCoil arrangementsSemiconductor/solid-state device manufacturingHeat sensitiveSolar cell

Owner:VIATRON TECH INC

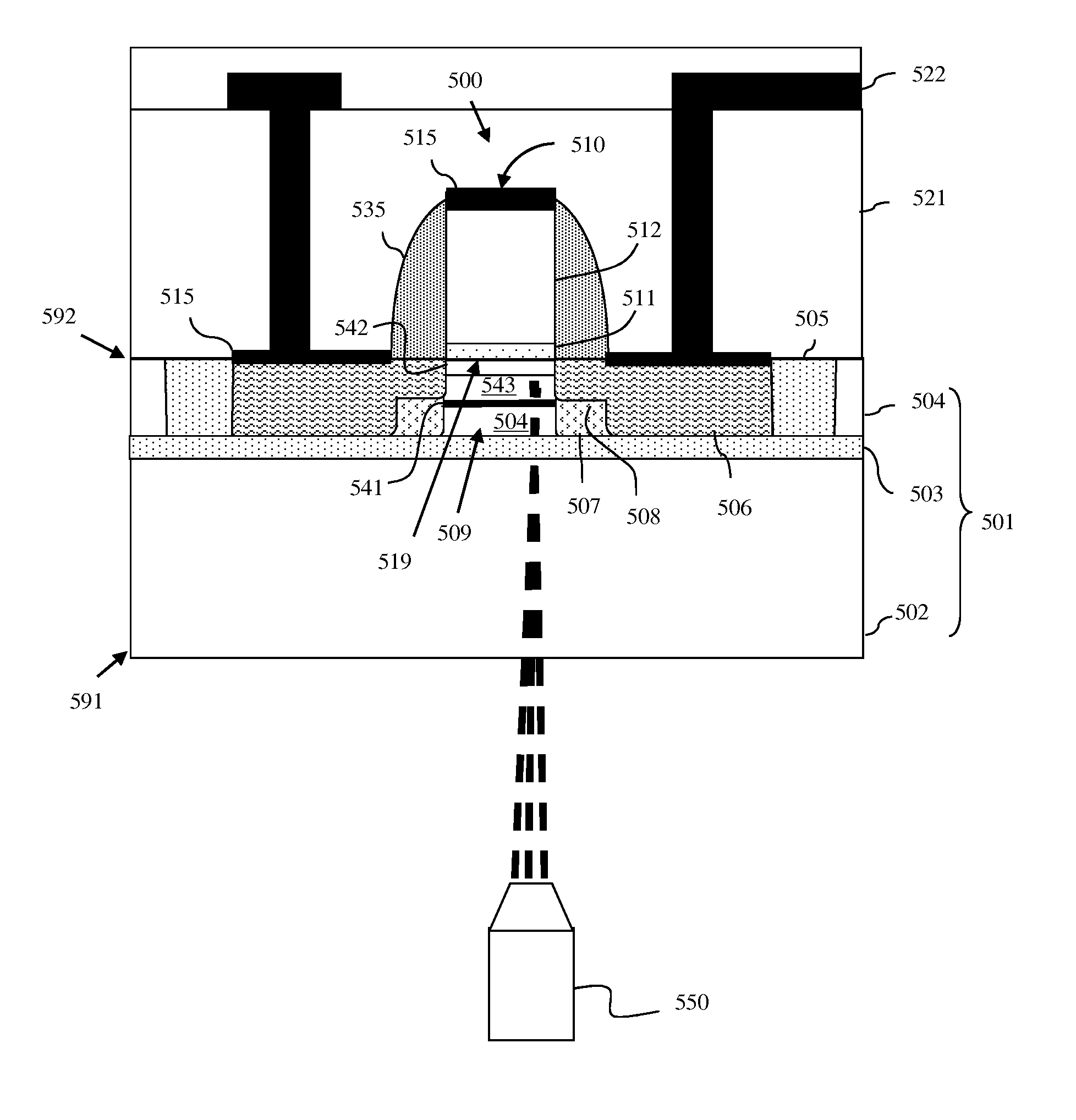

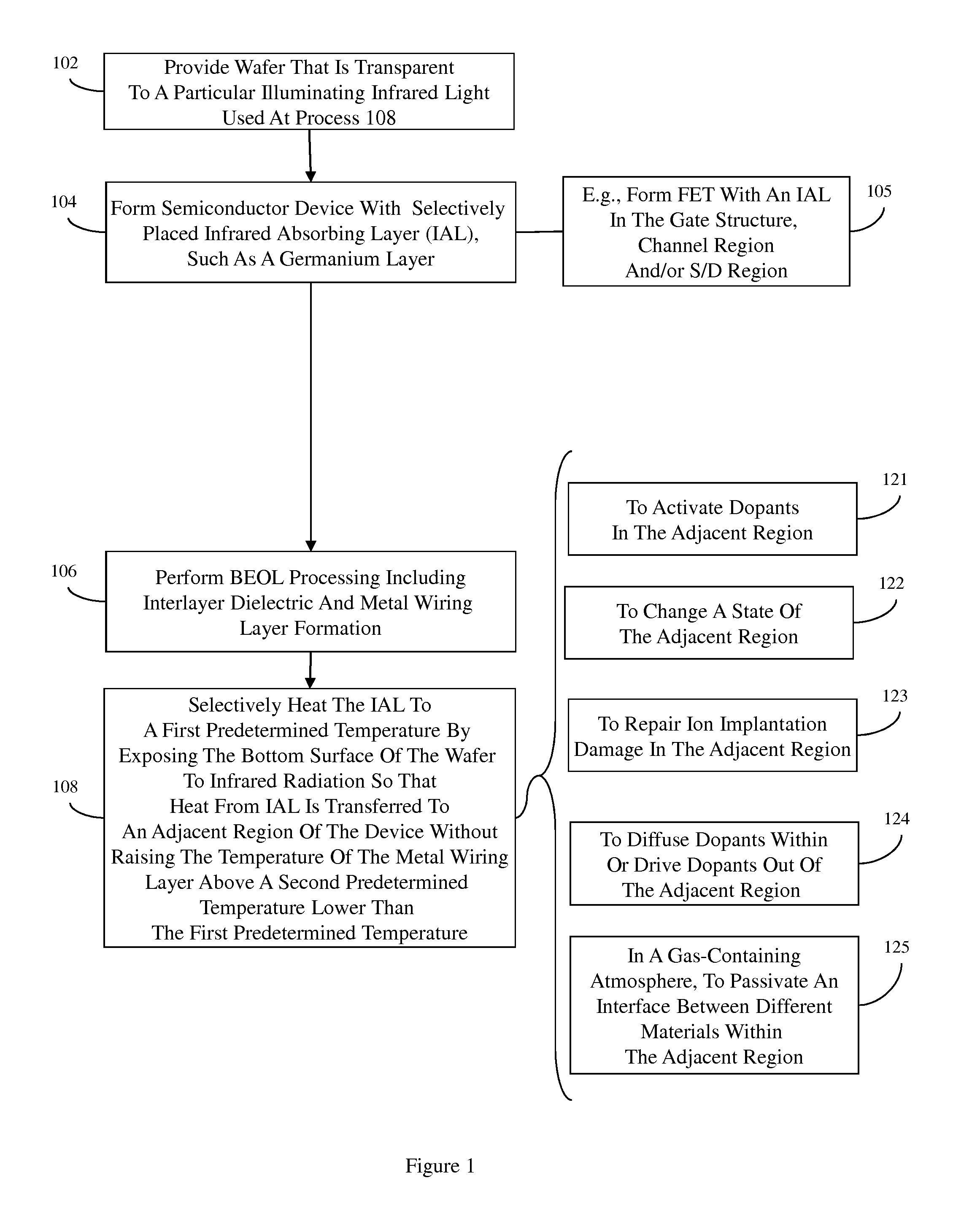

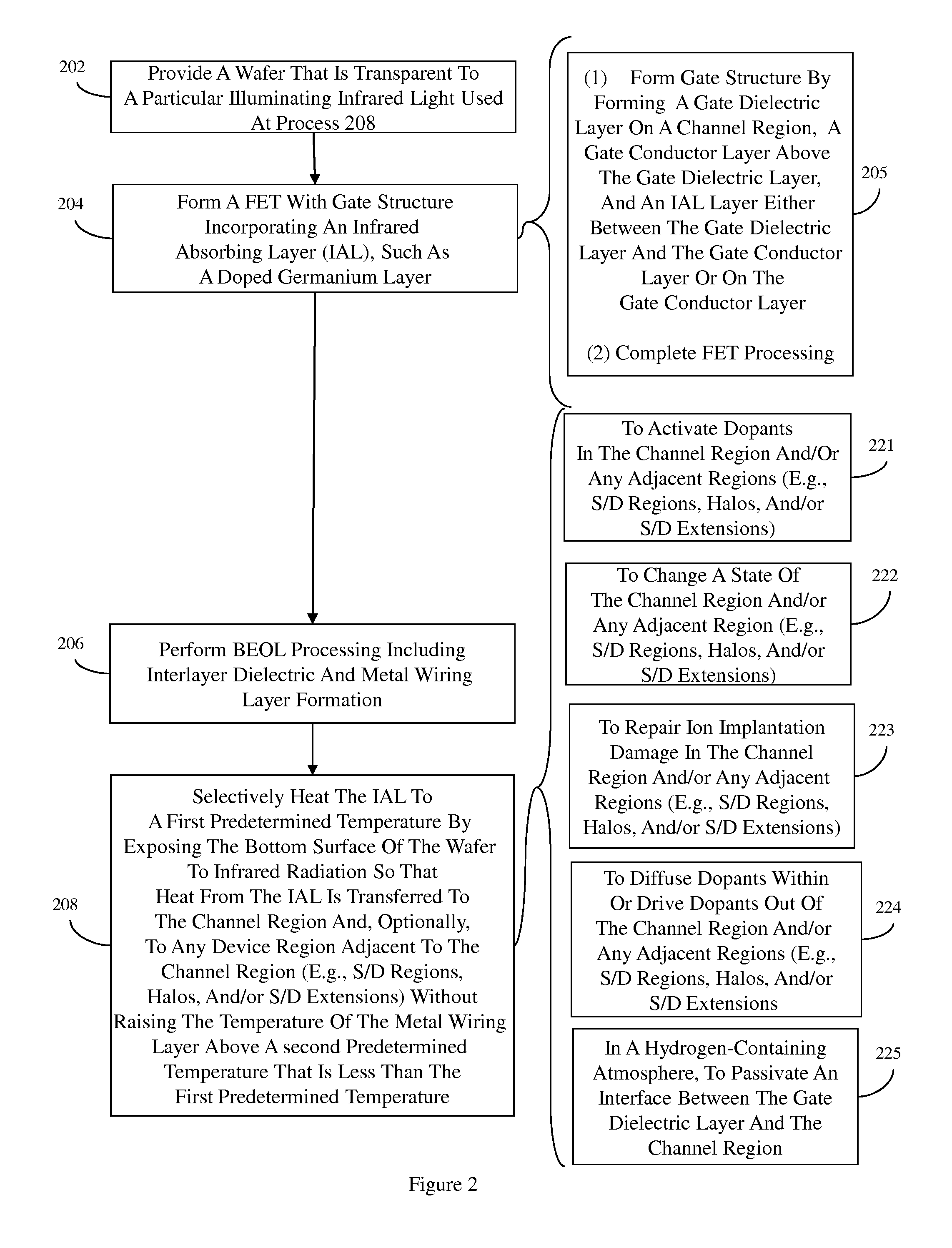

Semiconductor wafer processing method that allows device regions to be selectively annealed following back end of the line (BEOL) metal wiring layer formation

InactiveUS8021950B1TransistorSemiconductor/solid-state device manufacturingState variationLength wave

Disclosed are embodiments of a semiconductor wafer processing method that allow device regions to be selectively annealed following back end of the line (BEOL) metal wiring formation without degrading wiring layer reliability. In the embodiments, a semiconductor device is formed adjacent to the top surface of a wafer such that it incorporates a selectively placed infrared absorbing layer (IAL). Then, following BEOL metal wiring formation, the bottom surface of the wafer is exposed to an infrared light having a wavelength that is transparent to the wafer. The infrared light is absorbed by and, thereby heats up the IAL to a first predetermined temperature (e.g., a dopant activation temperature, a temperature required for a state change, etc.). The resulting heat is transferred from the IAL to an adjacent region of the semiconductor device without raising the temperature of the metal wiring above a second predetermined temperature (e.g., a temperature that could degrade the metal wiring) that is lower than the first predetermined temperature.

Owner:ULTRATECH INT INC

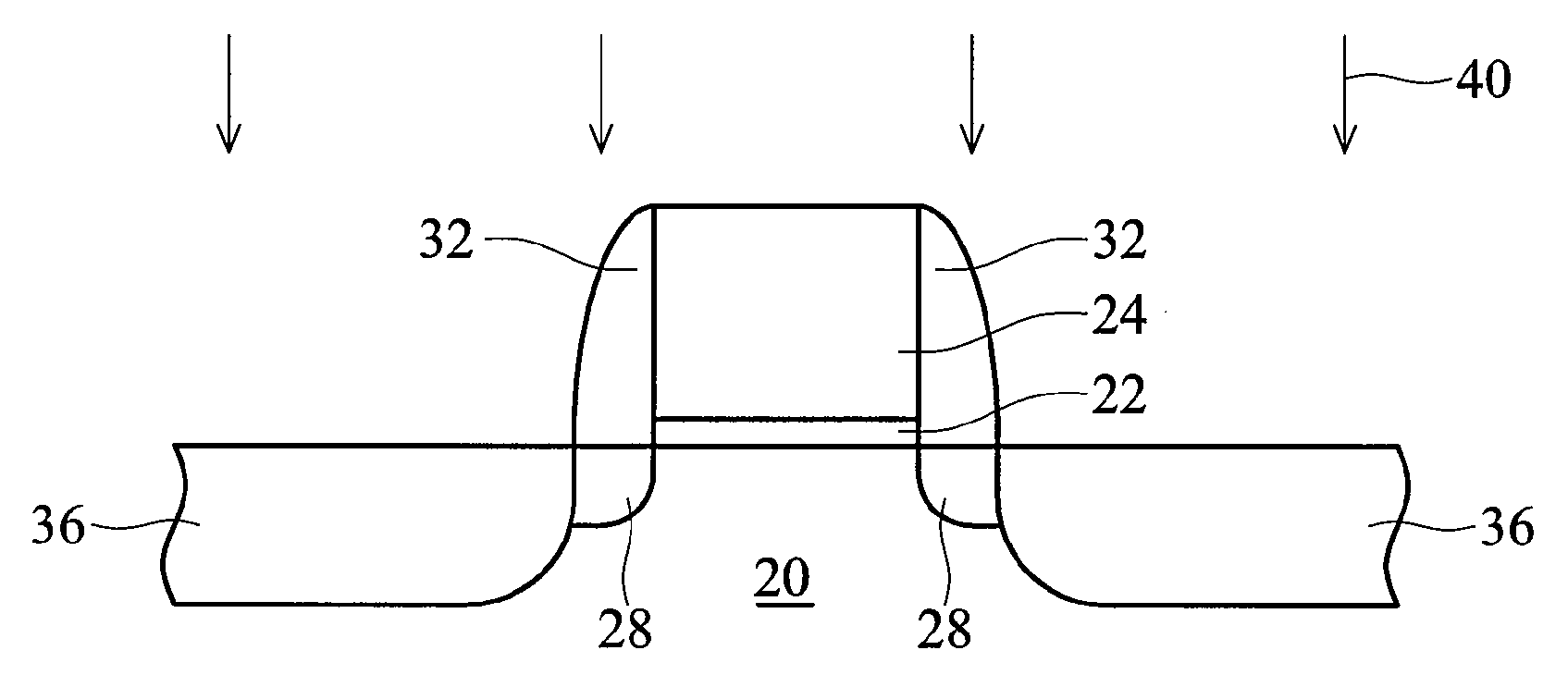

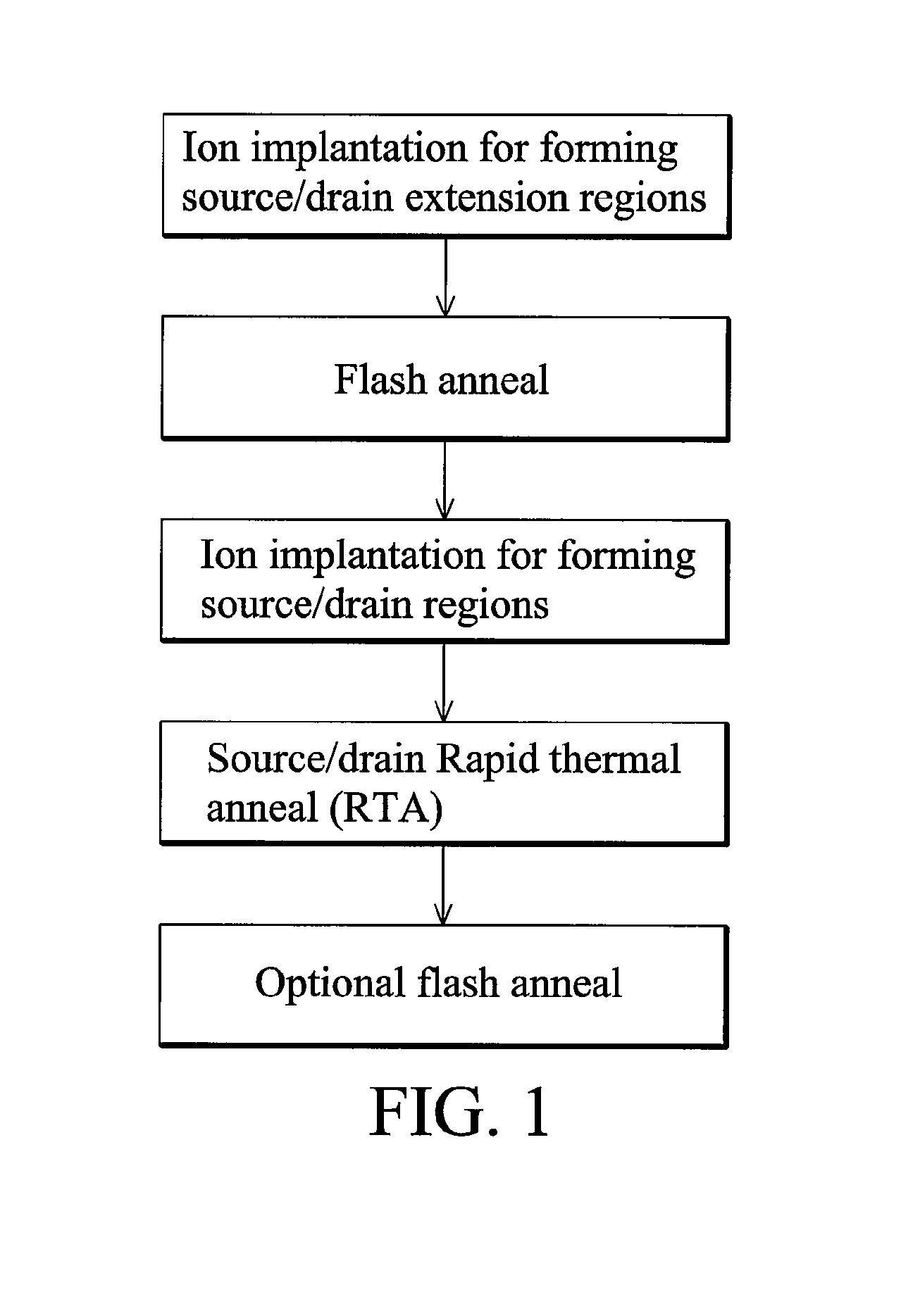

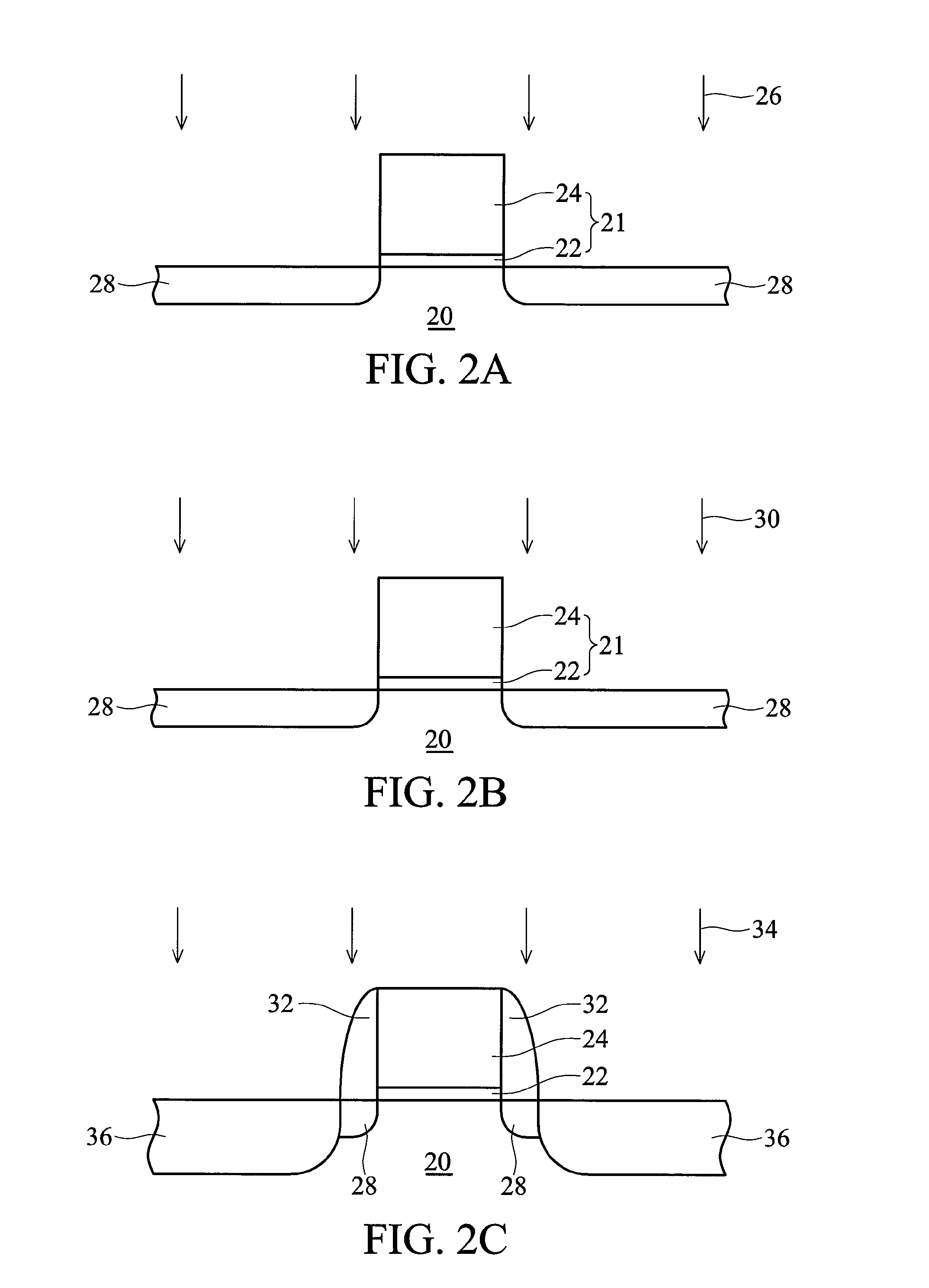

Method of enhancing dopant activation without suffering additional dopant diffusion

ActiveUS20080242039A1Quick stepsTransistorSemiconductor/solid-state device manufacturingDopant ActivationRapid thermal annealing

Owner:TAIWAN SEMICON MFG CO LTD

Shallow junction formation and high dopant activation rate of MOS devices

InactiveUS20080293204A1Reduce junction depthImproved short channel characteristicTransistorSemiconductor/solid-state device manufacturingPhosphorous acidSemiconductor structure

A method for forming a semiconductor structure includes providing a semiconductor substrate; forming a gate stack over the semiconductor substrate; implanting carbon into the semiconductor substrate; and implanting an n-type impurity into the semiconductor substrate to form a lightly doped source / drain (LDD) region, wherein the n-type impurity comprises more than one phosphorous atom. The n-type impurity may include phosphorous dimer or phosphorous tetramer.

Owner:TAIWAN SEMICON MFG CO LTD

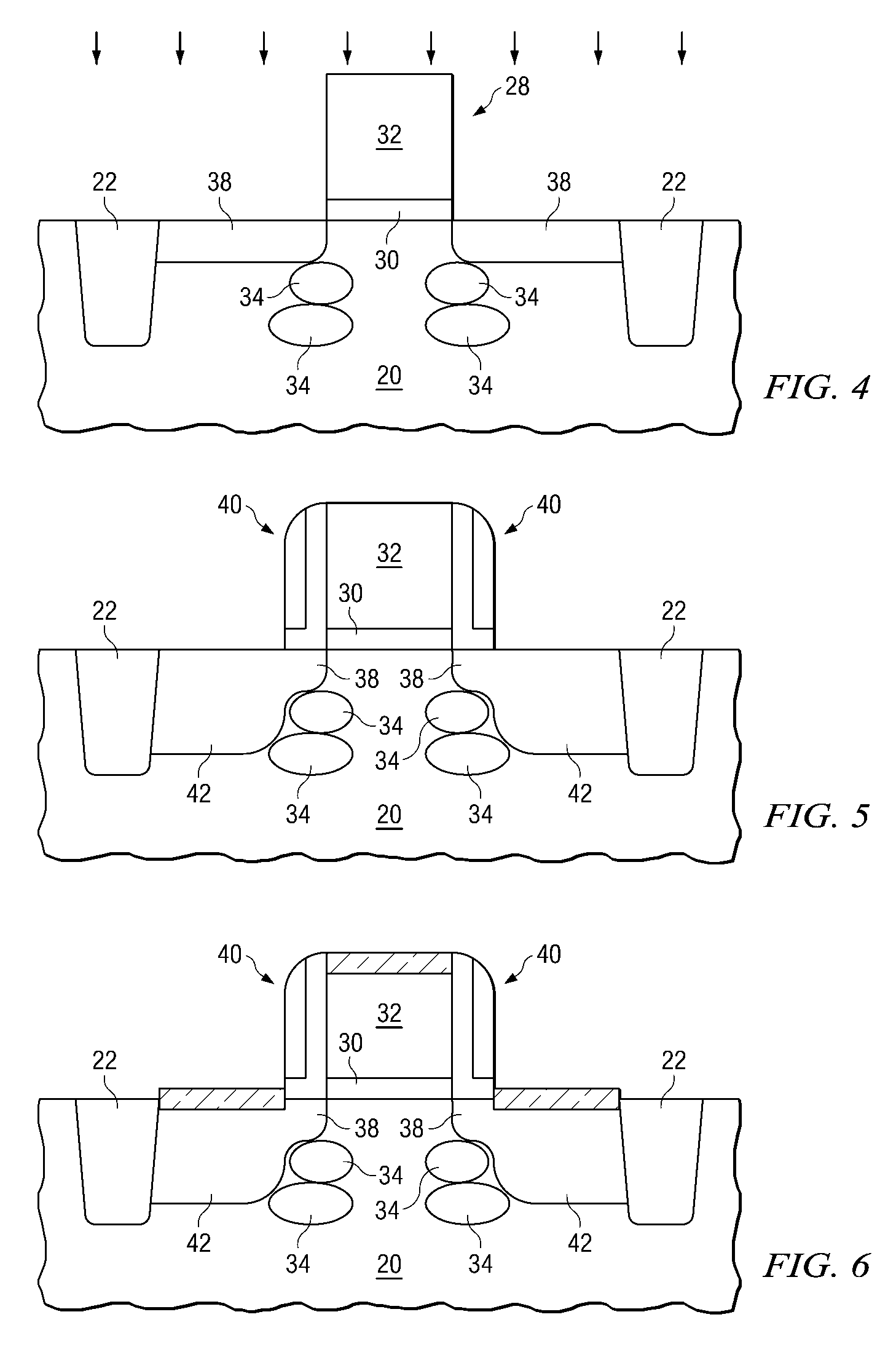

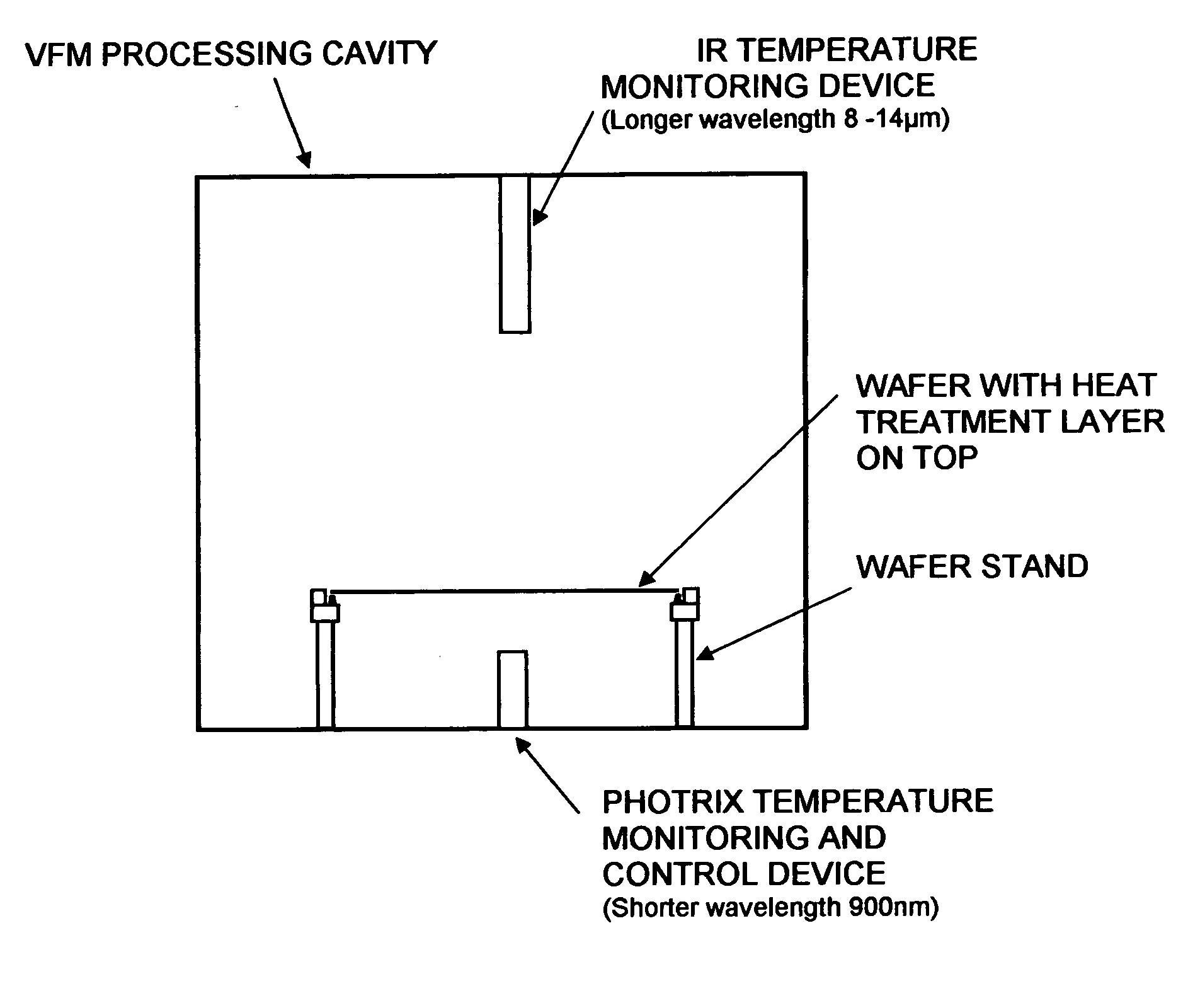

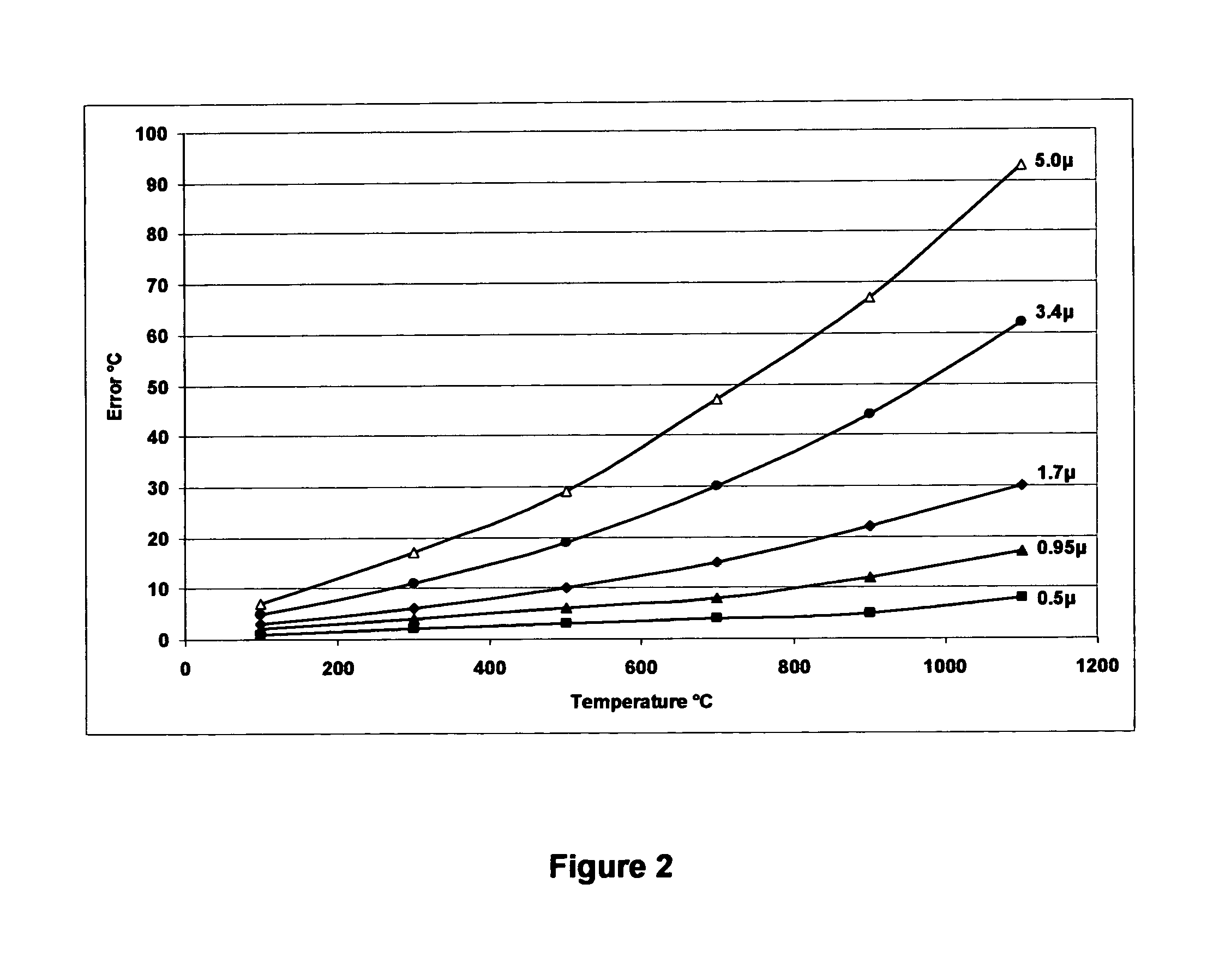

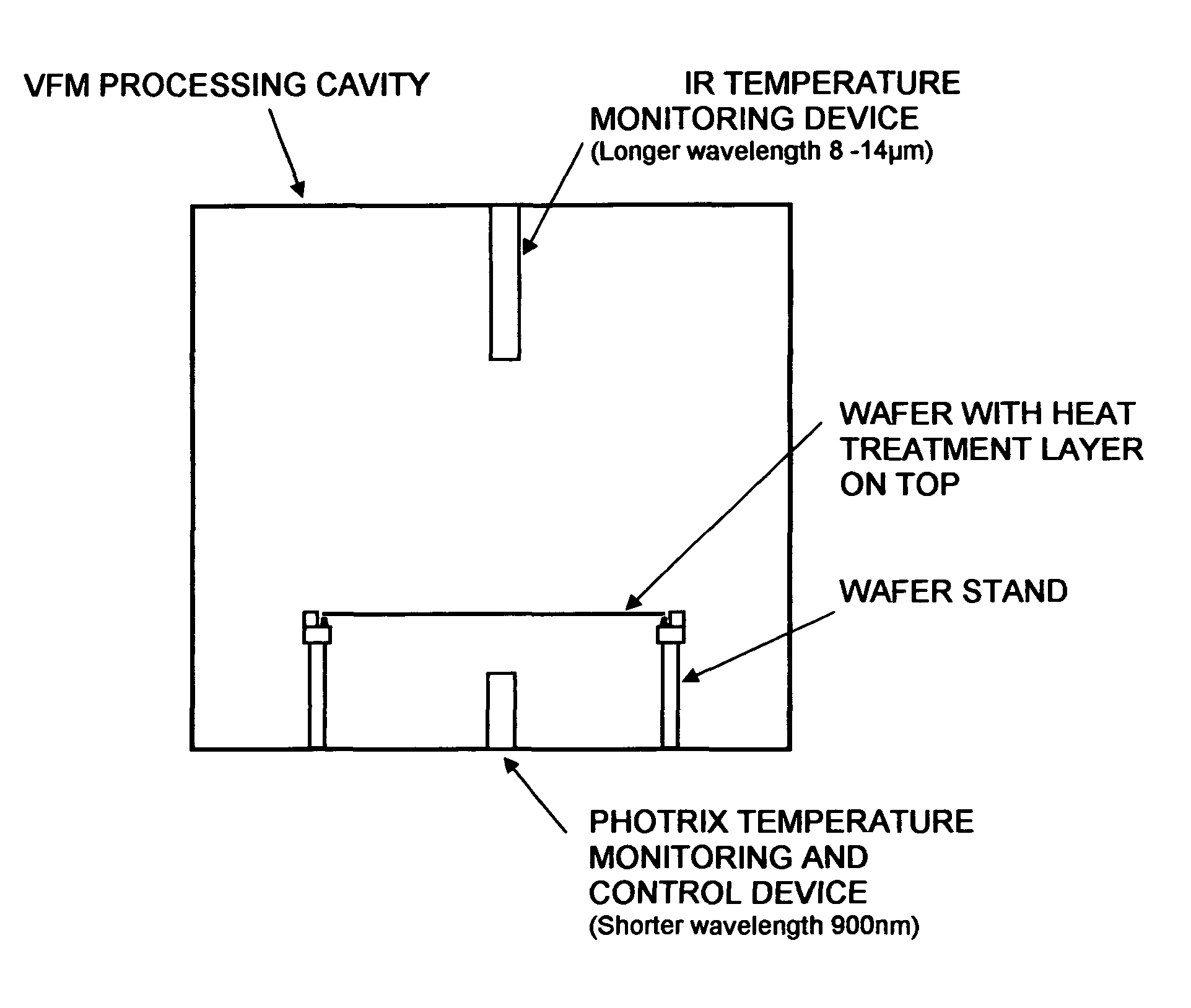

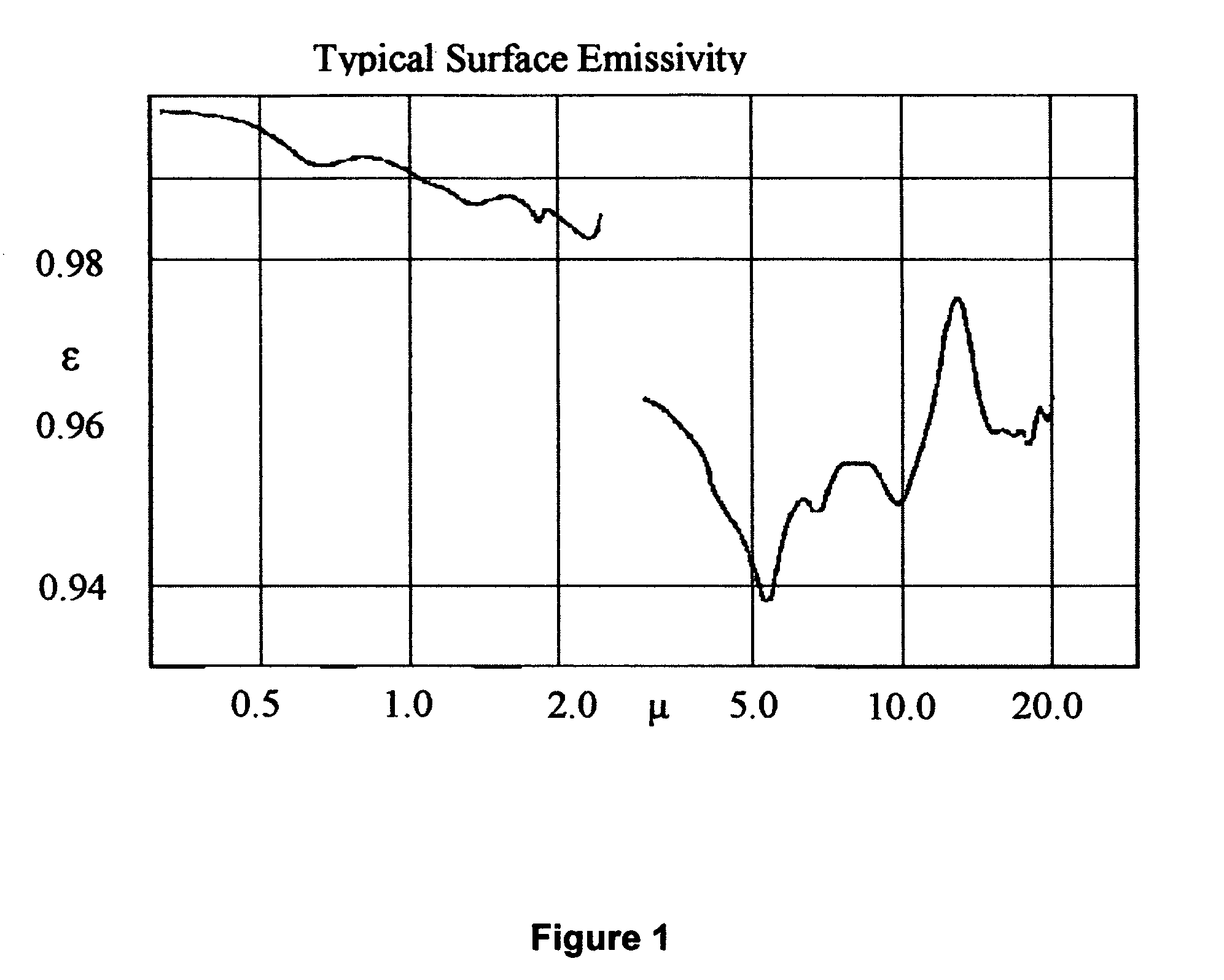

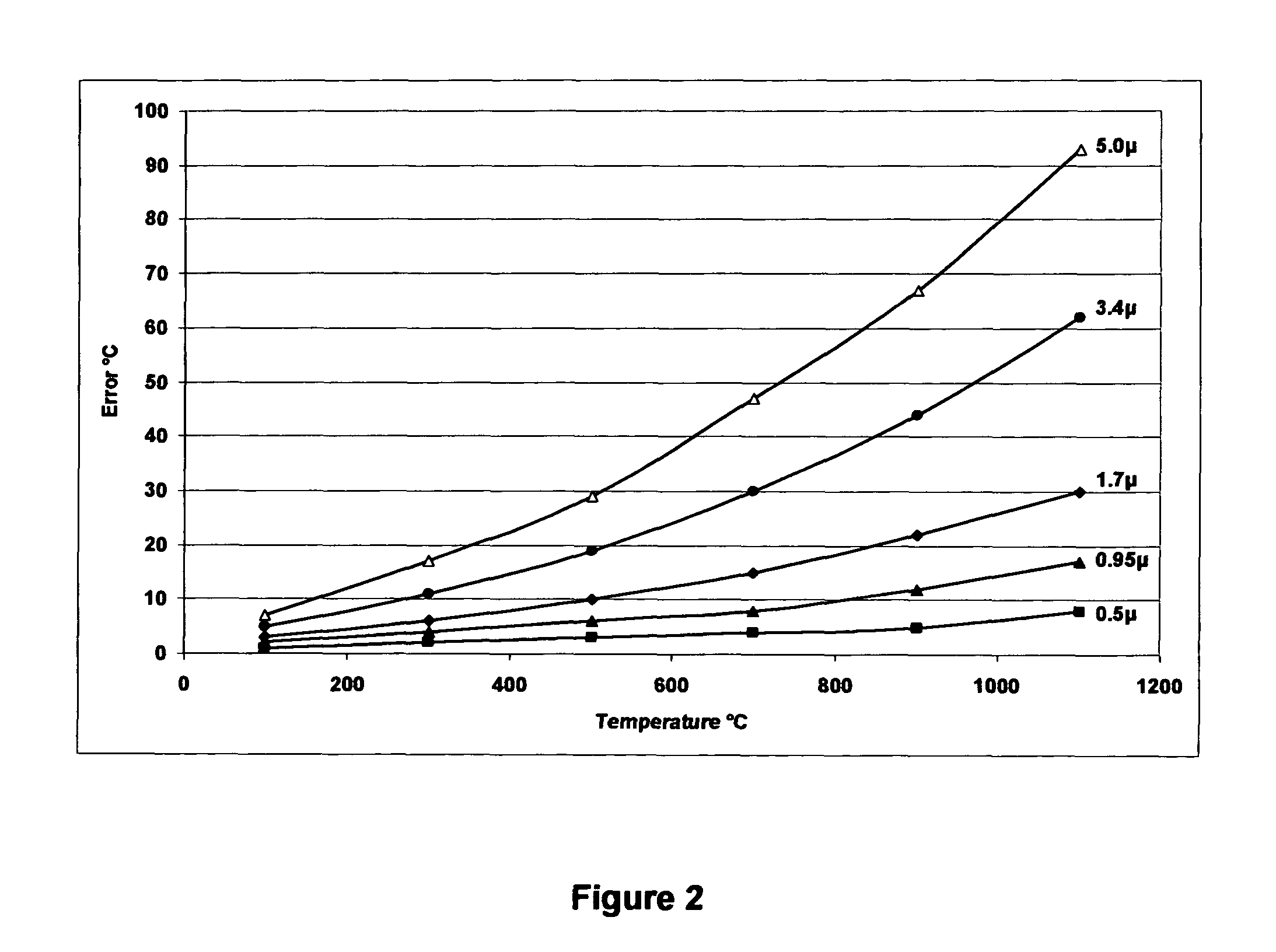

Method and apparatus for controlled thermal processing

ActiveUS20110076786A1Optical radiation measurementDomestic stoves or rangesEmissivityMeasurement device

A materials processing system comprises a thermal processing chamber including a heating source, a first noncontacting thermal measurement device positioned to measure temperature on a first area of the material being processed, and, a second noncontacting thermal measurement device positioned to measure temperature on a second area of the material being processed, the first device being relatively more sensitive to changes in surface emissivity than the second device. By comparing the outputs of the two devices, emissivity changes can be detected and used as a proxy for some physical change in the workpiece and thereby determine when the desired process has been completed. The system may be used to develop a process recipe, or it may be part of a system for real-time process control based on emissivity changes. Applicable processes include heating, annealing, dopant activation, silicide formation, carburization, nitridation, sintering, oxidation, vapor deposition, metallization, and plating.

Owner:APPLIED MATERIALS INC

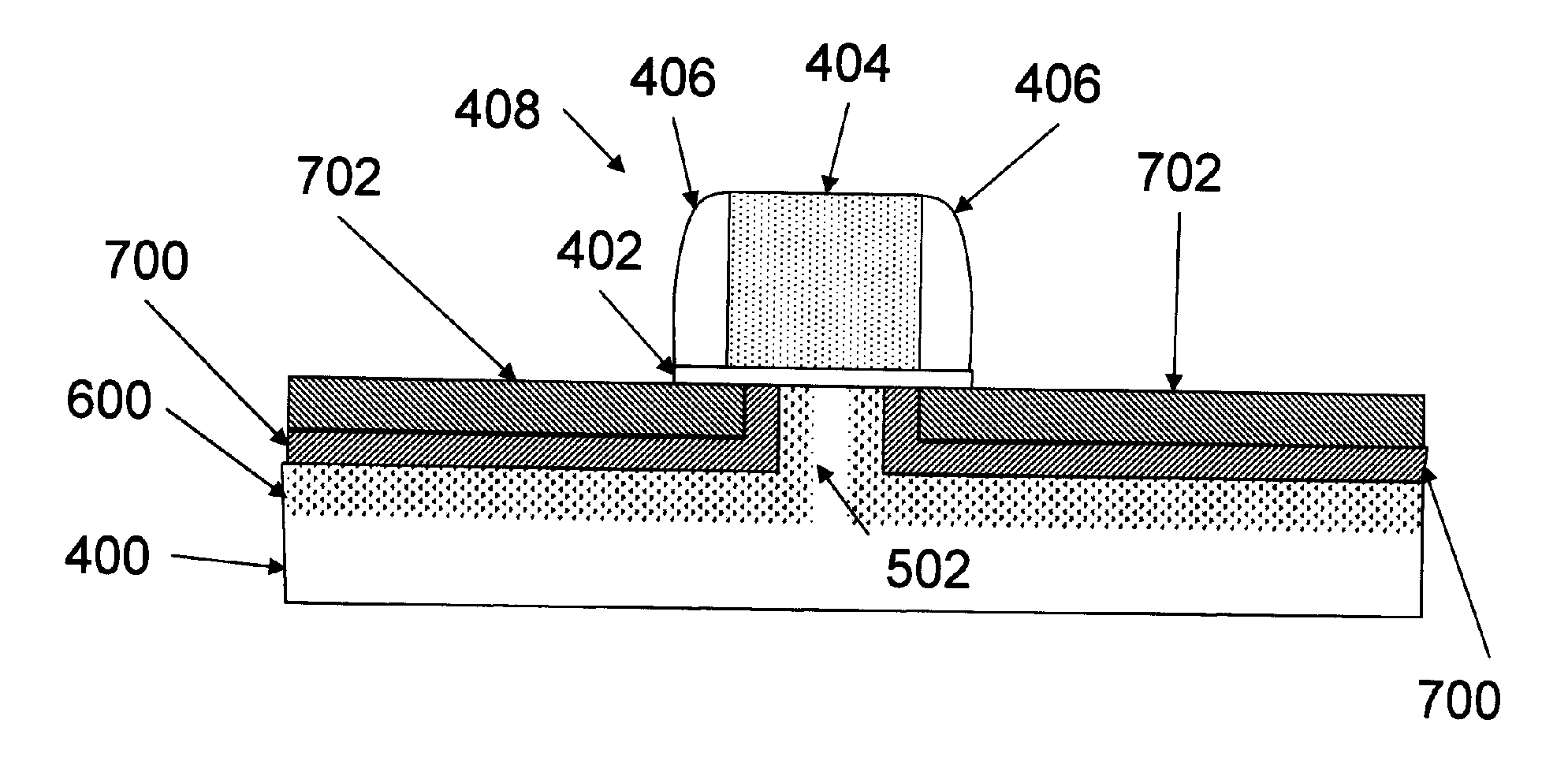

Methods of forming field effect transistors on substrates

InactiveUS7867851B2TransistorSemiconductor/solid-state device manufacturingField-effect transistorDopant Activation

The invention includes methods of forming field effect transistors. In one implementation, the invention encompasses a method of forming a field effect transistor on a substrate, where the field effect transistor comprises a pair of conductively doped source / drain regions, a channel region received intermediate the pair of source / drain regions, and a transistor gate received operably proximate the channel region. Such implementation includes conducting a dopant activation anneal of the pair of source / drain regions prior to depositing material from which a conductive portion of the transistor gate is made. Other aspects and implementations are contemplated.

Owner:MICRON TECH INC

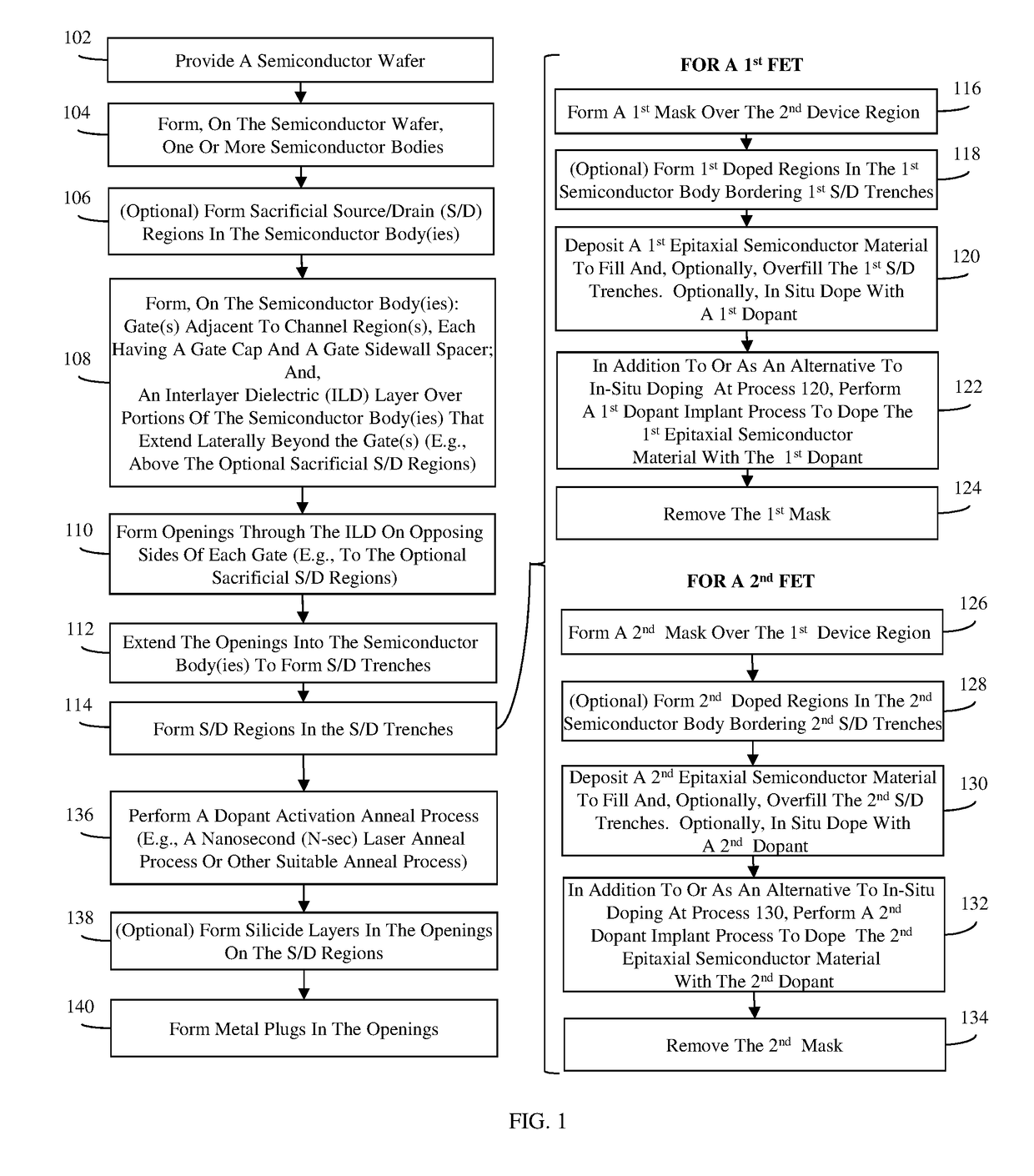

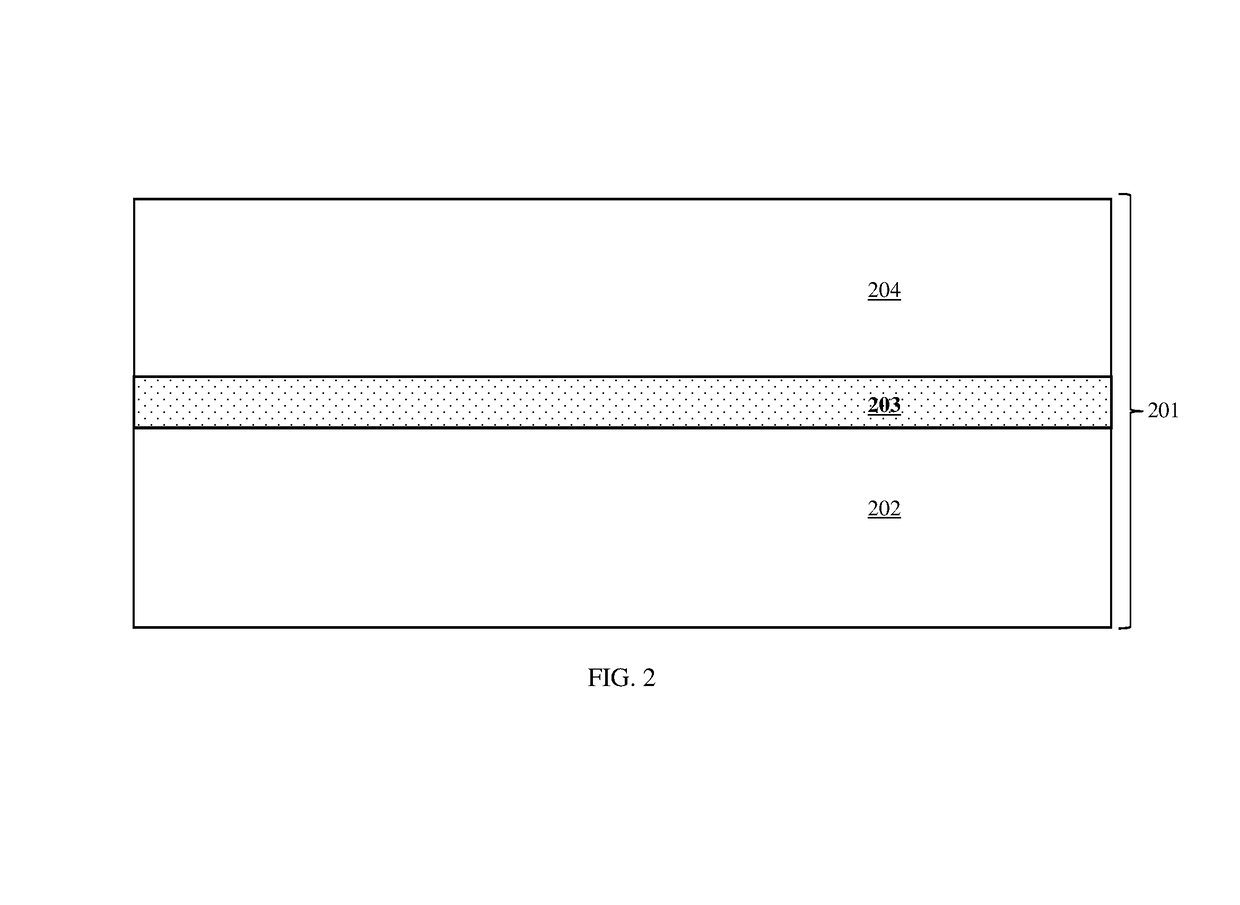

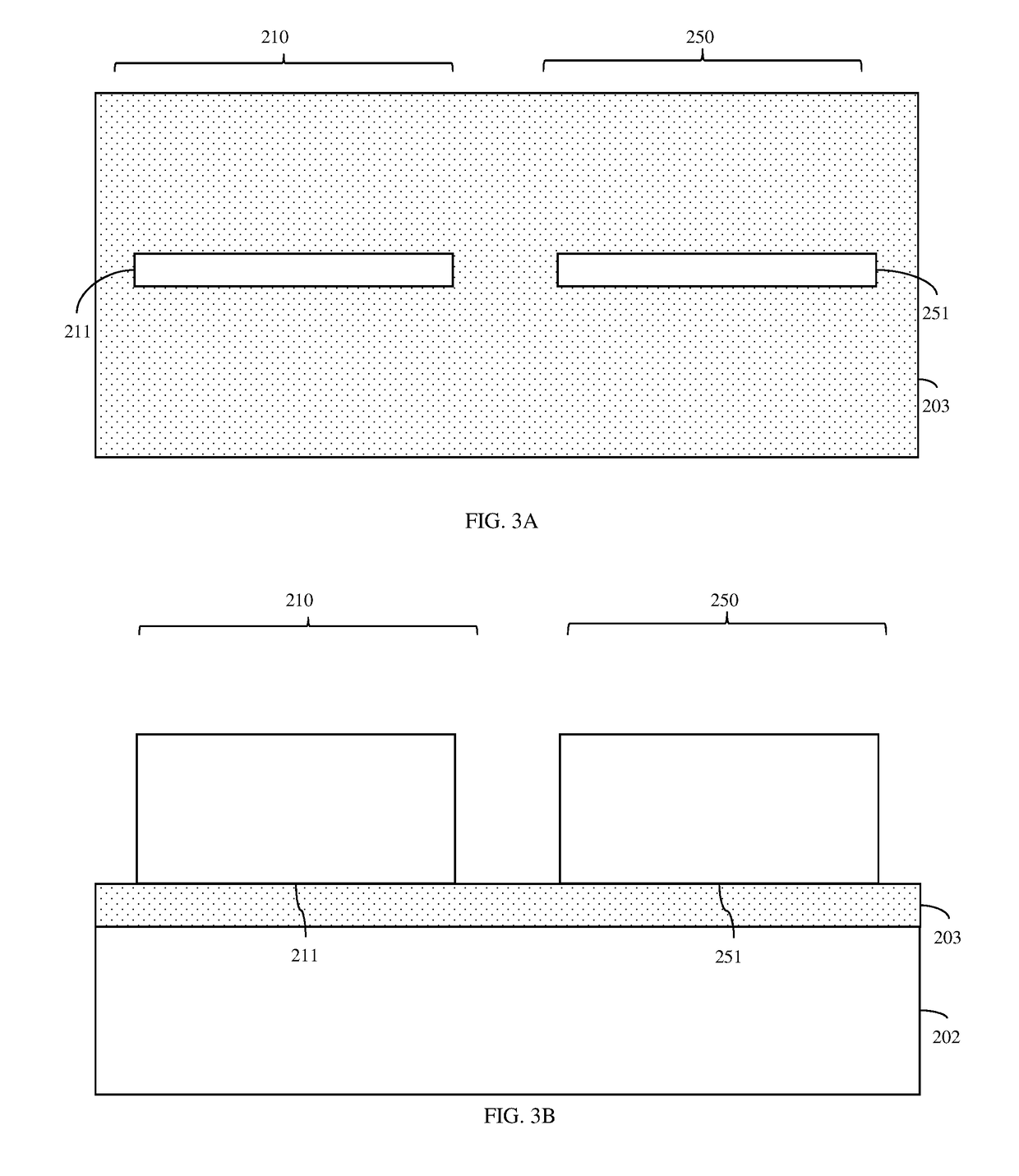

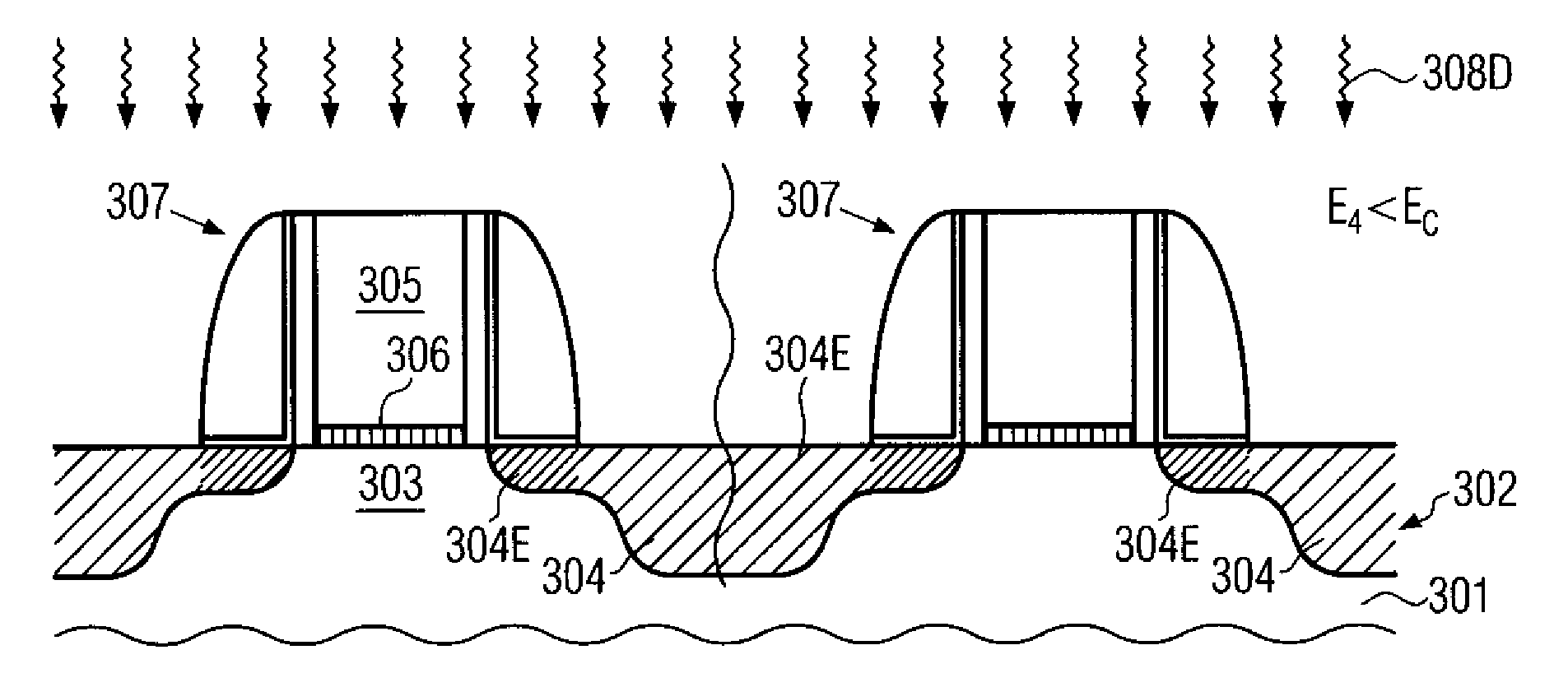

Field effect transistors with reduced parasitic resistances and method

ActiveUS10062692B1Reduce inactivationOptimal strain engineeringTransistorSemiconductor/solid-state device manufacturingElectrical resistance and conductanceDielectric

Disclosed are methods of forming field effect transistor(s) (FET) and the resulting structures. Instead of forming the FET source / drain (S / D) regions during front end of the line (FEOL) processing, they are formed during middle of the line (MOL) processing through metal plug openings in an interlayer dielectric (ILD) layer. Processes used to form the S / D regions through the metal plug openings include S / D trench formation, epitaxial semiconductor material deposition, S / D dopant implantation and S / D dopant activation, followed by silicide and metal plug formation. Since the post-MOL processing thermal budget is low, the methods ensure reduced S / D dopant deactivation, reduced S / D strain reduction, and reduced S / D dopant diffusion and, thus, enable reduced S / D resistance, optimal strain engineering, and flexible junction control, respectively. Since the S / D regions are formed through the metal plug openings, the methods eliminate overlay errors that can lead to uncontacted or partially contacted S / D regions.

Owner:GLOBALFOUNDRIES US INC

Technique for enhancing dopant activation by using multiple sequential advanced laser/flash anneal processes

InactiveUS20080268597A1Enhanced transistor performanceReduce probabilitySemiconductor/solid-state device manufacturingEngineeringDopant Activation

By performing multiple radiation-based anneal processes on the basis of less critical process parameters, the overall risk for creating anneal-induced damage, such as melting of gate portions, may be substantially avoided while nevertheless the respective degree of dopant activation may be enhanced for each individual anneal process. Consequently, the sheet resistance of advanced transistor devices may be reduced with a decreasing number of sequential anneal processes.

Owner:ADVANCED MICRO DEVICES INC

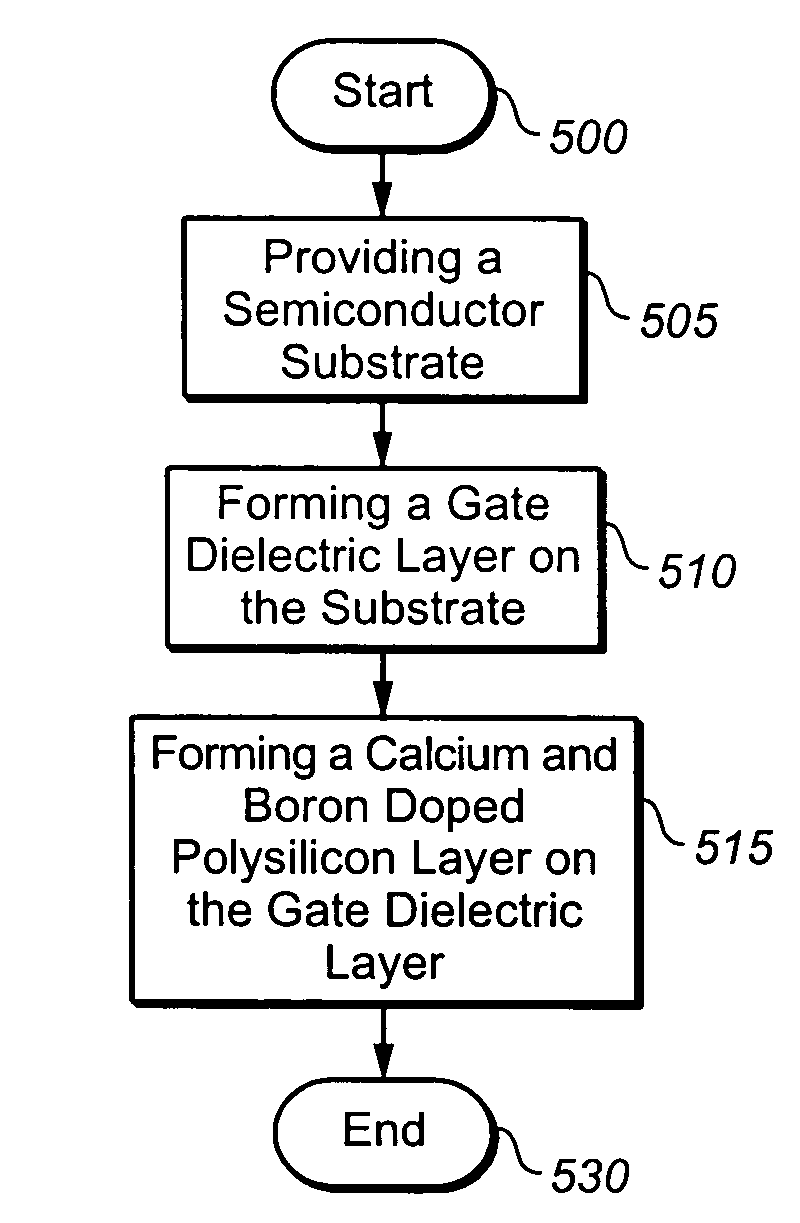

Calcium doped polysilicon gate electrodes

InactiveUS6930362B1Promote migrationReduce decreaseSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricDopant Activation

A calcium doped polysilicon gate electrodes for PMOS containing semiconductor devices. The calcium doped PMOS gate electrodes reduce migration of the boron dopant out of the gate electrode, through the gate dielectric and into the substrate thereby reducing the boron penetration problem increasingly encountered with smaller device size regimes and their thinner gate dielectrics. Calcium doping of the gate electrode may be achieved by a variety of techniques. It is further believed that the calcium doping may improve the boron dopant activation in the gate electrode, thereby further improving performance.

Owner:BELL SEMICON LLC

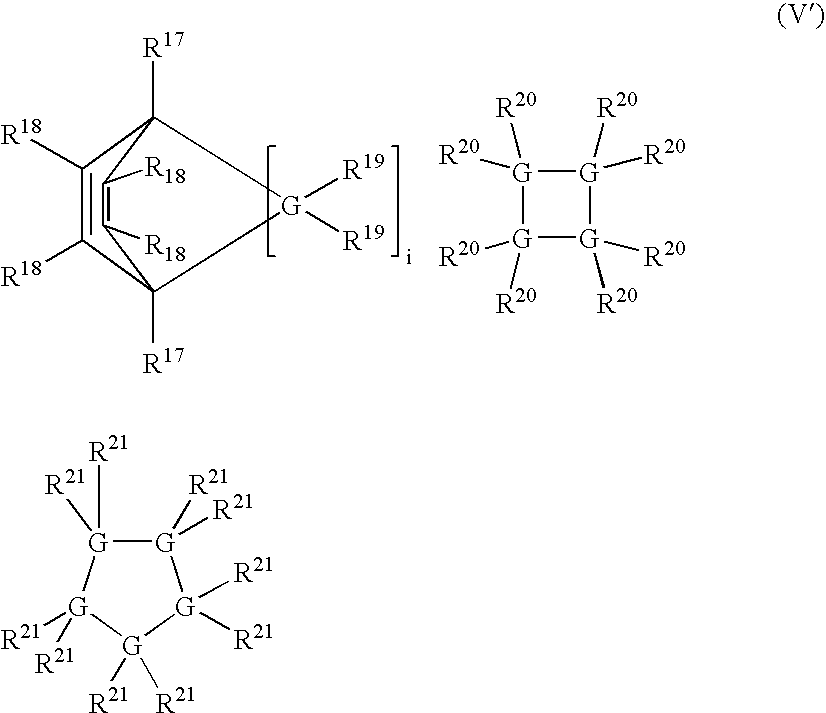

Linear and cross-linked high molecular weight polysilanes, polygermanes, and copolymers thereof, compositions containing the same, and methods of making and using such compounds and compositions

Methods are disclosed of making linear and cross-linked, HMW (high molecular weight) polysilanes and polygermanes, polyperhydrosilanes and polyperhydrogermanes, functional liquids containing the same, and methods of using the liquids in a range of desirable applications. The silane and germane polymers are generally composed of chains of Si and / or Ge substituted with R′ substituents, where each instance of R′ is, for example, independently hydrogen, halogen, alkenyl, alkynyl, hydrocarbyl, aromatic hydrocarbyl, heterocyclic aromatic hydrocarbyl, SiR″3, GeR″3, PR″2, OR″, NR″2, or SR″; where each instance of R″ is independently hydrogen or hydrocarbyl. The cross-linked polymers can be synthesized by dehalogenative coupling or dehydrocoupling. The linear polymers can be synthesized by ring-opening polymerization. The polymers can be further modified by halogenation and / or reaction with the source of hydride to furnish perhydrosilane and perhydrogermane polymers, which are used in liquid ink formulations. The synthesis allows for tuning of the liquid properties (e.g., viscosity, volatility, and surface tension). The liquids can be used for deposition of films and bodies by spincoating, inkjetting, dropcasting, etc., with or without the use of UV irradiation. The deposited films can be converted into amorphous and polycrystalline silicon or germanium, and silicon or germanium oxide or nitride by curing at 400-600 DEG C. and (optionally) laser- or heat-induced crystallization (and / or dopant activation, when dopant is present).

Owner:ENSURGE MICROPOWER ASA

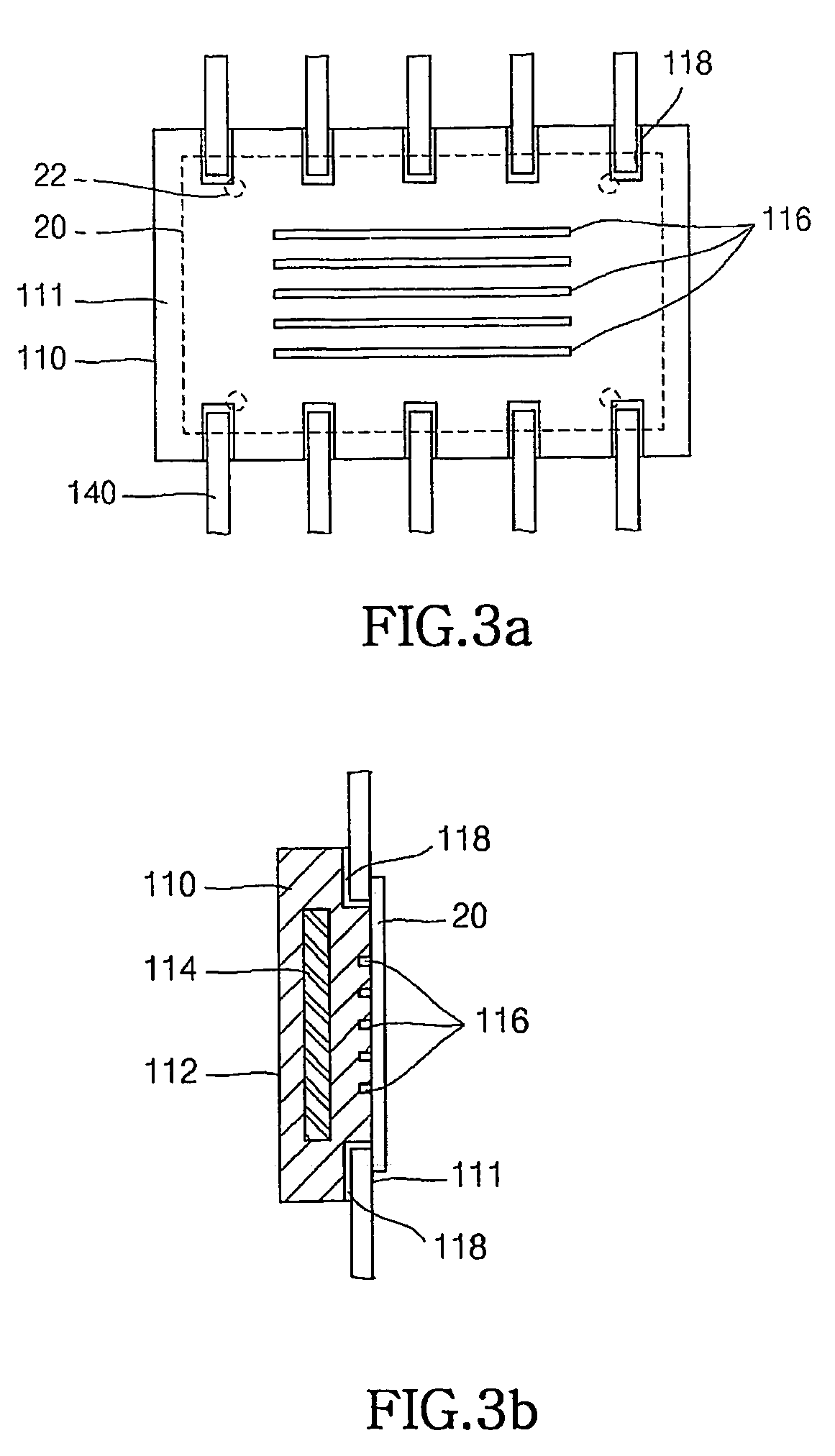

Methods and apparatuses for heat treatment of semiconductor films upon thermally susceptible non-conducting substrates

InactiveUS20050186723A1Maximize goalImprove process uniformitySemiconductor/solid-state device manufacturingIn planeSusceptor

In a method for crystallization or dopant activation heat treatment of a semiconductor film upon a thermally susceptible non-conducting substrate lying onto a susceptor, an induction coil is disposed in close proximity of the semiconductor film and disposed with the electrical current direction of the coil aligned parallel to the in-plane direction of the semiconductor film, a magnetic core is disposed around the coil to strengthen and concentrate a magnetic field generated by the coil onto the semiconductor film, and an alternating electrical current is introduced in the induction coil to generate an alternating magnetic field through the semiconductor film heated by the susceptor to the extent that the semiconductor film can be induction-heated.

Owner:VIATRON TECH INC

Semiconductor device and method for manufacturing the same

InactiveUS20070155070A1Promote recoveryImprove mobilitySolid-state devicesSemiconductor/solid-state device manufacturingOxygenDopant Activation

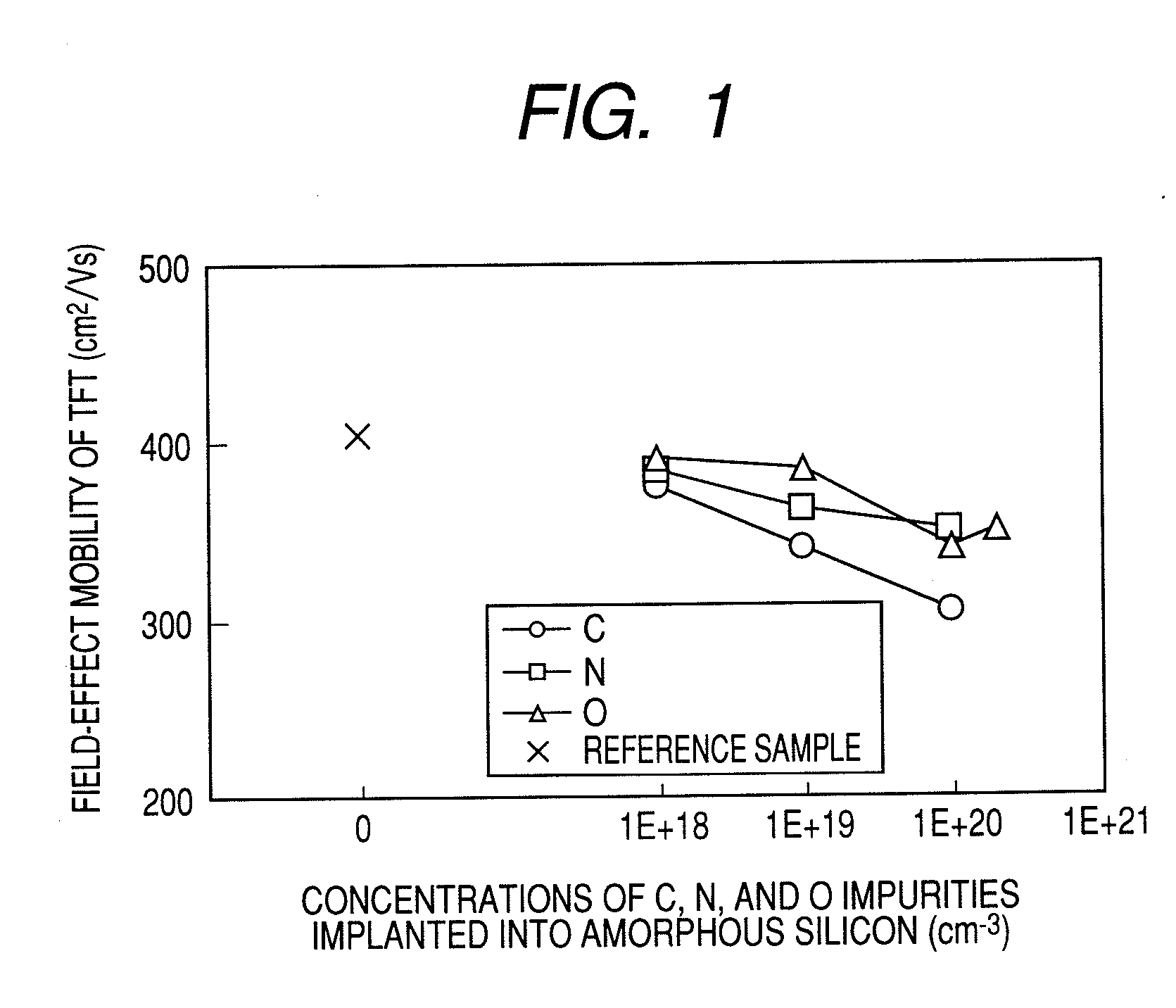

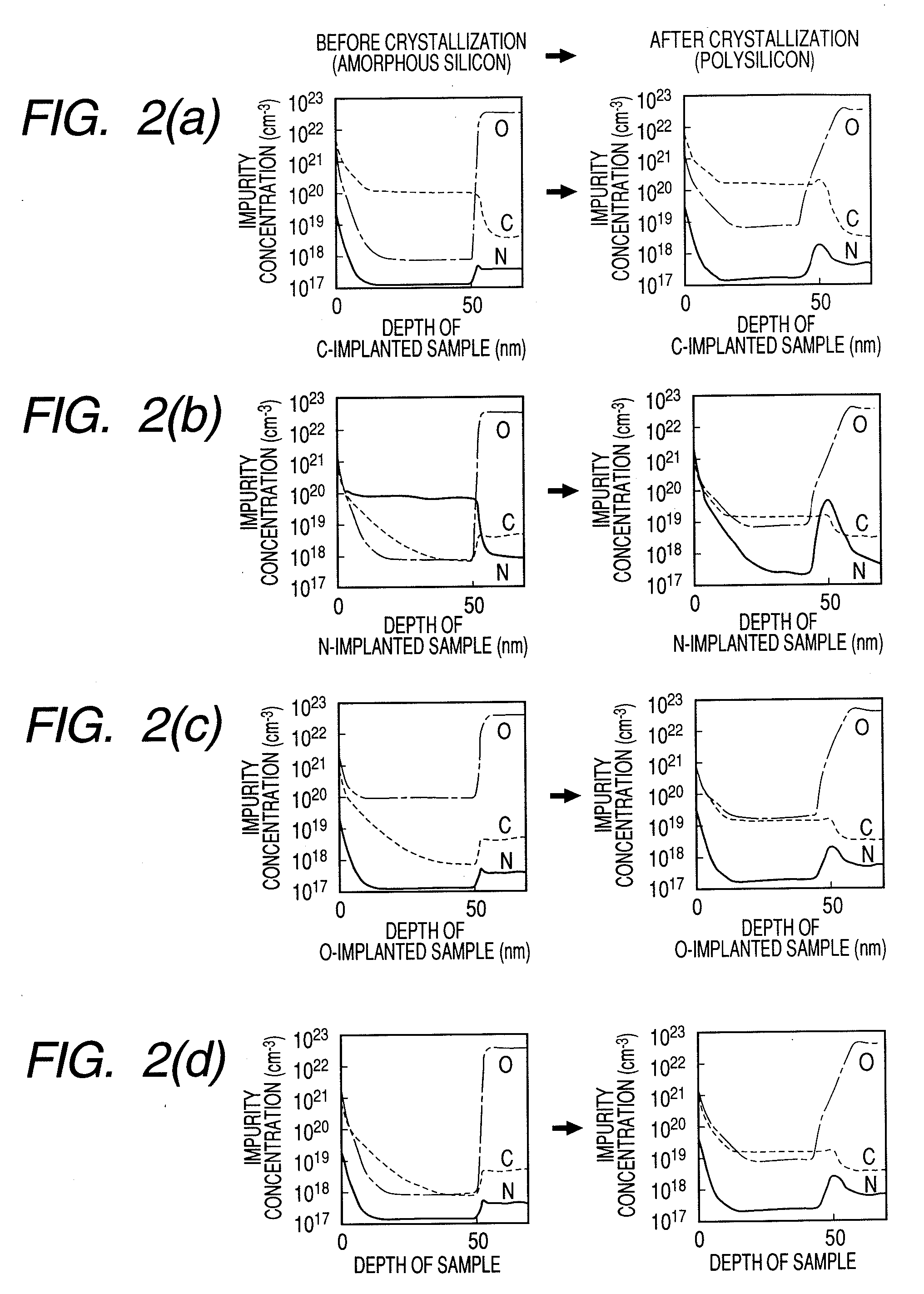

An image display device capable of high-resolution and smooth moving image display, equipped with TFTs in an n-type (or p-type) semiconductor layer with a high on-off ratio and a low resistance. In polysilicon crystallization by laser annealing, an n-type (or p-type) semiconductor layer with a low resistance is produced by performing the following processes in order: implanting nitrogen (N) ions into an amorphous silicon precursor semiconductor film; laser crystallization; implanting n-type (or p-type) dopant ions; and annealing for dopant activation. When fabricating TFTs, this low-resistance semiconductor layer is used to form a source and a drain. Since C, N, and O impurities decrease the mobility of the TFTs, polysilicon is used in which the contaminants concentrations meet the following conditions: carbon concentration ≦3×1019 cm−3, nitrogen concentration ≦5×1017 cm−3, and oxygen concentration ≦3×1019 cm−3.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

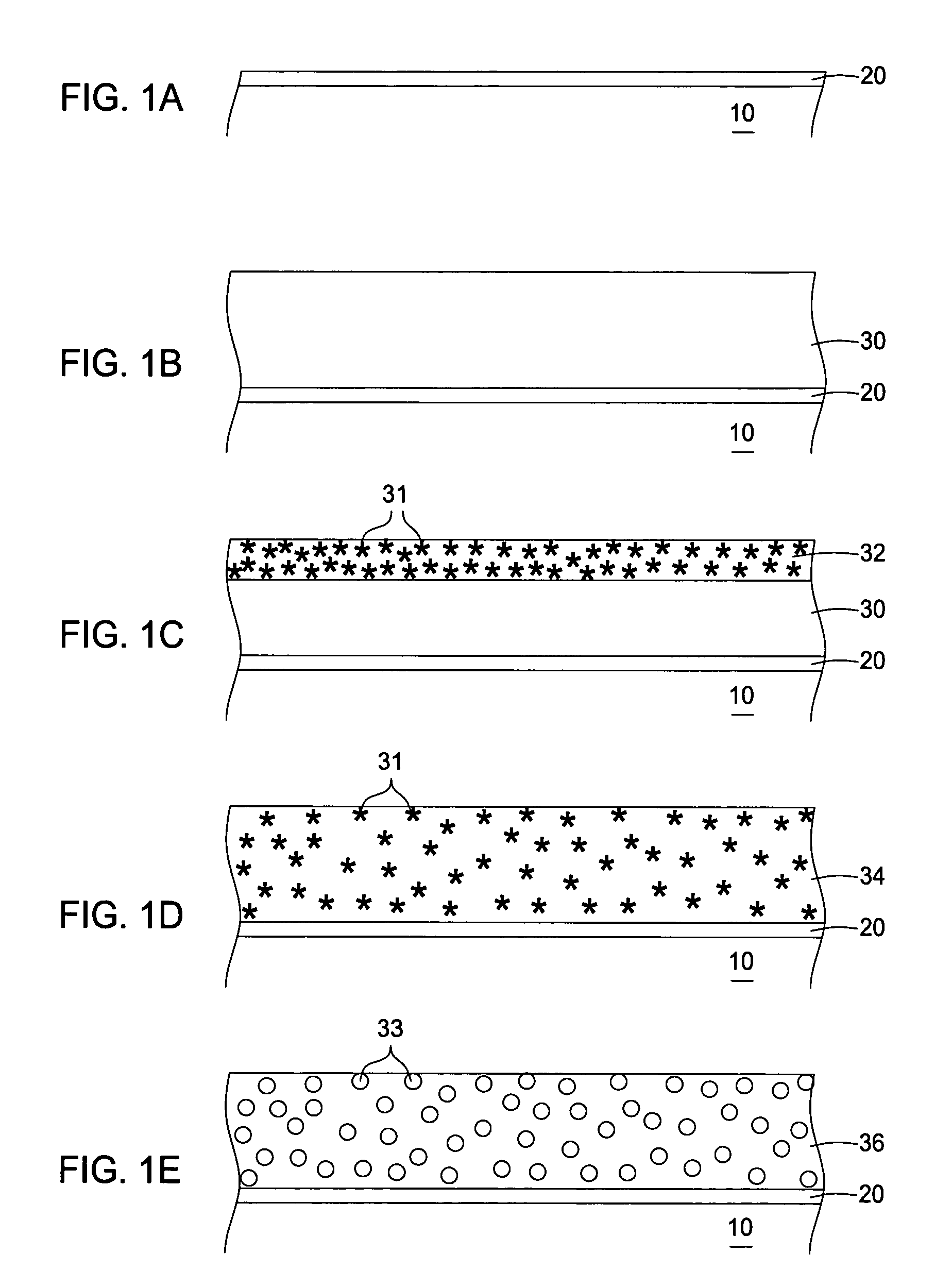

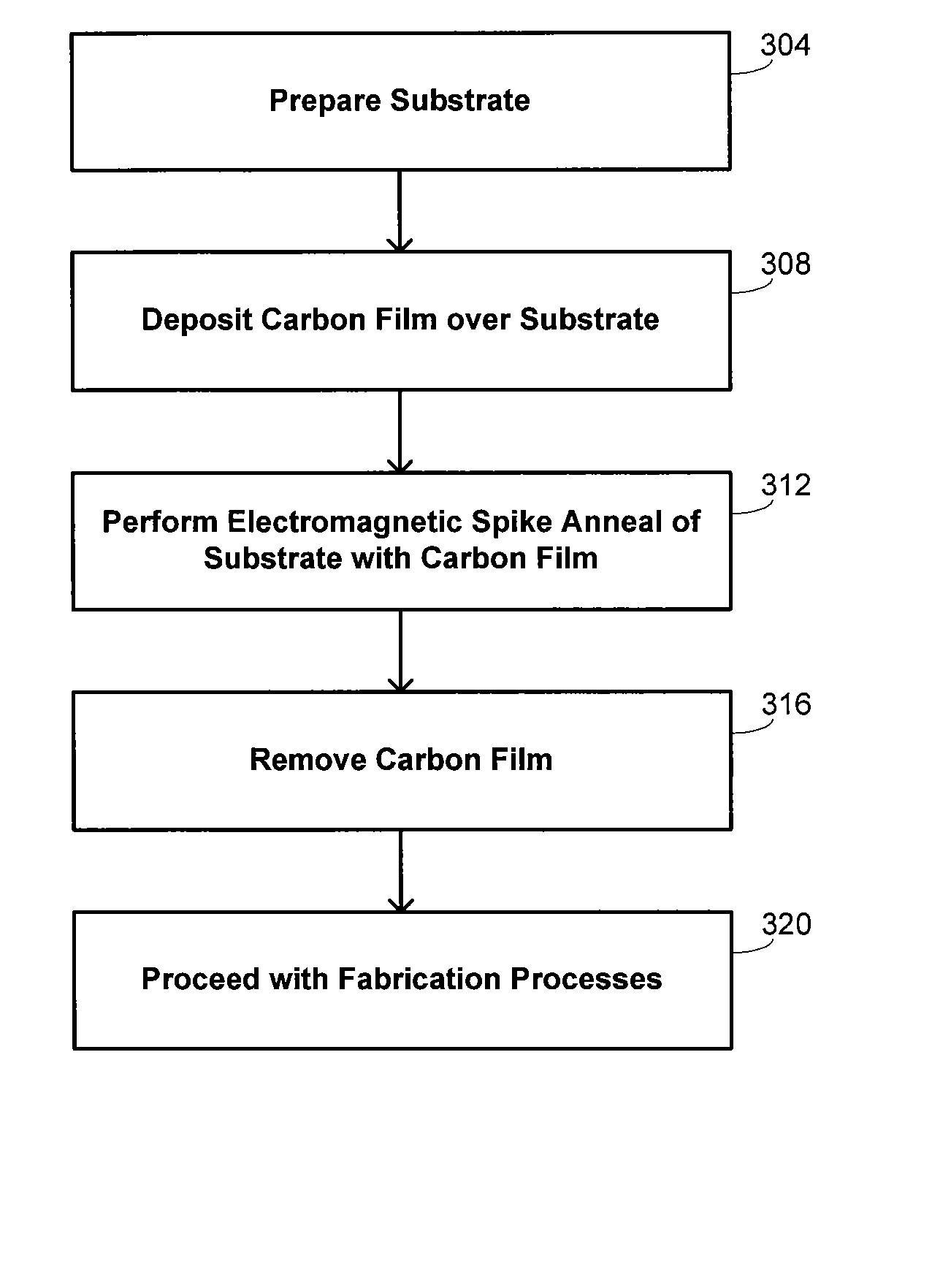

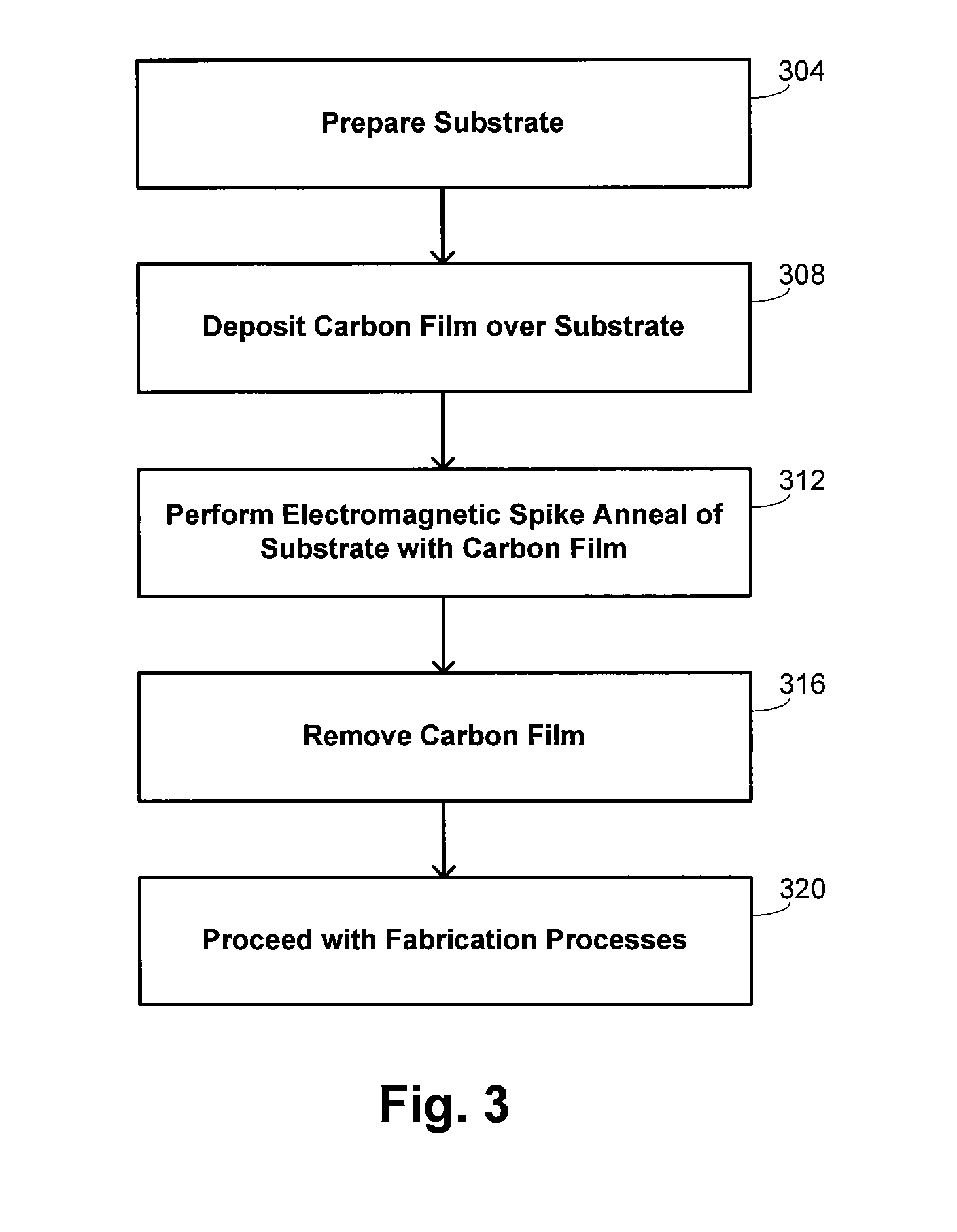

Dopant activation in doped semiconductor substrates

InactiveUS20080057740A1Maintain temperatureSemiconductor/solid-state device manufacturingCarbon filmElectromagnetic radiation

Methods are disclosed for activating dopants in a doped semiconductor substrate. A carbon precursor is flowed into a substrate processing chamber within which the doped semiconductor substrate is disposed. A plasma is formed from the carbon precursor in the substrate processing chamber. A carbon film is deposited over the substrate with the plasma. A temperature of the substrate is maintained while depositing the carbon film less than 500° C. The deposited carbon film is exposed to electromagnetic radiation for a period less than 10 ms, and has an extinction coefficient greater than 0.3 at a wavelength comprised by the electromagnetic radiation.

Owner:APPLIED MATERIALS INC

Method and apparatus for controlled thermal processing

ActiveUS8021898B2Drying solid materials with heatSemiconductor/solid-state device testing/measurementEmissivityMeasurement device

A materials processing system comprises a thermal processing chamber including a heating source, a first noncontacting thermal measurement device positioned to measure temperature on a first area of the material being processed, and, a second noncontacting thermal measurement device positioned to measure temperature on a second area of the material being processed, the first device being relatively more sensitive to changes in surface emissivity than the second device. By comparing the outputs of the two devices, emissivity changes can be detected and used as a proxy for some physical change in the workpiece and thereby determine when the desired process has been completed. The system may be used to develop a process recipe, or it may be part of a system for real-time process control based on emissivity changes. Applicable processes include heating, annealing, dopant activation, silicide formation, carburization, nitridation, sintering, oxidation, vapor deposition, metallization, and plating.

Owner:APPLIED MATERIALS INC

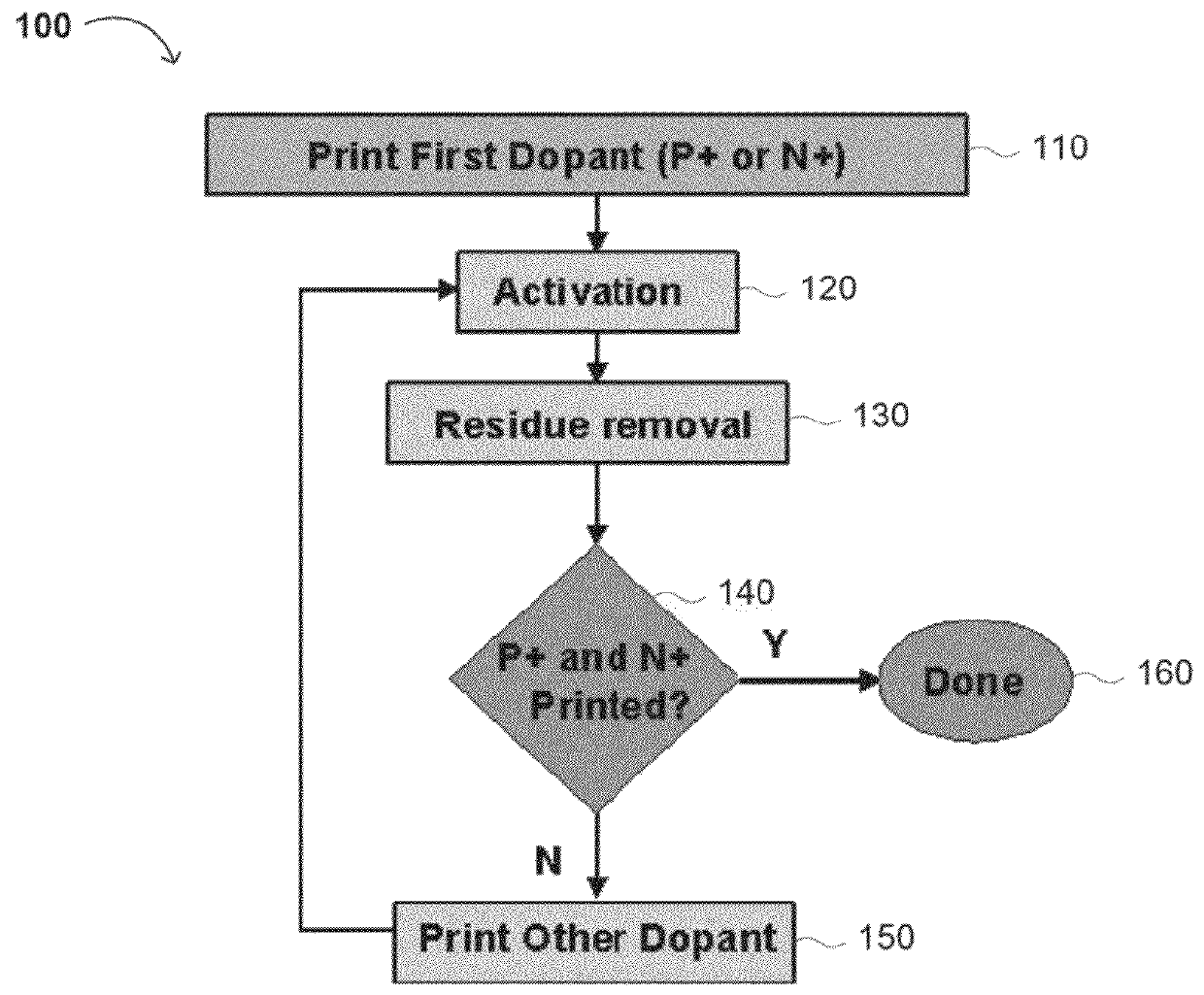

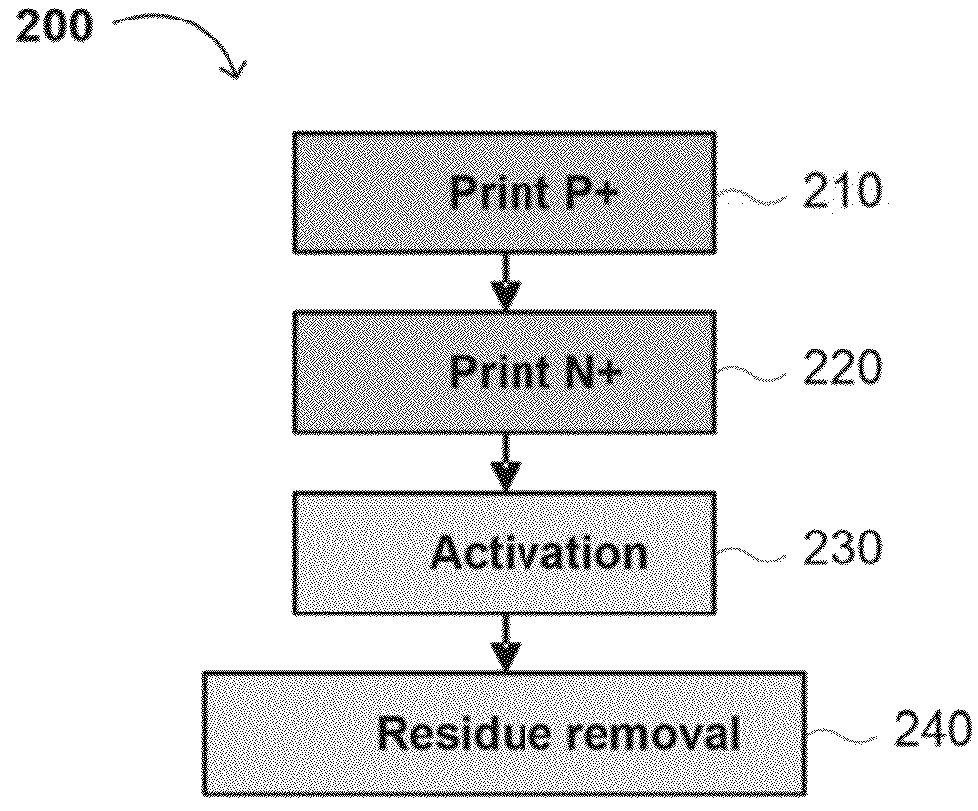

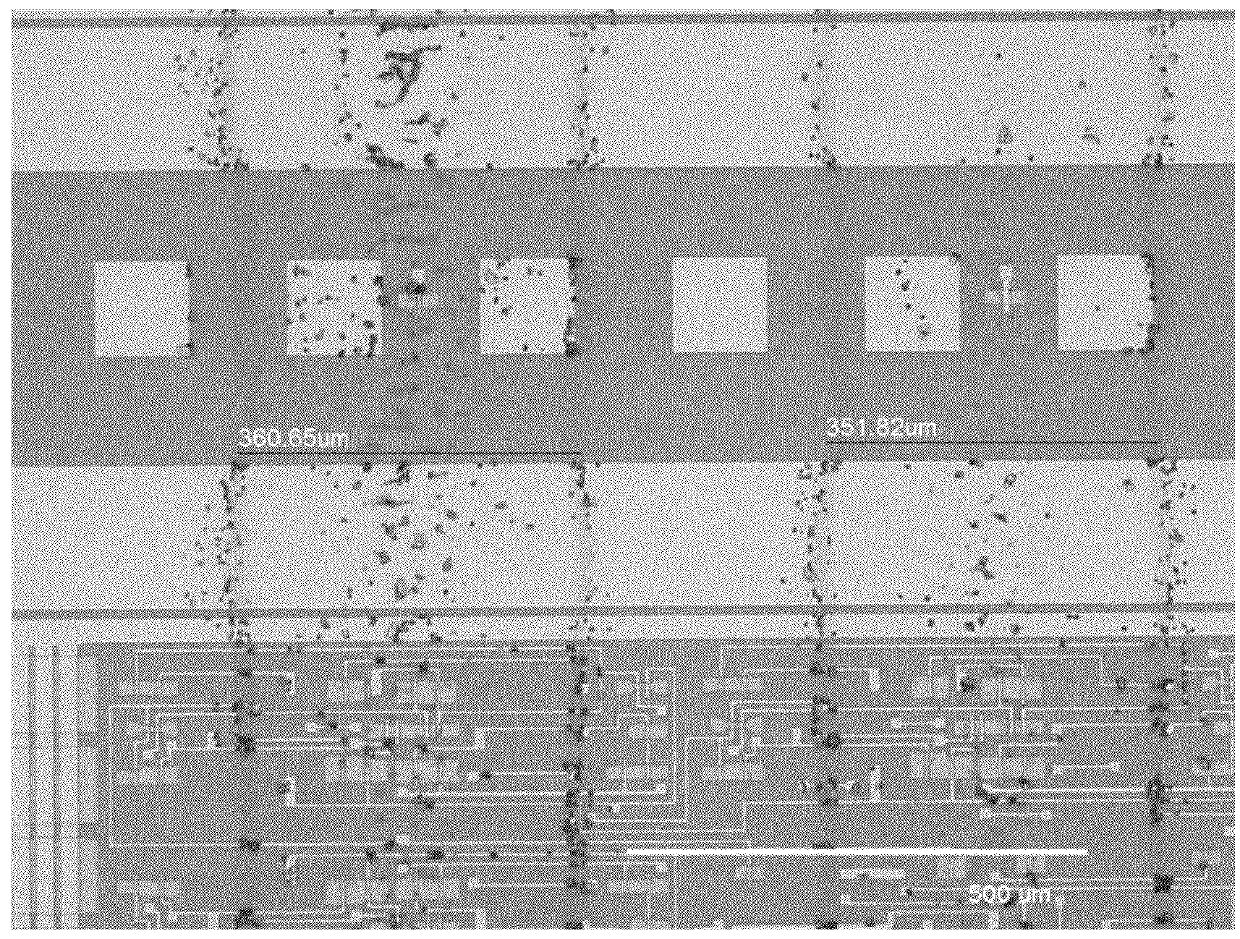

Dopant inks, methods of making dopant inks, and methods of using dopant inks

ActiveUS9359513B1Suitable viscosityPreventing undesirable line and pattern distortionInksIon exchangeDopant Activation

Printable dopant formulations, methods of making such dopant formulations, and methods of using such dopant formulations are disclosed. The dopant formulations provide a printable dopant ink with a viscosity sufficient to prevent ink spreading when deposited in a pattern on a substrate. Furthermore, an ion exchange purification process provides the dopant formulation with a reduced metal ion concentration, and thus a relatively high purity level. Consequently, the dopant residue remaining on the substrate after curing and / or dopant activation process is relatively uniform, and therefore can be easily removed.

Owner:ENSURGE MICROPOWER ASA

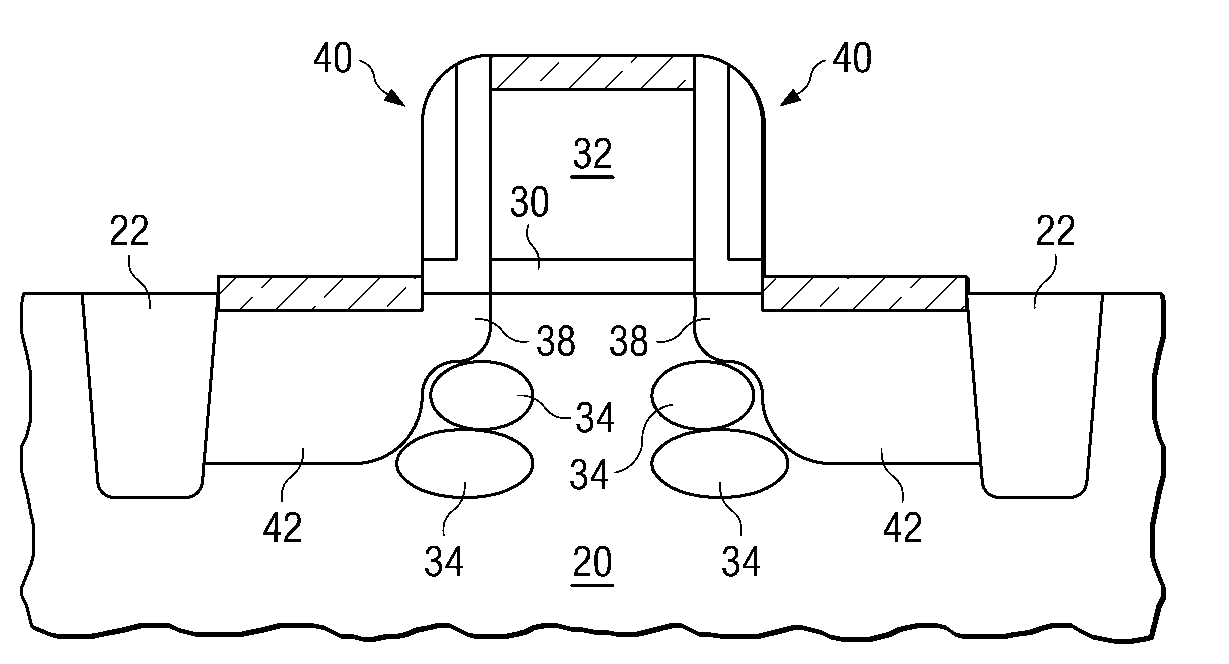

Low-temperature post-dopant activation process

InactiveUS6902966B2Reduces dopant deactivationReduce inactivationMaterial nanotechnologySemiconductor/solid-state device manufacturingMOSFETGate oxide

A method of manufacturing a MOSFET semiconductor device comprises forming a gate electrode over a substrate and a gate oxide between the gate electrode and the substrate; forming source / drain extensions in the substrate; forming first and second sidewall spacers; implanting dopants within the substrate to form source / drain regions in the substrate adjacent to the sidewalls spacers; laser thermal annealing to activate the source / drain regions; depositing a layer of nickel over the source / drain regions; and annealing to form a nickel silicide layer disposed on the source / drain regions. The source / drain extensions and sidewall spacers are adjacent to the gate electrode. The source / drain extensions can have a depth of about 50 to 300 angstroms, and the source / drain regions can have a depth of about 400 to 1000 angstroms. The annealing is at temperatures from about 350 to 500° C.

Owner:ADVANCED MICRO DEVICES INC