System and method for detecting defects in semiconductor wafers

a technology of semiconductor wafers and defect delineation, which is applied in the direction of optics, optical radiation measurement, instruments, etc., can solve the problems of incomplete manufacturing process, defects still created in wafers, and full area of wafers, and achieves non-destructive, cheap, and rapid

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

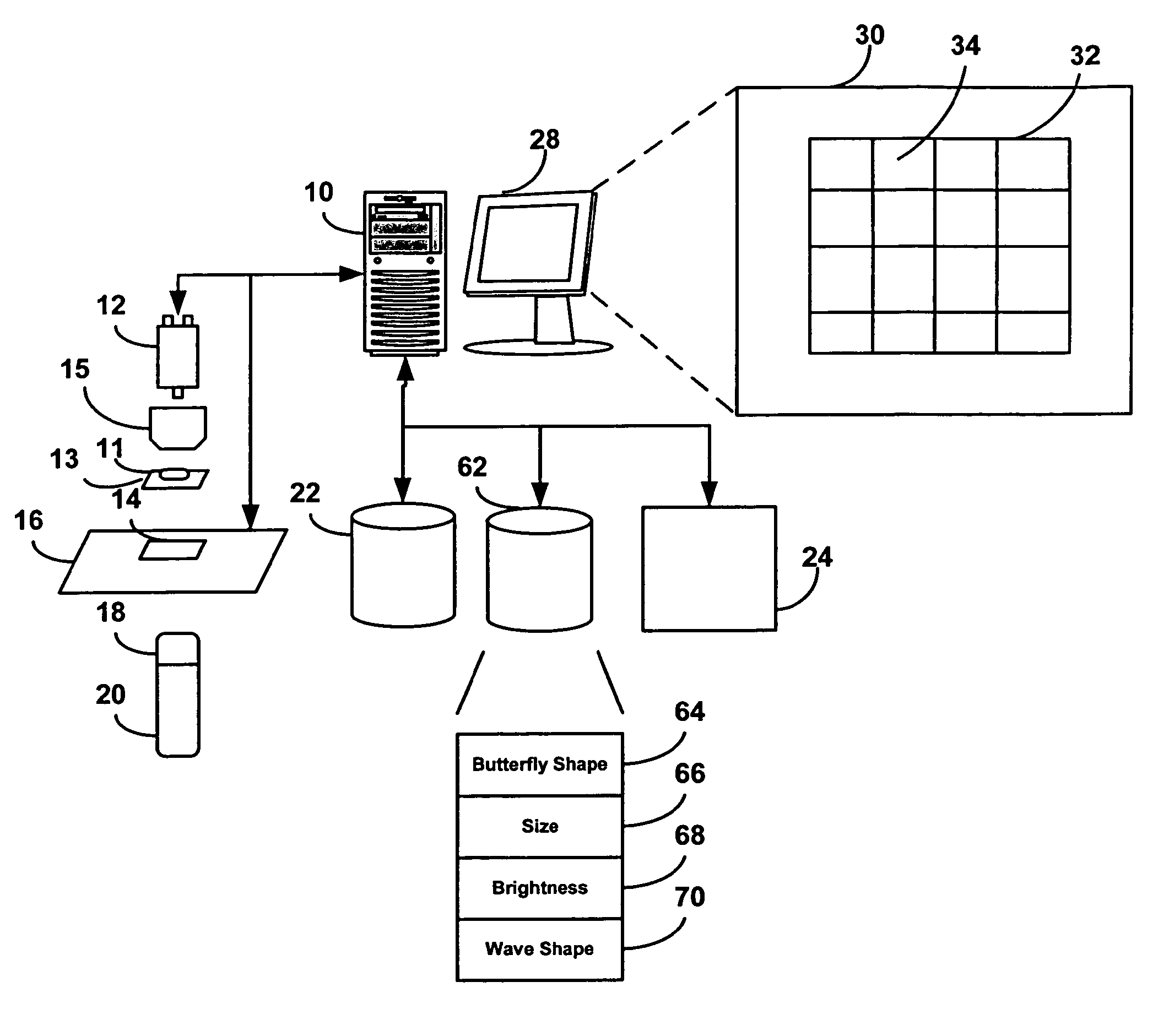

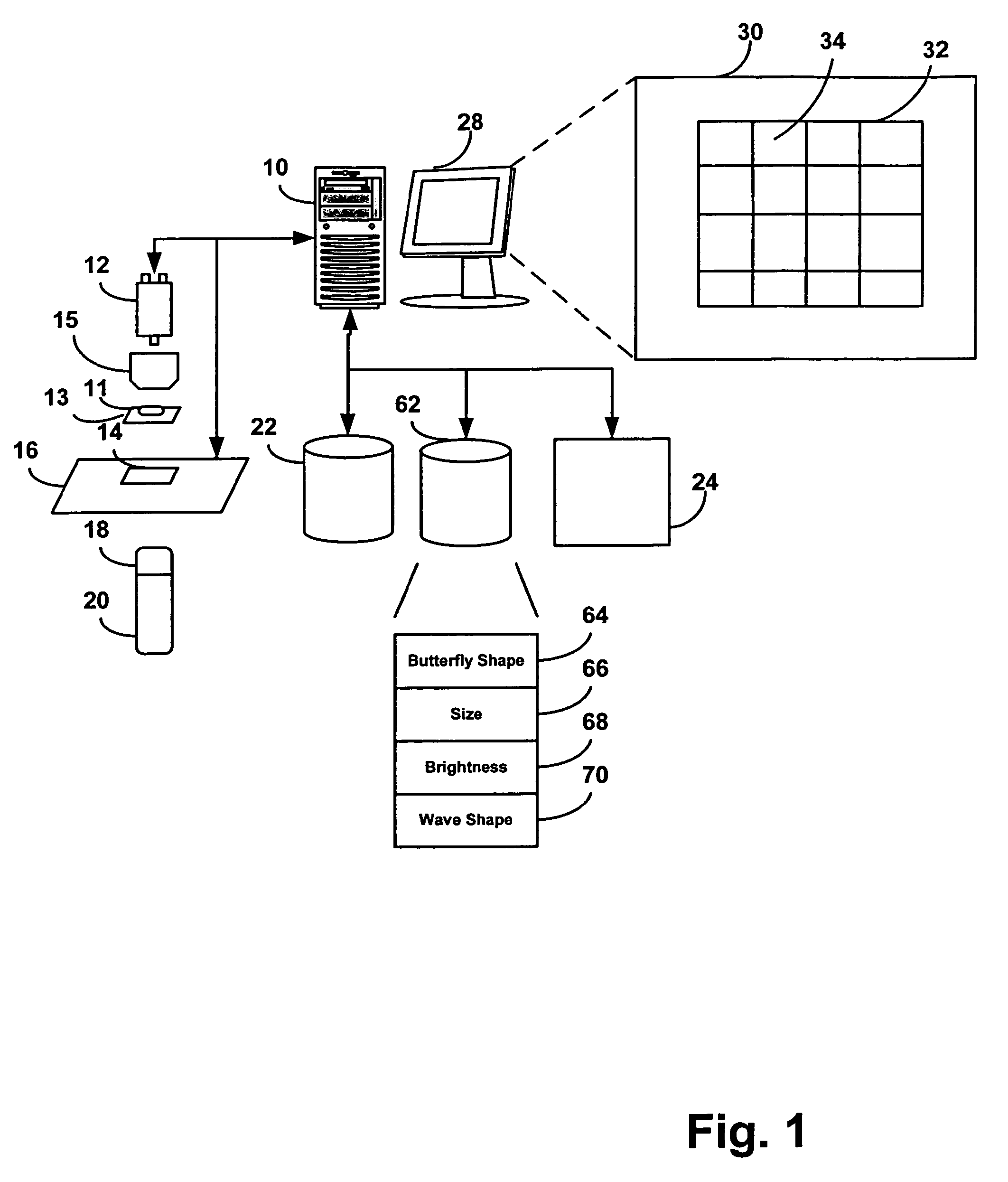

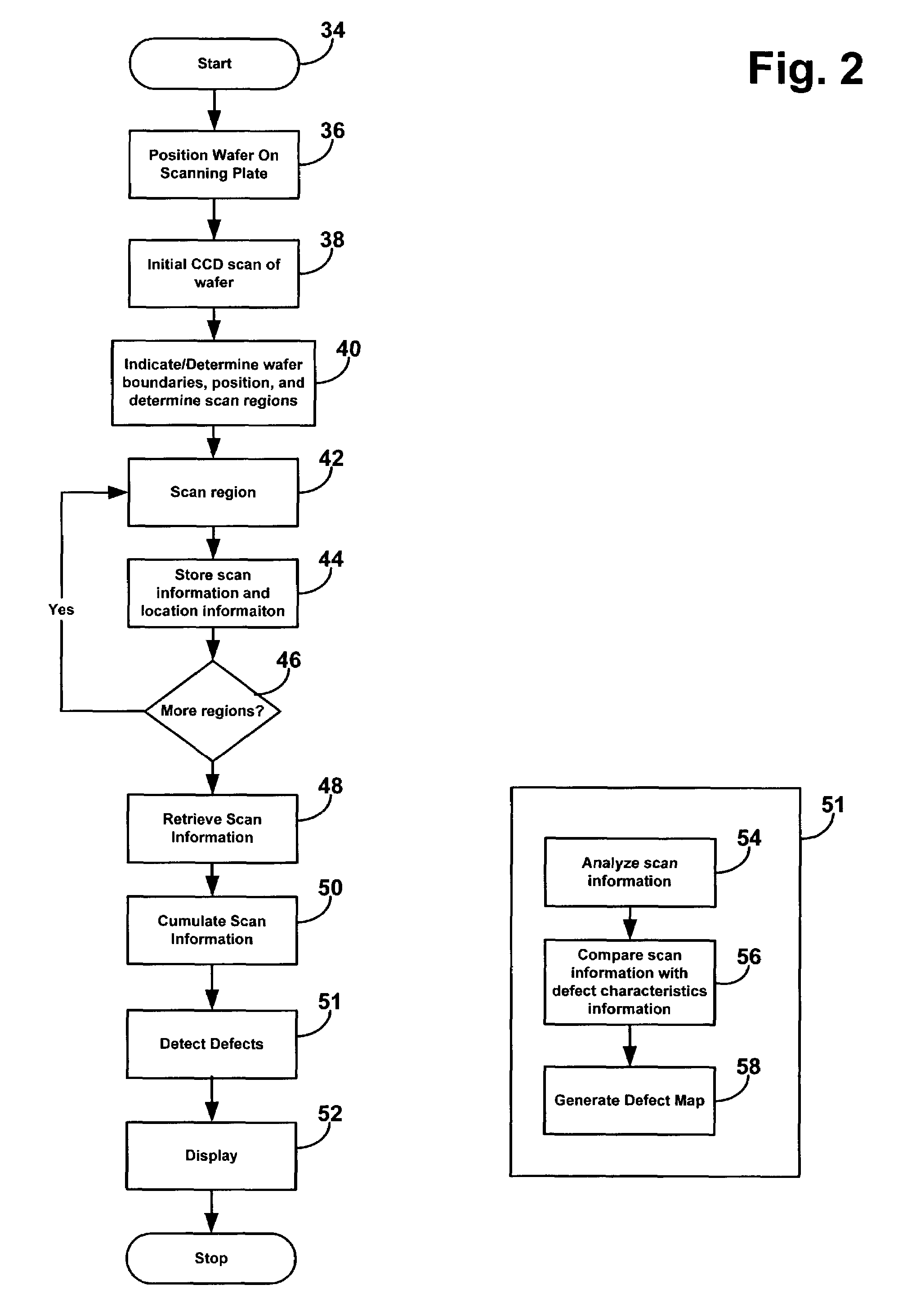

[0016]The detailed description that follows may be presented in terms of program procedures executed on a computer or network of computers. These procedural descriptions are representations used by those skilled in the art to most effectively convey the substance of their work to others skilled in the art. These procedures herein described are generally a self-consistent sequence of steps leading to a desired result. These steps require physical manipulations of physical quantities such as electrical or magnetic signals capable of being stored, transferred, combined, compared, or otherwise manipulated computer readable medium that is designed to perform a specific task or tasks. Actual computer or executable code or computer readable code may not be contained within one file or one storage medium but may span several computers or storage mediums. The term “host” and “server” may be hardware, software, or combination of hardware and software that provides the functionality described ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More