Delay circuit device

a delay circuit and circuit technology, applied in the direction of generating/distributing signals, pulse techniques, instruments, etc., can solve the problems of degrading the accuracy of controlled frequency and increasing power consumption, and achieve the effects of reducing power consumption, reducing power consumption, and reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

The First Embodiment

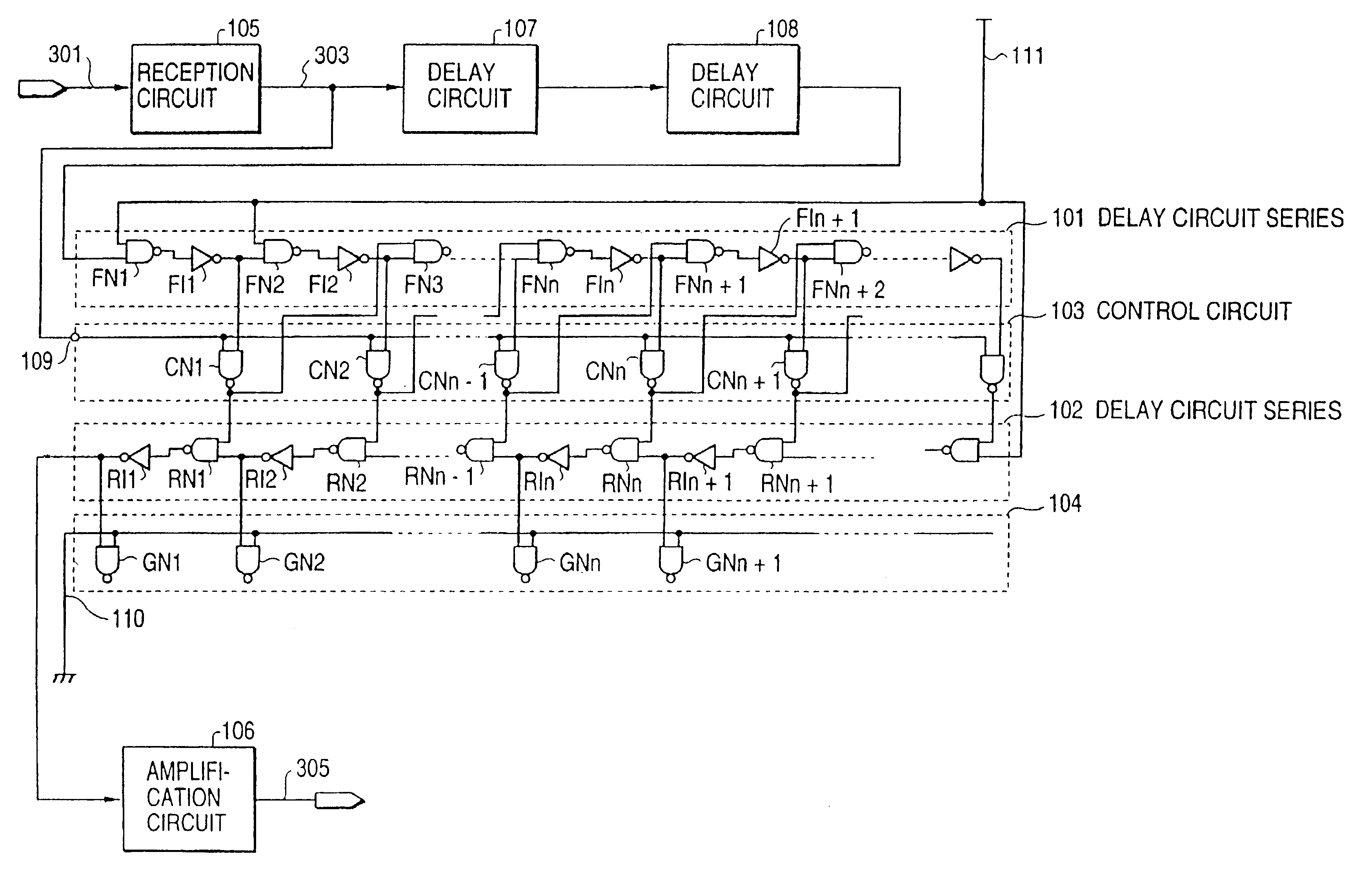

FIGS. 5 and 6 show the first embodiment of the present invention.

Referring to FIG. 5, the present embodiment is made up of a delay circuit series 101 that can extract output from an arbitrary position of a signal transfer path, a delay circuit series 102 that can input from an arbitrary position of a signal transfer path, a control circuit 103 having a signal input terminal and output terminal and an input / output control terminal 109, a load regulation element 104 for leveling the load of delay circuit series 101 and delay circuit series 102, a reception circuit 105 that receives external signals, an amplification circuit 106, a delay circuit 107 having a delay time equal to reception circuit 105, and a delay circuit 108 having a delay time equal to amplification circuit 106. The output 303 of reception circuit 105 is connected to the input of delay circuit 107 and control terminal 109. The output 303 of delay circuit 107 is connected to the input of delay circui...

second embodiment

The Second Embodiment

The second embodiment of the present invention will next be explained with reference to FIG. 7.

As shown in FIG. 7, this embodiment is configured by adding to the delay circuit device of FIG. 5 a delay circuit 112 that allows selection of a plurality of delay times according to a plurality of control signals, and a delay circuit 113 having equivalent composition delay circuit 112, delay circuit 112 being arranged in a series with the input path of delay circuit series 101, delay circuit 113 being arranged in a series with the output path of delay circuit series 102, and the delay times of delay circuit 112 and delay circuit 113 being controlled so as to be equal.

The operation of this embodiment will next be explained.

The operation of this embodiment is basically equivalent to that of the first embodiment with the difference that the regulation of the delay time dV of delay circuit 112 and delay circuit 113 has been added. Explanation will therefore first be given...

third embodiment

The Third Embodiment

The third embodiment of the present invention will next be explained with reference to FIG. 8.

As shown in FIG. 8, this embodiment involves adding to the delay circuit device of FIG. 5 an inverter 114 that inverts input of amplification circuit 106, the embodiment differing from the first embodiment in that sum of the delay times of delay circuit 107 and delay circuit 108 is set to a time that is shorter than the sum of the delay time of reception circuit 105 and the delay time of amplification circuit 106 by the pulse width of clock 301.

The operation of this embodiment is basically equivalent to that of the first embodiment. However, while an H pulse is inverted to an L pulse when a pulse is transmitted from delay circuit series delay circuit series 102 in the first embodiment, in this embodiment, the L pulse is reinverted to an H pulse and outputted. Because the present embodiment also employs the leading edge of the outputted H pulse, regulation of the pulse wi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More