A digital phase lock loop device for smooth switching of clock phase and its method

A digital phase-locked loop and clock phase technology, applied in the field of communication, can solve problems such as phase steps, and achieve the effects of improving detection accuracy, reliability and integration, and simple circuit structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The technical solutions of the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

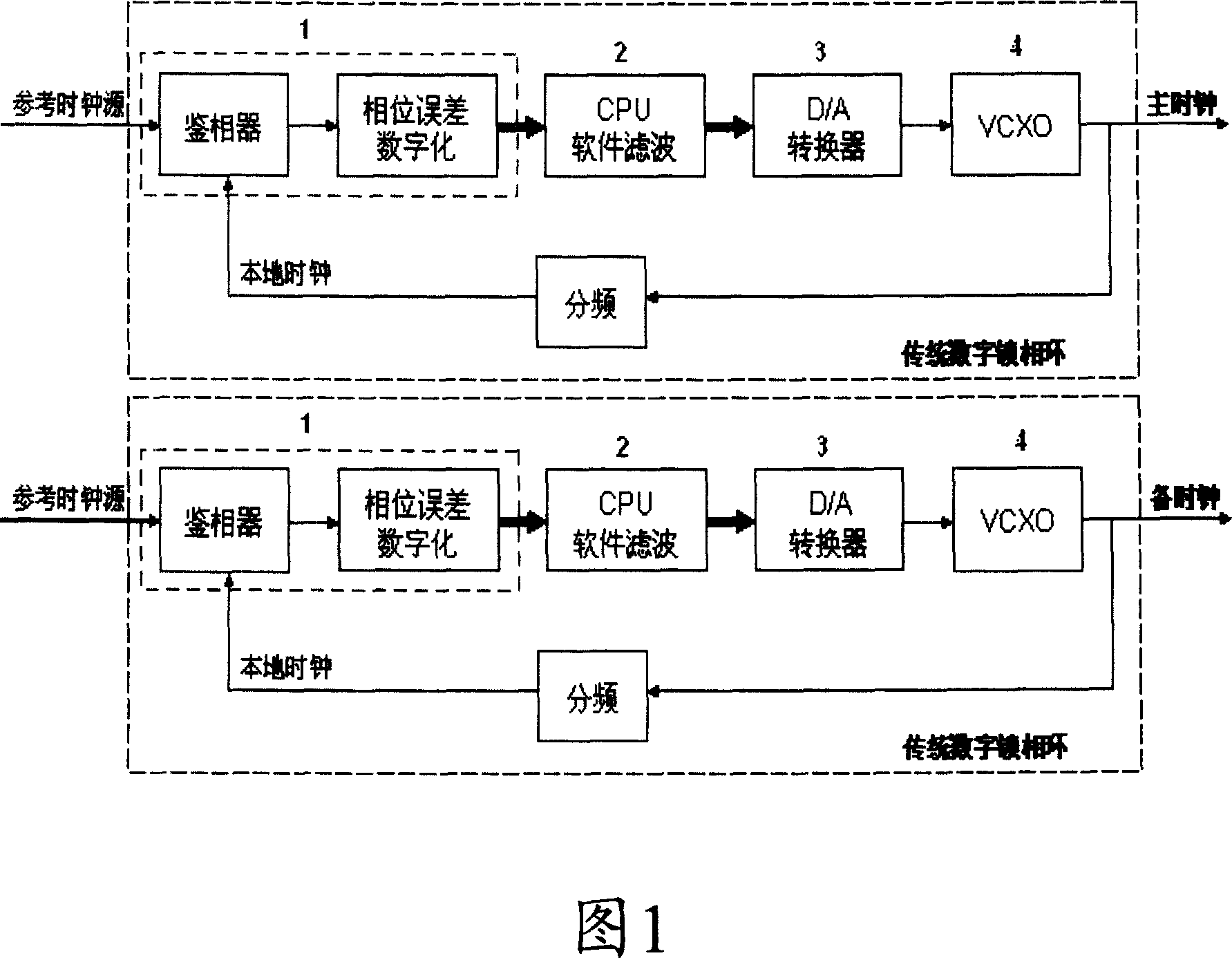

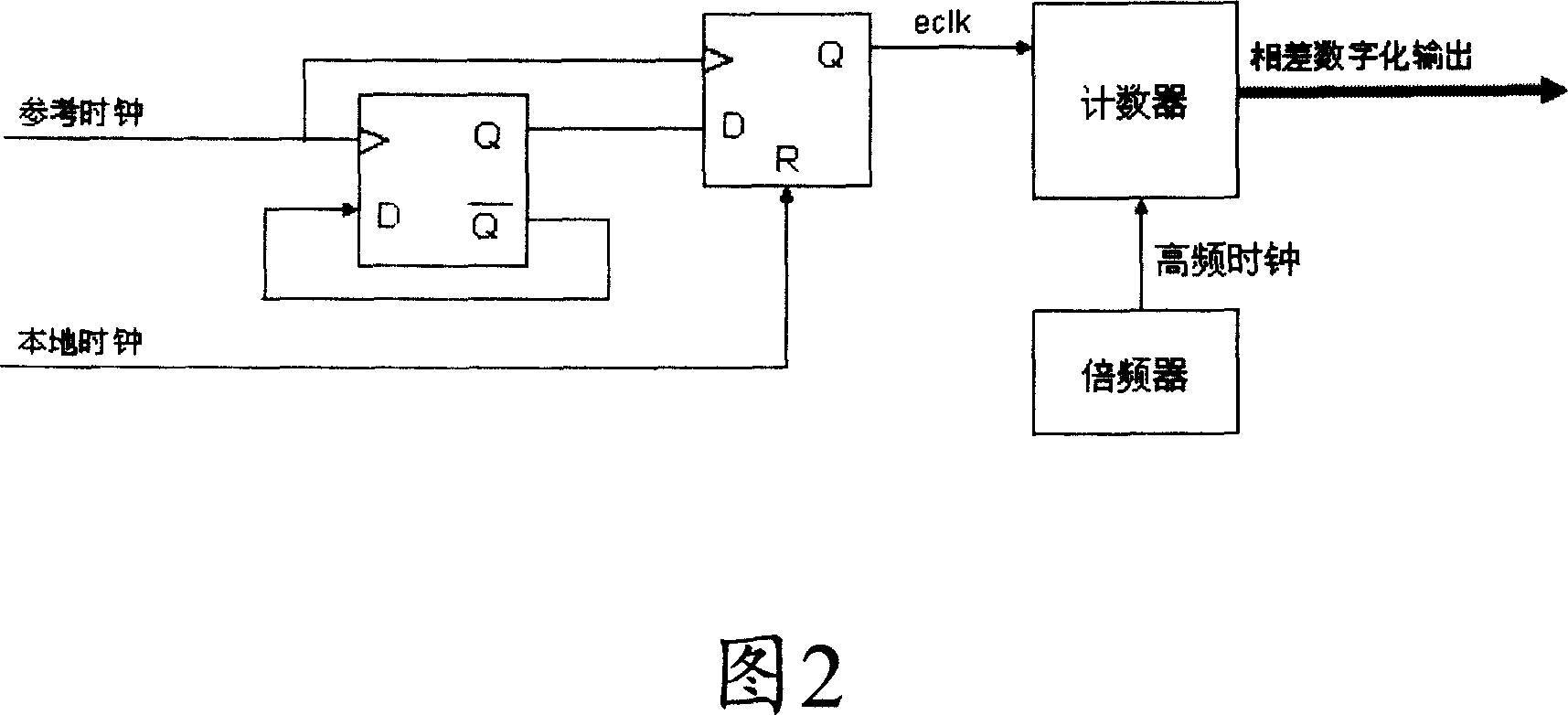

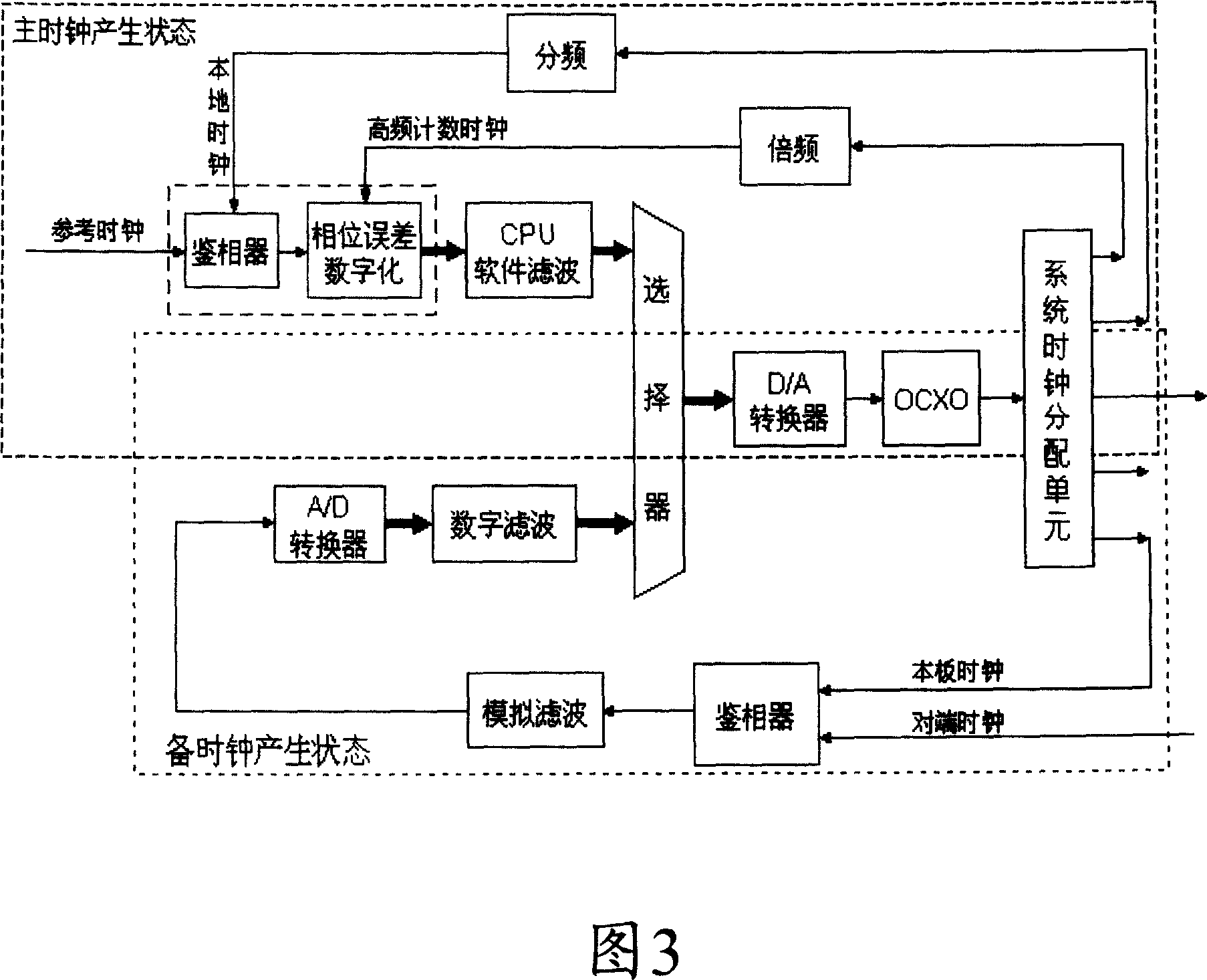

[0044]The invention mainly relates to a control technology for smooth switching of clock phases in a communication system, and adopts a DPLL (Digital Phase Locked Loop) to realize smooth switching under interlocking of main and standby clocks. The present invention provides a phase-locked loop device based on a new type of digital phase-locked loop for smooth switchover of active and standby clocks. The phase detector of the digital phase-locked loop is realized by a sampling time-to-digital converter TDC, which can achieve the purpose of frequency discrimination and phase discrimination , and at the same time greatly improve the control accuracy of the phase difference, which can overcome the defects that are difficult to achieve in the existing technology, and solve the problem of a large phase step that oc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More