Semiconductor encapsulation structure and its making process

A packaging process, semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of chip and chip carrier lamination, cracking, chip warping, etc., to improve the chip Warping or even cracking effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] Relevant detailed description and technical contents of the present invention are as follows now in conjunction with the accompanying drawings:

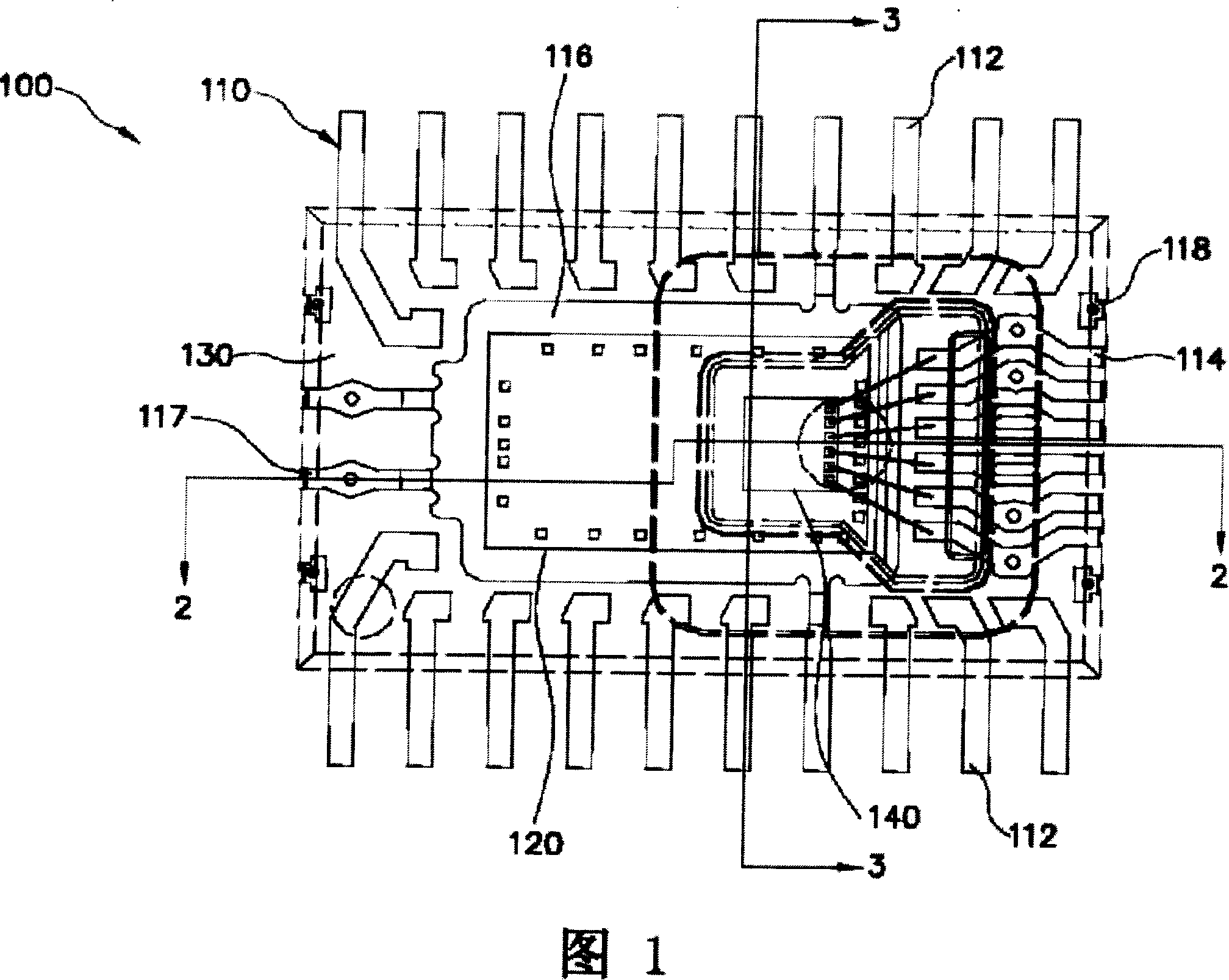

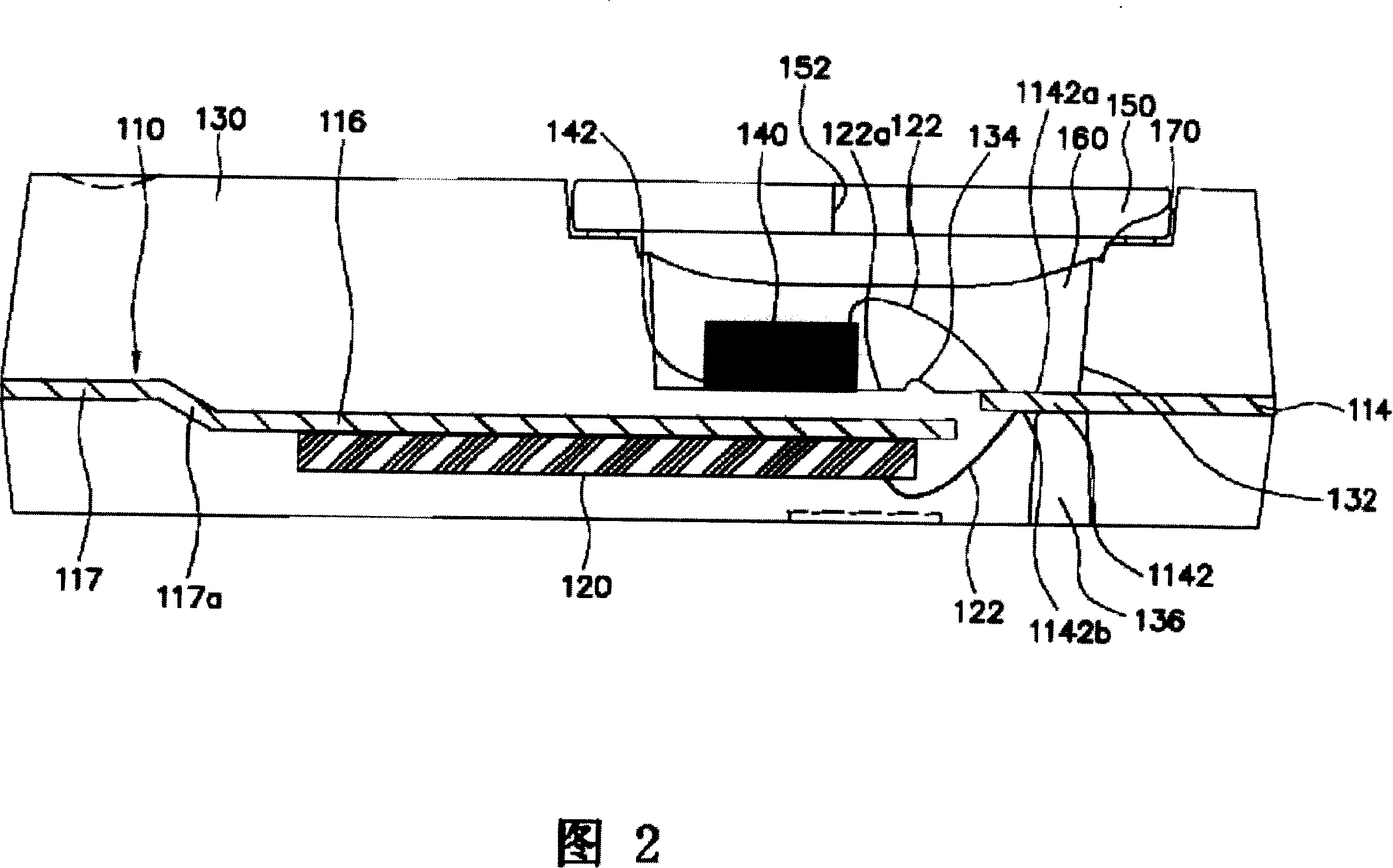

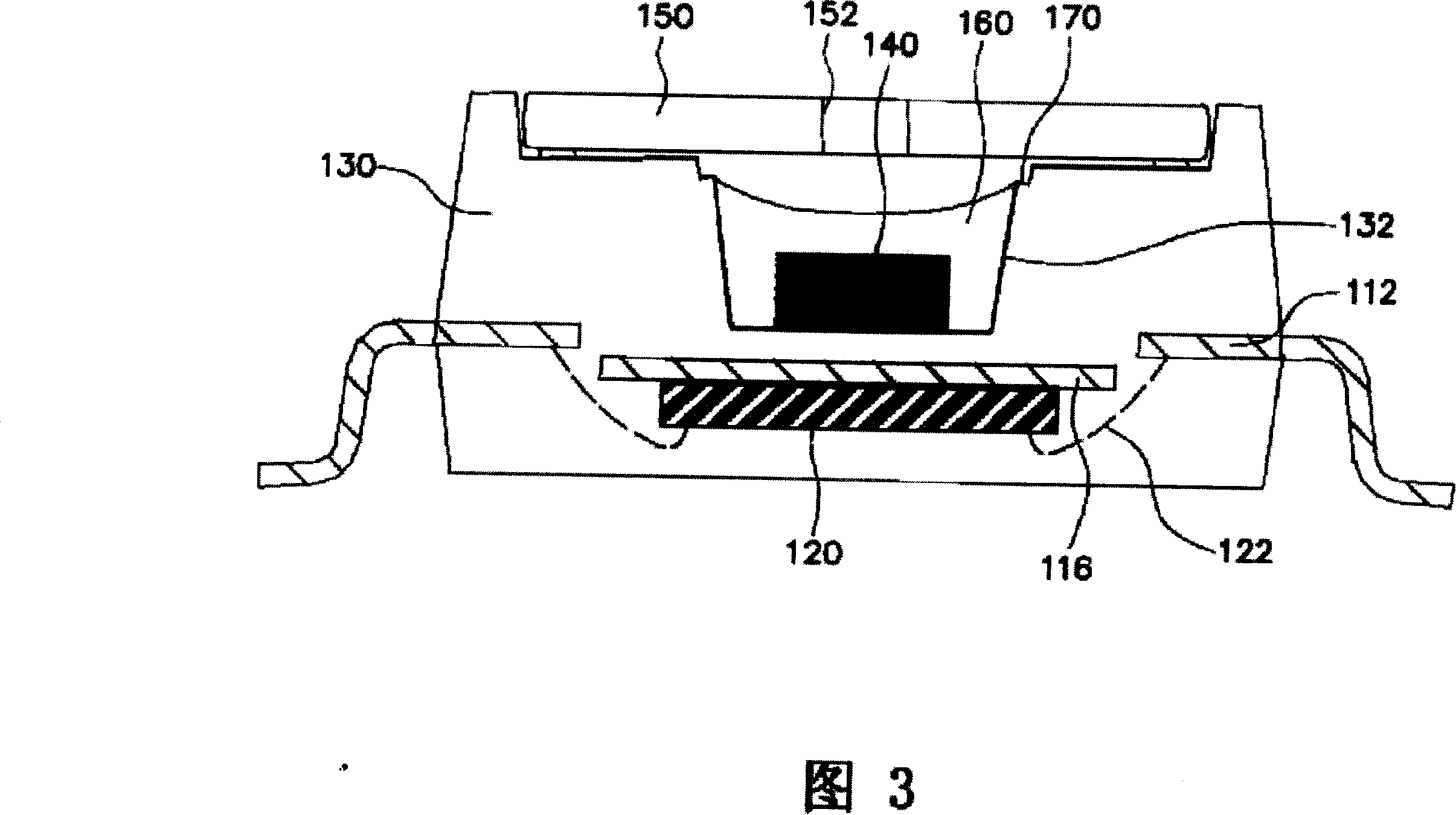

[0015] 1-3 illustrate a semiconductor package structure 100 according to a preferred embodiment of the present invention. FIG. 1 is a top view of the semiconductor package structure 100 . Fig. 2 is a cross-sectional view taken along section line 2-2 in Fig. 1 . Fig. 3 is a sectional view taken along section line 3-3 in Fig. 1 . As shown in FIG. 1 , the semiconductor package structure 100 mainly includes a lead frame 110, a first semiconductor chip 120 wrapped in a first encapsulant 130 (the first encapsulant 130 has a recess 132 for containing Put a second semiconductor chip 140, and a cover 150 (see Fig. 2 and Fig. 3 ) that is located on the recess 132 of the first encapsulant 130. For example, the first semiconductor chip 120 can be a Discrete components, an integrated circuit or a control chip, and the second semiconduct...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More