Method for realizing portion exhaust insulators upper silicon device physical contact

A technology of silicon-on-insulator and body contact, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems that the floating body effect cannot be completely suppressed, the floating body effect cannot be effectively suppressed, and the leakage current is too large, so as to achieve the purpose of suppressing the floating body Effect, low cost, simple process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

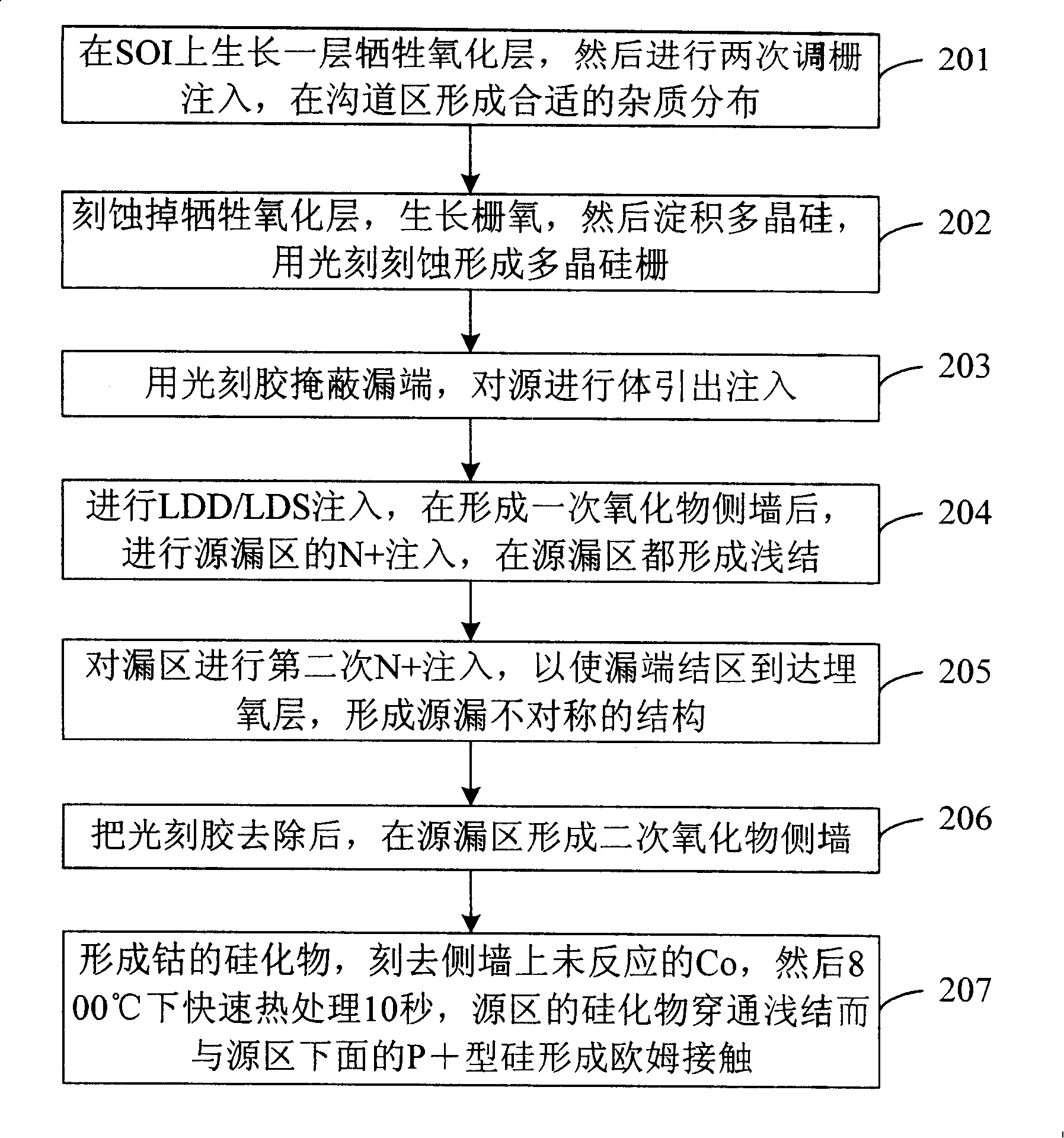

[0046] Such as figure 2 as shown, figure 2 A flowchart of a method for realizing body contact of a partially depleted SOI device according to an embodiment of the present invention, the method includes the following steps:

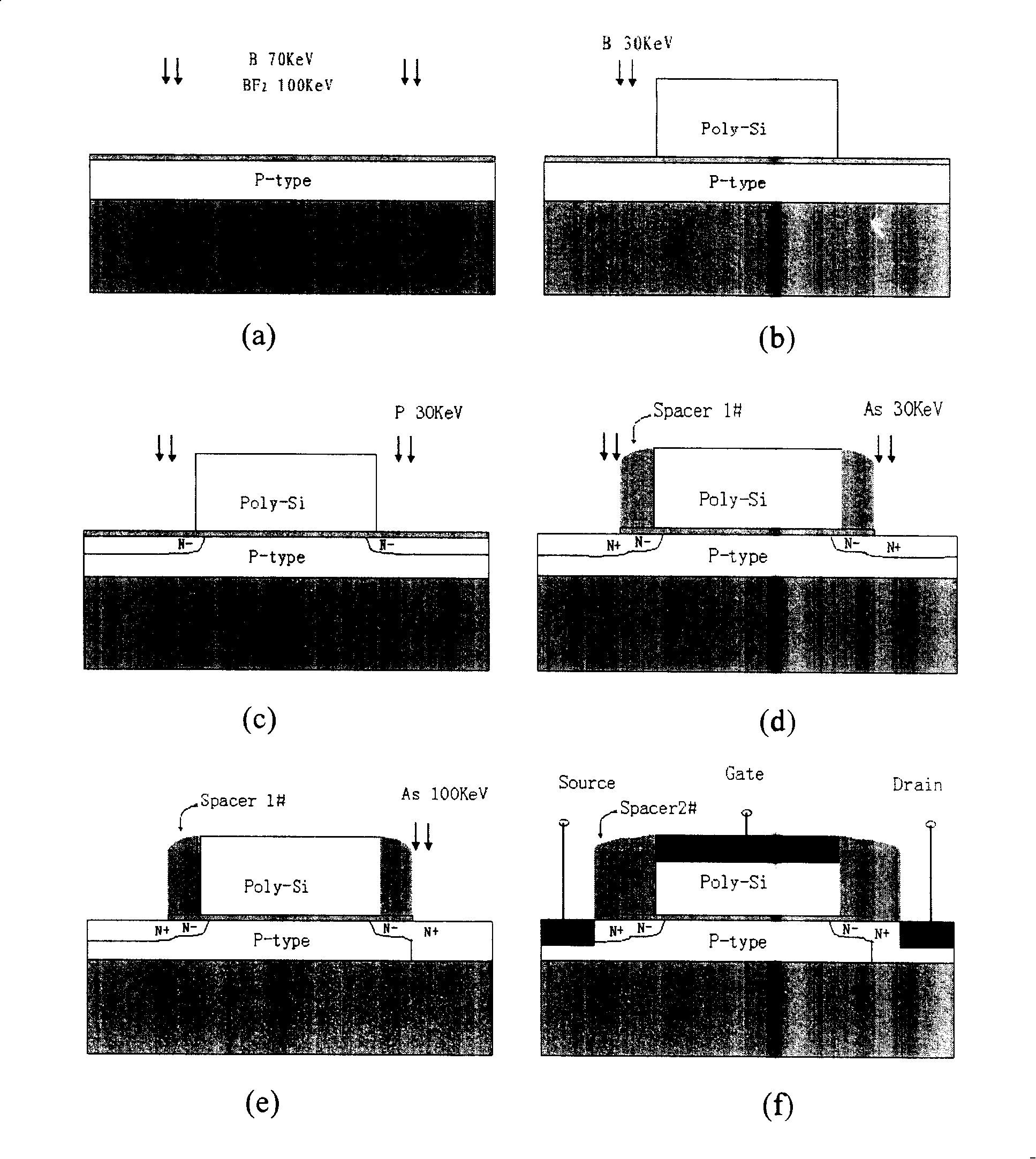

[0047] Step 201: first grow a sacrificial oxide layer on the SOI, and then perform gate adjustment implantation twice to form a proper impurity distribution in the channel region. Such as image 3 Shown in (a).

[0048] Step 202: Etching away the sacrificial oxide layer, growing gate oxide, then depositing polysilicon, and forming a polysilicon gate by photolithography. Such as image 3 Shown in (b).

[0049]Step 203: Mask the drain end with photoresist, and perform body extraction implantation on the source; for example image 3 Shown in (b).

[0050] In this step, high-dose and high-energy boron ion implantation is performed for SOI NMOSFET to form a high-concentration P+ region under the source. For SOI PMOSFETs, high-dose and high-energy phos...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com