Structure and manufacturing method of packaged base plate

A technology for packaging substrates and substrates, which is applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., and can solve problems such as limiting the spacing of metal bumps 15

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

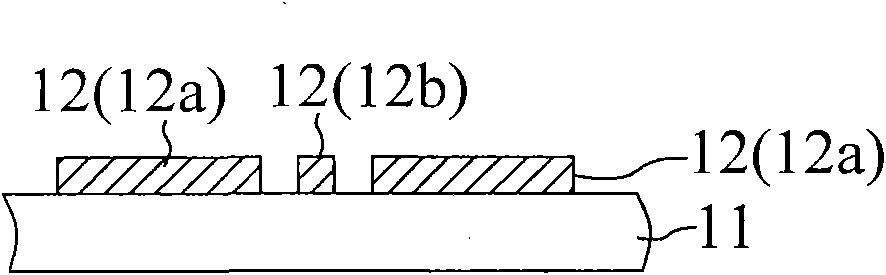

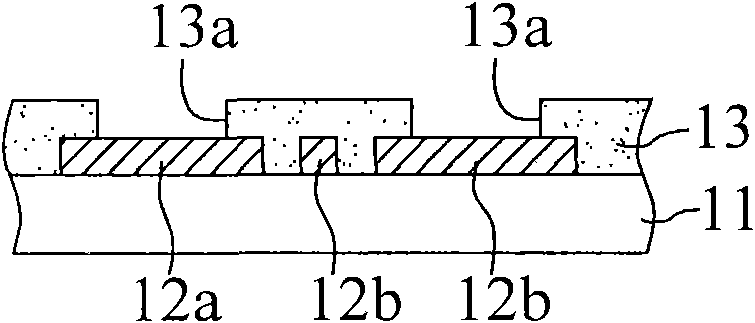

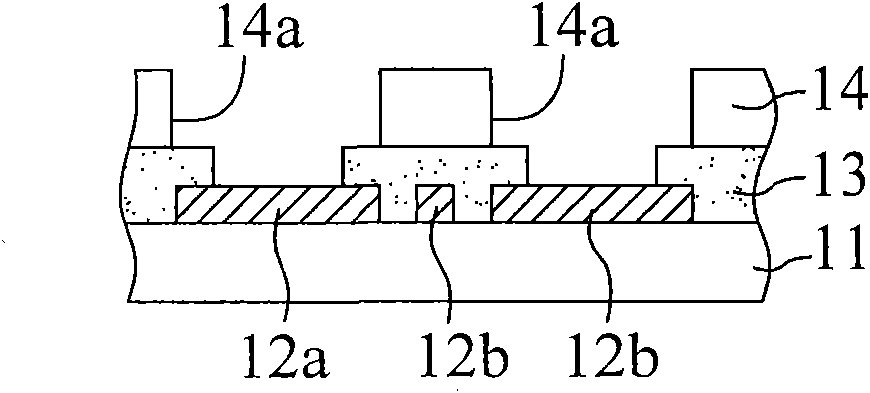

[0041] Figure 4A to Figure 4D It is a schematic cross-sectional view of the manufacturing method of the packaging substrate structure of a preferred embodiment of the present invention, Figure 5A to Figure 5D Its corresponding top view diagram. First, see Figure 4A A packaging substrate 41 is provided, and a patterned metal layer is formed on the surface of the packaging substrate 41 as the circuit layer 42 . In this embodiment, the patterned metal layer is a structure formed by stacking a seed layer and a metal layer on the seed layer. The material of the seed layer and the metal layer used in this embodiment is copper.

[0042] see Figure 4A and Figure 5A The circuit layer 42 includes a plurality of electrical connection pads 42a and circuits 42b. The planar shape of the electrical connection pads 42a is a prolate rectangle, so as to improve the flexibility of circuit layout space.

[0043] Compared with existing packaging substrate structures (see Figure 2A ), th...

Embodiment 2

[0049] Except that the plane shapes of the electrical connection pads and the openings of the solder resist layer are elliptical, the structure and manufacturing method of the packaging substrate of this embodiment are the same as those of the first embodiment. So I won't repeat them here.

[0050] Compared to Example 1 Figure 4B and Figure 5B , Figure 7 It is a three-dimensional schematic view of the packaging substrate structure of this embodiment, including: a substrate body 41 , an electrical connection pad 42 a , a circuit 42 b , a solder resist layer 43 and a solder resist layer opening 43 a. Figure 8 for Figure 7 In the top view of , the plane shapes of the electrical connection pad 42a (indicated by a dotted line) and the solder mask opening 43a are both elliptical.

[0051] Similarly, since the planar shape of the electrical connection pad and the opening of the solder mask layer is flat and long, the flexibility of the circuit layout space can be improved, t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com