Etching and filling method of deep groove isolation structure of silicon-on-insulator

A silicon-on-insulator, isolation structure technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem of inconspicuous transition areas between the silicon layer and the isolation oxide layer, lattice defects, affecting the electrical isolation characteristics of deep grooves, etc. problems, to achieve the effect of increasing the available active area area, reducing the minimum spacing, and increasing the lateral breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

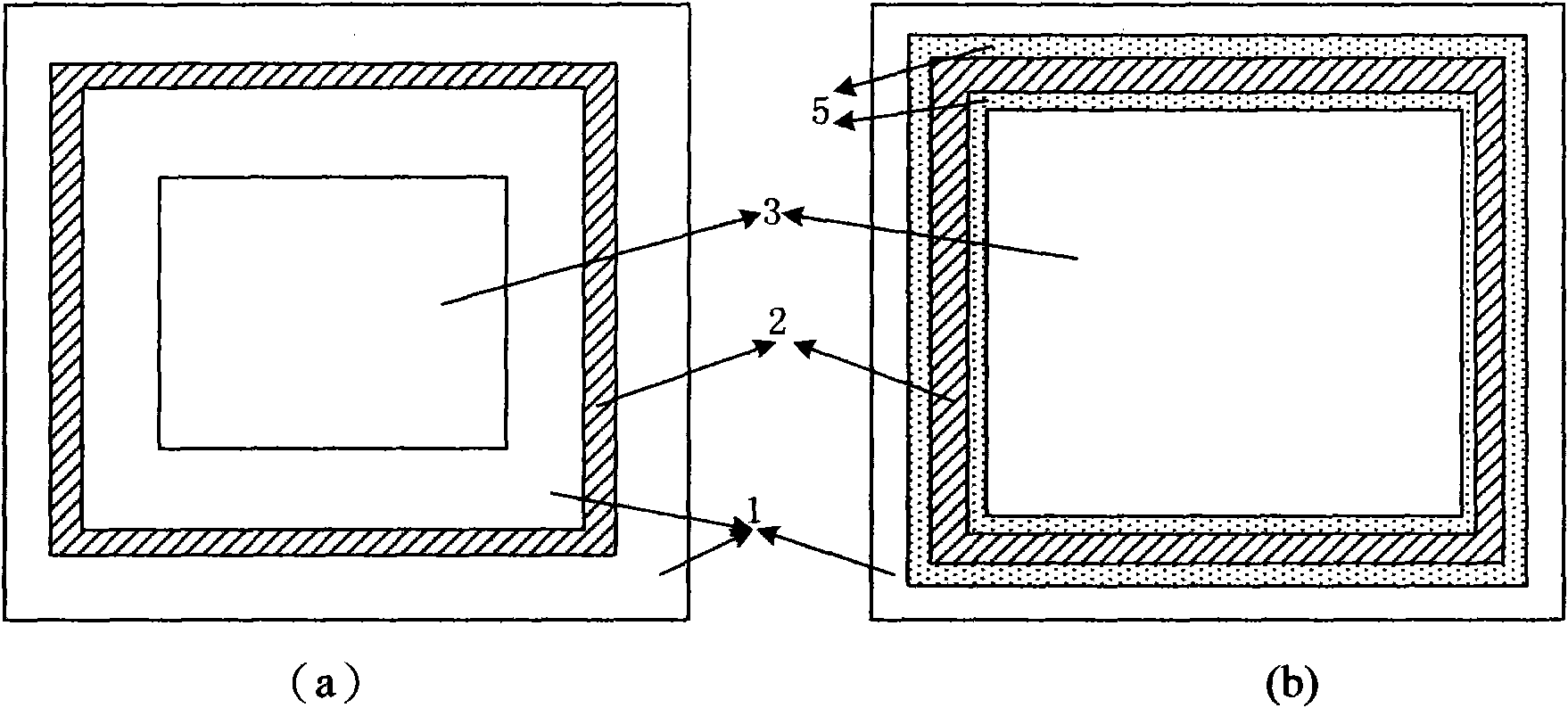

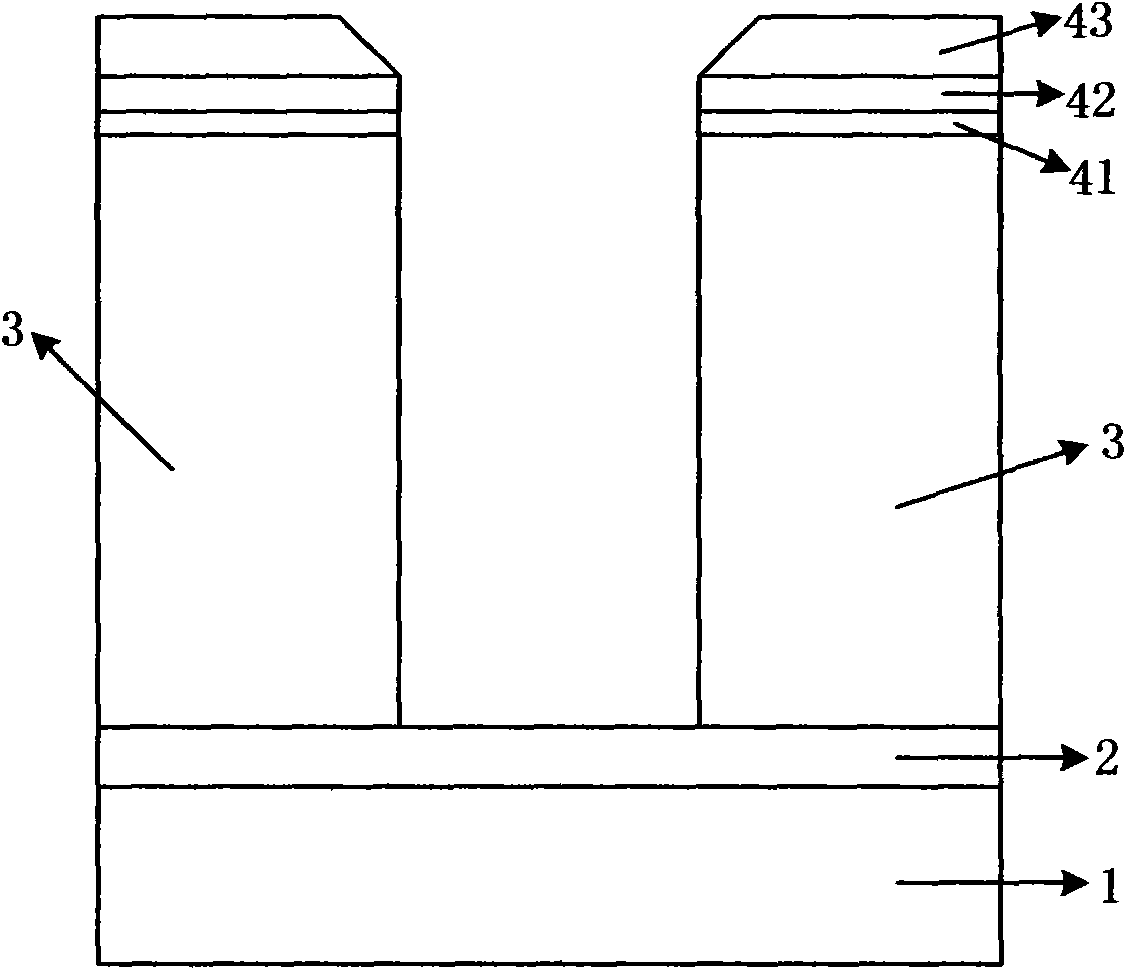

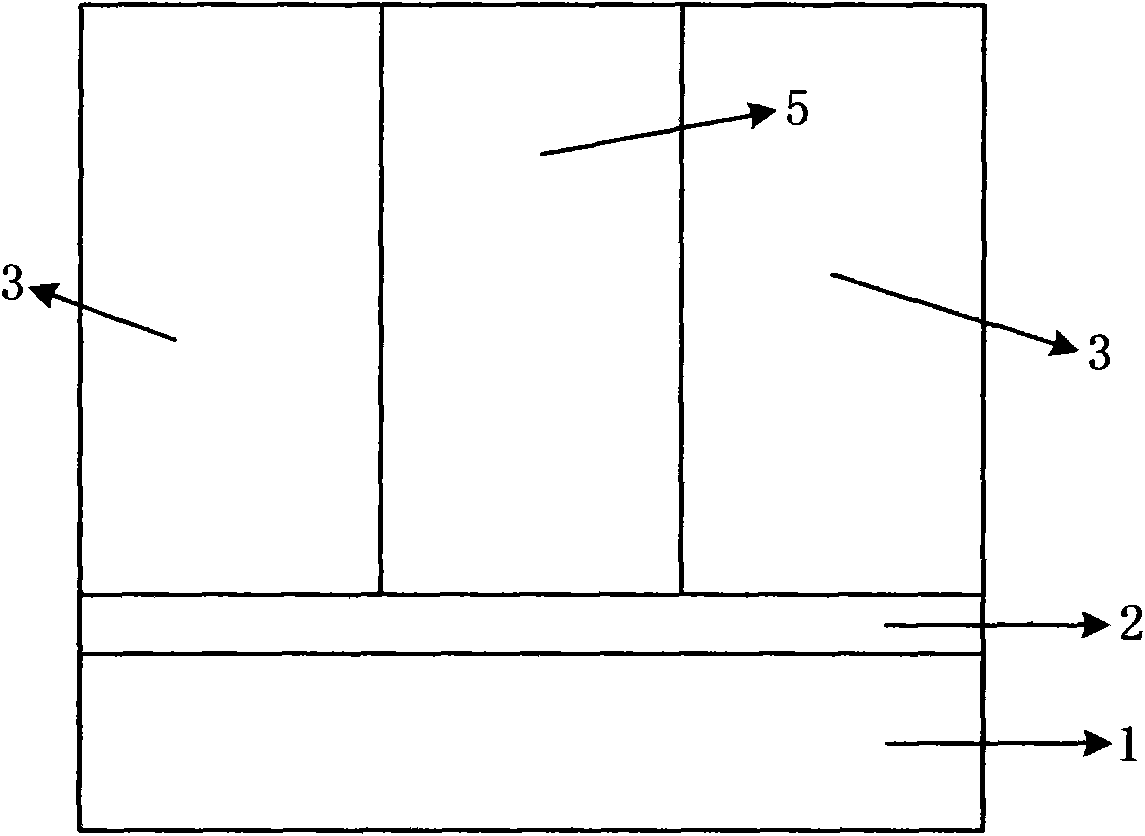

[0024] refer to Figure 6 , a silicon-on-insulator deep trench isolation structure using a new etching and filling method, comprising: a semiconductor substrate 1, a buried oxide layer 2 is arranged on the semiconductor substrate 1, and an N-type The top layer of single crystal silicon 3 is etched from the surface of the N-type top layer of single crystal silicon 3 to the buried oxide layer 2, and then filled with a dielectric, and the side wall surface of the N-type top layer of single crystal silicon 3 is N-type heavily doped The heterogeneous monocrystalline silicon layer 5, on the side surface of the N-type heavily doped monocrystalline silicon layer 5 is an isolation oxide layer 6 thermally grown by wet oxygen method, and polysilicon 7 is filled between the isolation oxide layers 6 on both sides, so that the entire The inside of the deep groove is completely filled with medium.

[0025] The present invention adopts following method to prepare:

[0026] 1. On a silicon-o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More