Thin film transistor liquid crystal display (TFT-LCD) array substrate and manufacturing method thereof

A manufacturing method and technology for array substrates, which are applied in semiconductor/solid-state device manufacturing, optics, instruments, etc., can solve problems such as excessive TFT off-state current, shortened pixel electrode charge retention time, and affect TFT performance, etc. Off-state current, prolonging pixel electrode charge retention time, reducing R&D and production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

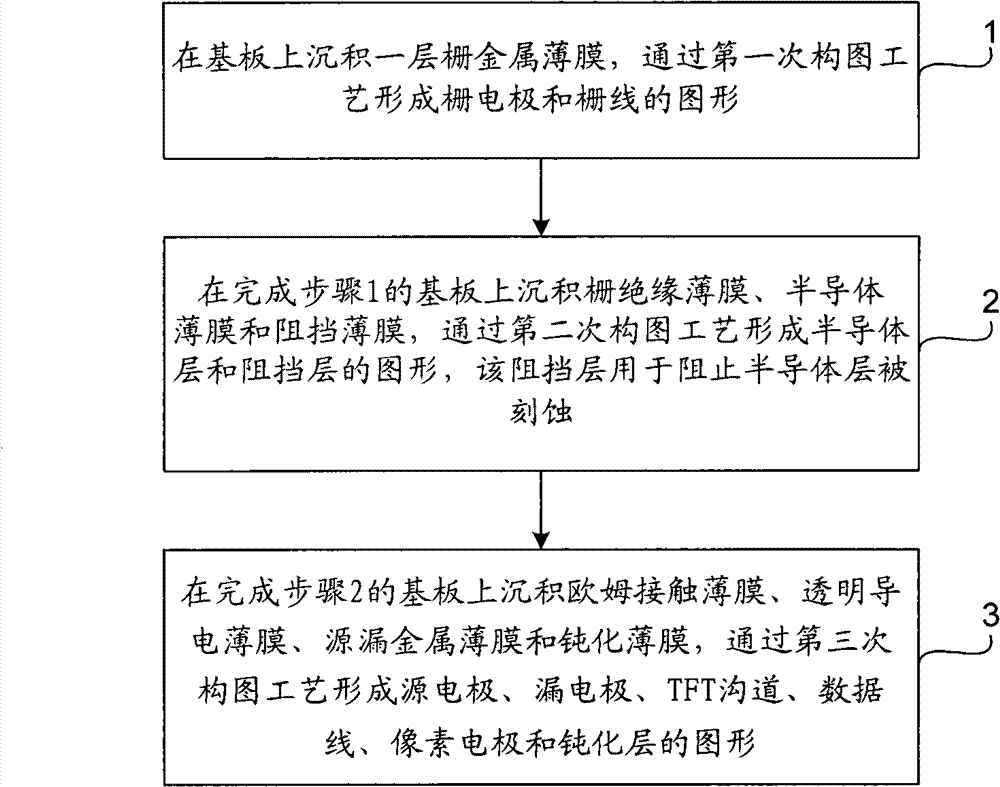

[0027] Such as figure 1 Shown is the flow chart of the TFT-LCD array substrate manufacturing method of the present invention, including:

[0028] Step 1, depositing a layer of gate metal thin film on the substrate, and forming the pattern of gate electrode and gate line through the first patterning process;

[0029] Step 2. Depositing a gate insulating film, a semiconductor film and a barrier film on the substrate completed in step 1, and forming a pattern of the semiconductor layer and the barrier layer through a second patterning process, the barrier layer is used to prevent the semiconductor layer from being etched;

[0030] Step 3. Deposit ohmic contact film, transparent conductive film, source-drain metal film and passivation film on the substrate after step 2, and form source electrode, drain electrode, channel, data line, pixel electrode and Graphics of the passivation layer.

[0031] The specific implementation process of each step is introduced in detail below.

[...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More