Low-power dissipation RS latch unit and low-power dissipation master-slave D flip-flop

A low-power, latch technology, applied in electrical components, pulse generation, electrical pulse generation, etc., can solve problems such as energy consumption, reduce leakage power consumption, affect circuit performance, etc., achieve low power consumption characteristics, save leakage Power consumption, effect of good leakage power suppression performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

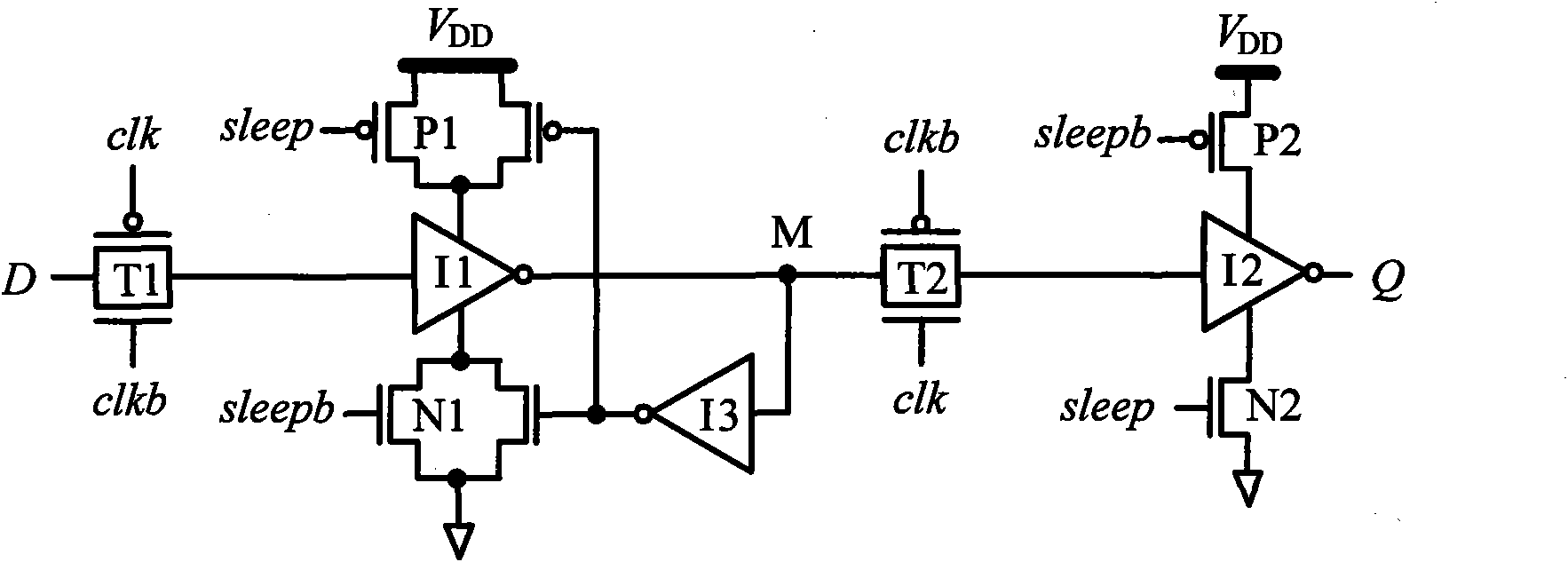

[0023] Embodiment one: if Figure 5 As shown, a low-power RS latch unit includes an input drive and synchronization circuit, a pull-down circuit, a power control circuit, and a first inverter and a second inverter that are cross-coupled to each other. The input drive and synchronization circuit consists of The third PMOS transistor P3, the fourth PMOS transistor P4, the fifth PMOS transistor P5 and the sixth PMOS transistor P6 are composed, the pull-down circuit is composed of the third NMOS transistor N3 and the fourth NMOS transistor N4, and the power control circuit is composed of the fifth NMOS transistor N5 Composition, the first inverter is composed of the first NMOS transistor N1 and the first PMOS transistor P1, the second inverter is composed of the second NMOS transistor N2 and the second PMOS transistor P2, the first PMOS transistor P1 and the second PMOS transistor P2 is a high-threshold PMOS transistor, the third NMOS transistor N3, the fourth NMOS transistor N4...

Embodiment 2

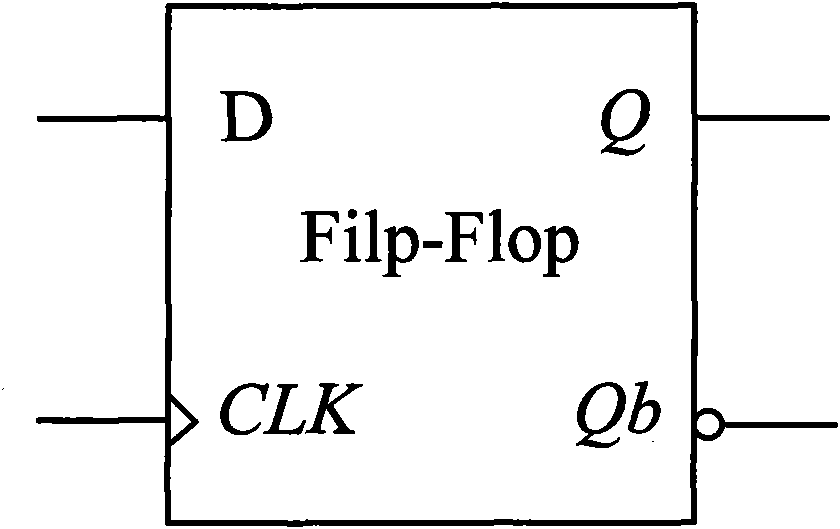

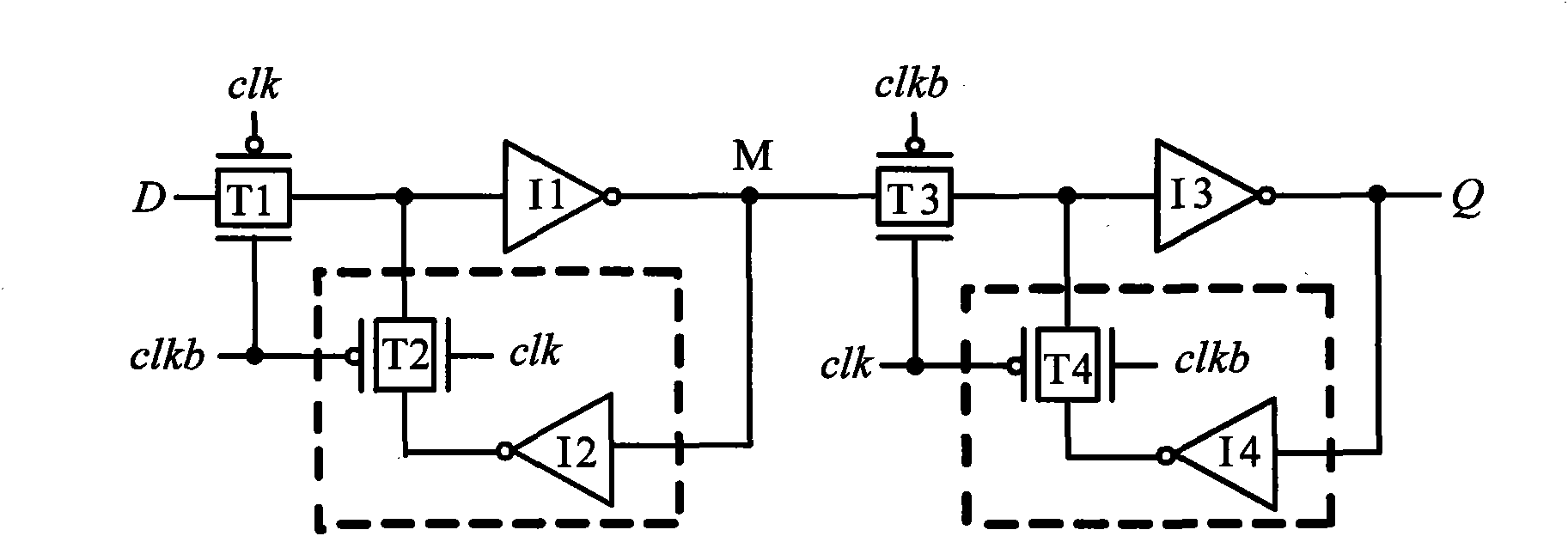

[0029] Embodiment two: if Figure 6 and Figure 7 A low-power master-slave D flip-flop is shown, which consists of input inverter XI1, clock inverter XI2 and two cascaded first low-power RS latch units 1 and second low-power RS The latch unit 2 is composed of the first low-power RS latch unit 1 and the second low-power RS latch unit 2 with the same internal structure, both of which use Figure 5 In the low-power RS latch unit shown in Embodiment 1, the first low-power RS latch unit 1 includes an input drive and synchronization circuit, a pull-down circuit, a power control circuit, and a first inverting phase coupled with each other. and the second inverter, the input drive and synchronization circuit is composed of the third PMOS transistor P3 1 , the fourth PMOS tube P4 1 , the fifth PMOS tube P5 1 and the sixth PMOS transistor P6 1 The pull-down circuit consists of the third NMOS transistor N3 1 and the fourth NMOS transistor N4 1 The power control circuit c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More