Packaging structure of semiconductor element and manufacture method thereof

A technology of packaging structure and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as long working hours, chip electrical performance failure, and a chip electrical performance failure, etc., to achieve Effects of improving yield rate and improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

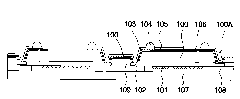

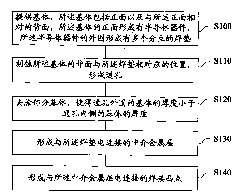

[0027] In the present invention, after the through hole is formed, part of the matrix is removed so that the thickness of the matrix around the through hole is smaller than the thickness of the matrix inside the through hole, thereby making the depth of the through hole smaller, which can ensure that the opening of the through hole is not easily formed. The accumulation of metal or insulating materials greatly improves the yield rate of the process, thereby improving the reliability of the product, and is conducive to large-scale production.

[0028] The packaging structure and manufacturing method of the semiconductor device of the present invention will be described in more detail below in conjunction with schematic diagrams, wherein a preferred embodiment of the present invention is represented, it should be understood that those skilled in the art can modify the present invention described here, and still realize the present invention Beneficial effects of the invention. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More