Electric charge capture non-volatile semiconductor storage unit and manufacture method thereof

A technology of charge trapping and manufacturing methods, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., which can solve the problems of high power consumption, slow programming speed, and low efficiency of hot electron injection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

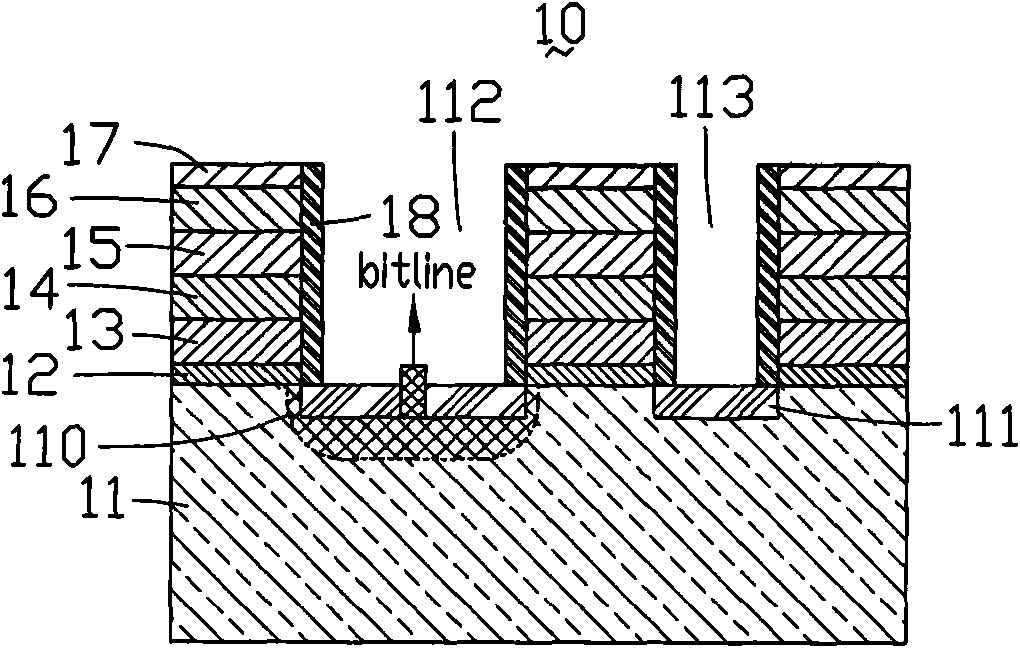

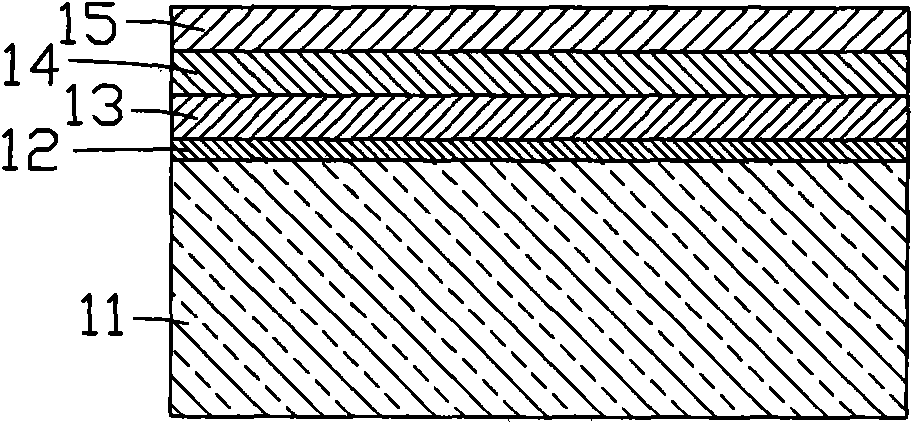

[0026] see figure 1 , figure 1 It is a cross-sectional schematic view of the charge trapping non-volatile semiconductor memory of the present invention. The charge-trapping non-volatile semiconductor memory 10 includes a semiconductor substrate 11, a tunnel insulating layer 12, a charge-trapping layer 13, a blocking insulating layer 14, a gate electrode 15, a first metal layer 16, and a hard mask Layer 17 and side walls 18. The surface of the semiconductor substrate 11 has a drain region 110 and a source region 111 . The above-mentioned tunnel insulating layer 12, charge trapping layer 13, blocking insulating layer 14, gate electrode 15, first metal layer 16 and hard mask layer 17 are sequentially formed on the above-mentioned semiconductor substrate 11 except for the above-mentioned drain region 110 and the above-mentioned source. Areas other than Area 111.

[0027] A first opening 112 and a second opening 113 are respectively formed in spaces corresponding to the drain r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More