Method for preparing longitudinal high-pressure deep-slot transistor

A technology of semiconductor tubes and semiconductors, which is applied in the field of preparation of silicon-made vertical high-voltage deep-groove metal oxide semiconductor field-effect transistors, can solve the problems of high device performance, low process cost, and high process controllability, so as to improve reliability, The effect of improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

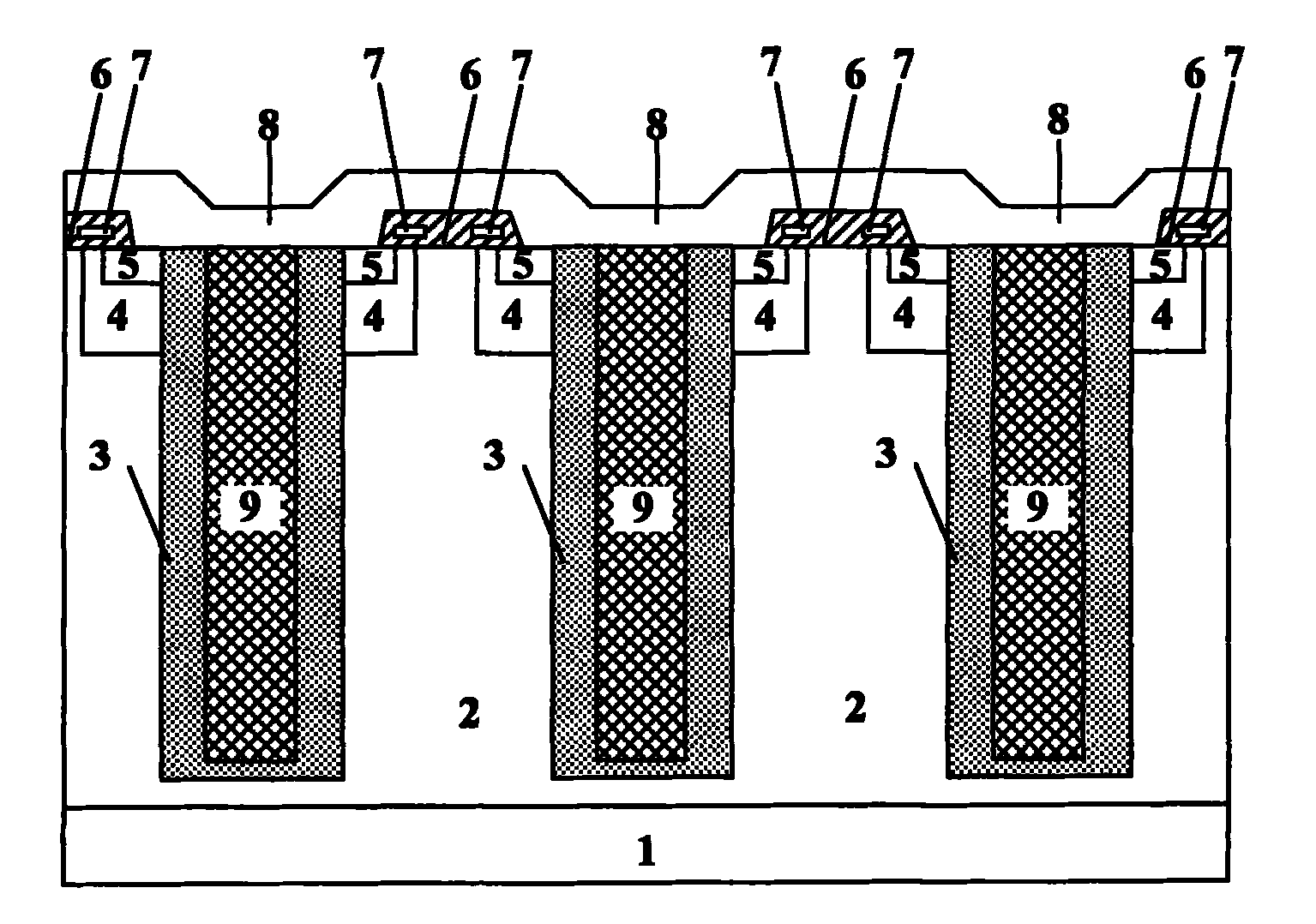

[0022] Referring to Figures 1-8, a method for manufacturing a vertical high-voltage deep-groove semiconductor tube includes the following steps:

[0023] As shown in FIG. 1 : an N-type doped substrate is taken, and an N-type epitaxial layer is grown by a known epitaxial growth process.

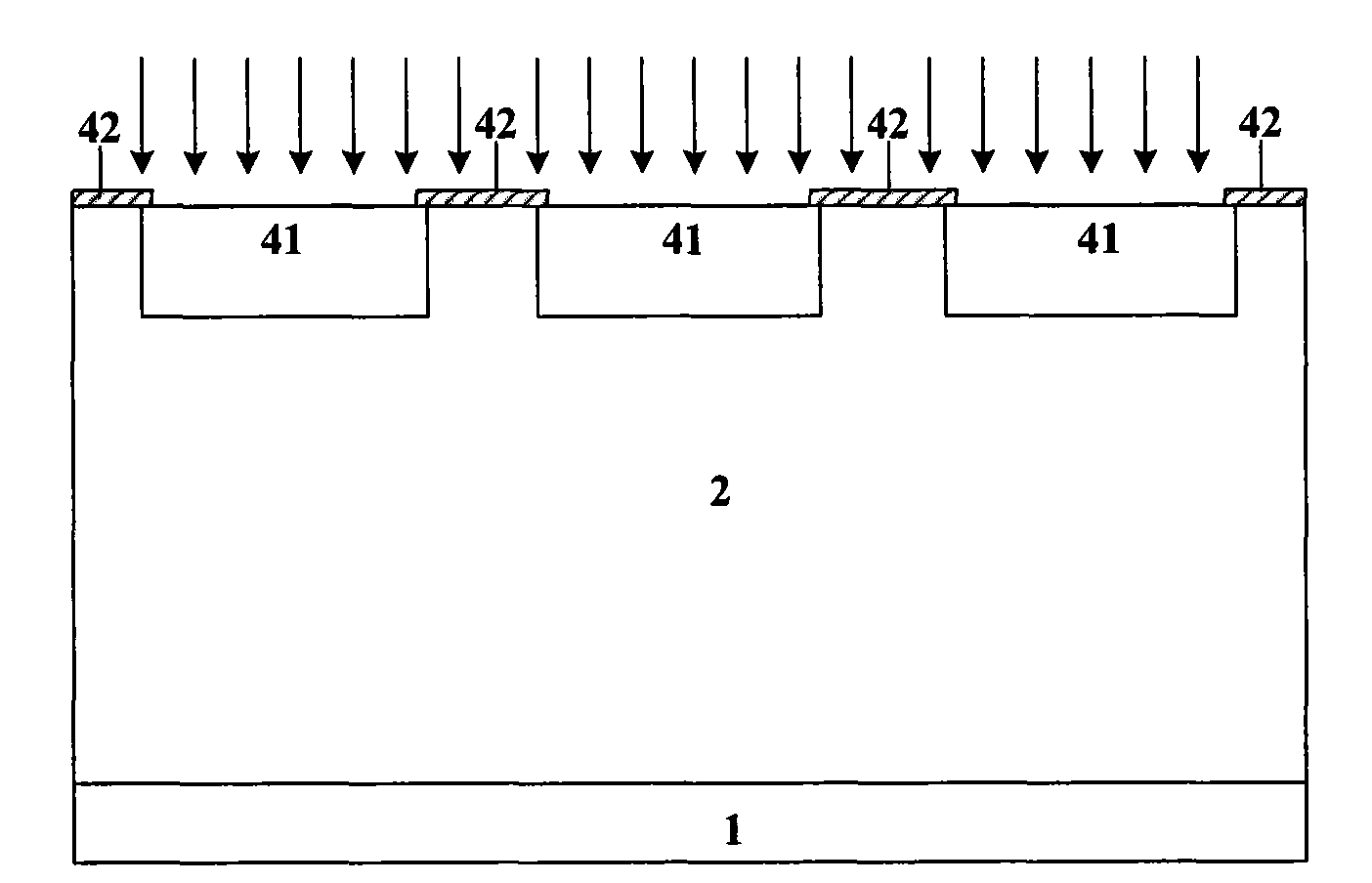

[0024] As shown in FIG. 2 , a P-type doped semiconductor region 4 is formed by using a mask plate 42 and using known ion implantation and annealing processes.

[0025] As shown in FIG. 3 , a deep groove 51 is formed in the N-type epitaxial layer 2 by a known deep groove etching process.

[0026] As shown in Fig. 4, molten borophosphosilicate glass 19 is then filled into the deep groove.

[0027] As shown in Figure 5, the borophosphosilicate glass on the surface of the device is removed by a known chemical vapor polishing process, and then the boron impurities and phosphorus impurities in the borophosphosilicate glass are diffused to the side walls of the deep groove by a known annealing push-...

Embodiment 2

[0037] An N-type doped substrate is taken, and an N-type epitaxial layer is grown by a known epitaxial growth process. The concentration of the N-type epitaxy is 1015cm-3, then use the mask 42, adopt the known ion implantation and annealing process to form the P-type doped semiconductor region 4, and then use the known deep groove etching process in the N-type epitaxial layer 2 Deep grooves 51 are formed. The molten borophosphosilicate glass 19 is then filled into the deep groove. And the content of the phosphorus source in the borophosphosilicate glass 19 is controlled within 1014, and the content of the phosphorus source is slightly higher than it can be. Then the borophosphosilicate glass on the surface of the device is removed by the known chemical vapor polishing process, and then the known The annealing push-well process makes the boron and phosphorus impurities in the borophosphosilicate glass diffuse into the silicon on the sidewall and bottom of the deep trench, maki...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More