Method for forming dual-depth trench

A double-depth, groove technology, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as gaps, device manufacturing yield reduction, device failure, etc., to improve fill factor, improve device yield, The effect of increasing the area of the active region

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

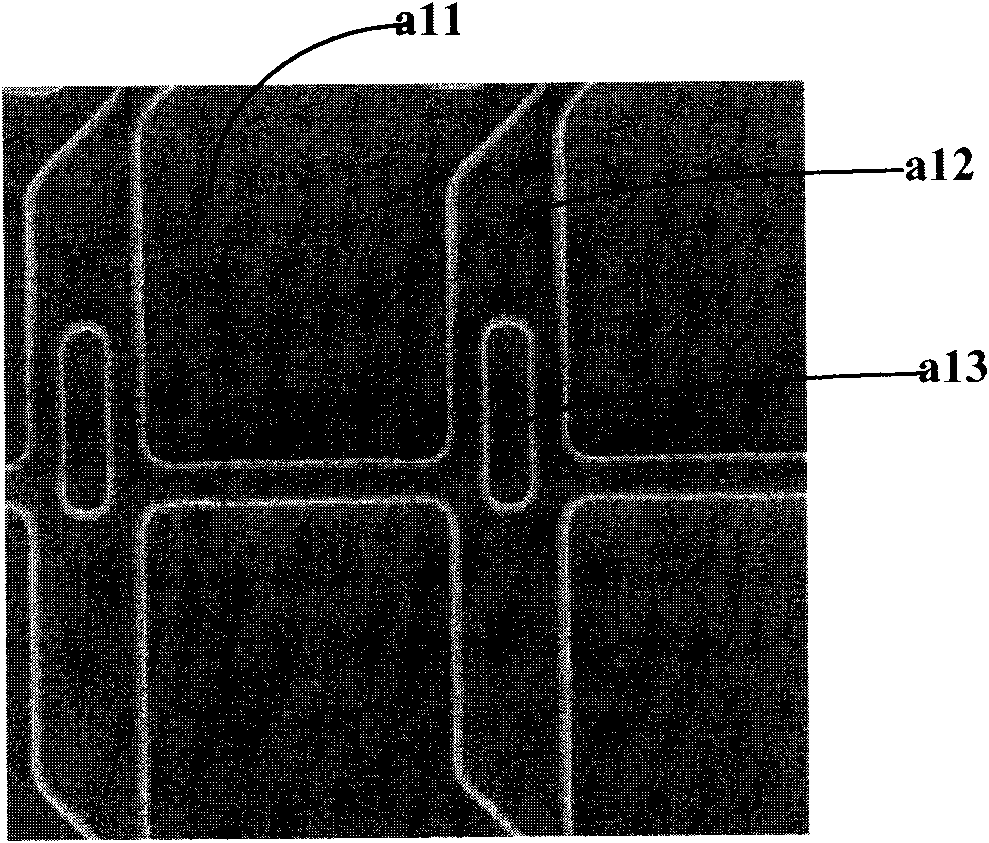

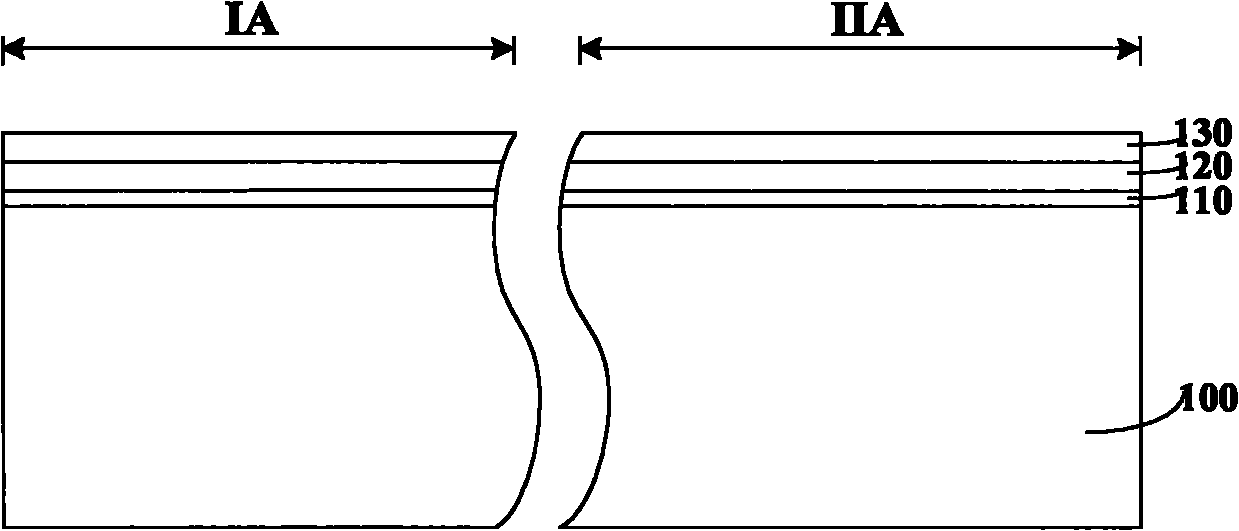

[0011] The invention provides a method for forming a double-depth trench, comprising: providing a semiconductor substrate, the semiconductor substrate sequentially includes a silicon substrate, a buried oxide layer, a barrier layer, and an oxide layer; the semiconductor substrate includes a pixel region and a peripheral region; forming a photoresist pattern on the oxide layer; using the photoresist pattern as a mask, performing ion implantation and annealing on the oxide layer, forming an ion implantation layer in the oxide layer in the peripheral region; etching the oxide layer , barrier layer, buried oxide layer and silicon substrate form a first trench and a second trench; the depth of the first trench is smaller than the depth of the second trench.

[0012] The specific embodiment of the present invention for forming double-depth grooves will be described in detail below with reference to the accompanying drawings.

[0013] refer to figure 2 , an embodiment of the presen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More