Trench type semiconductor power device with low gate resistance and preparation method thereof

A technology for power devices and semiconductors, which is applied in the field of new and improved cell structure and device configuration, can solve the problems of limiting cell density, difficult process, and increasing gate resistance, and achieves the effects of improving cell density, simple fabrication, and reducing gate resistance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

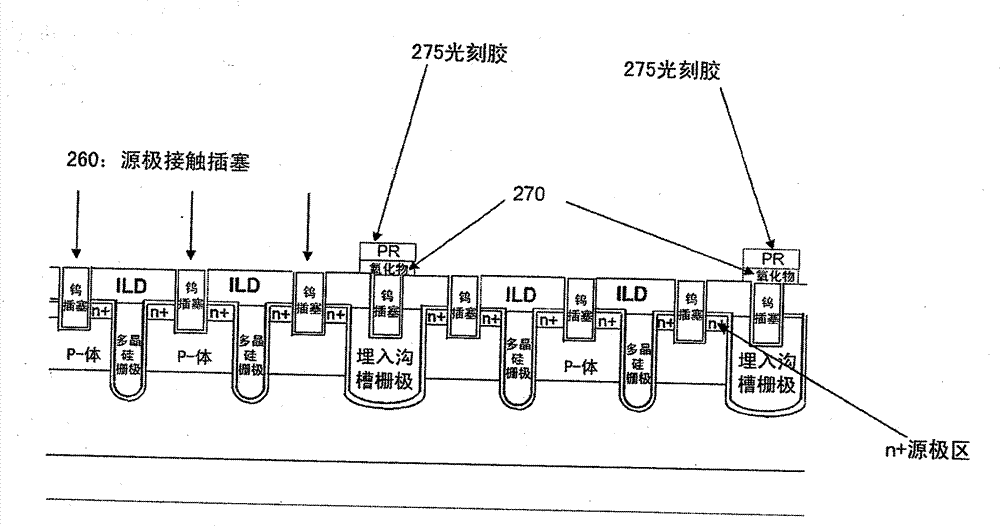

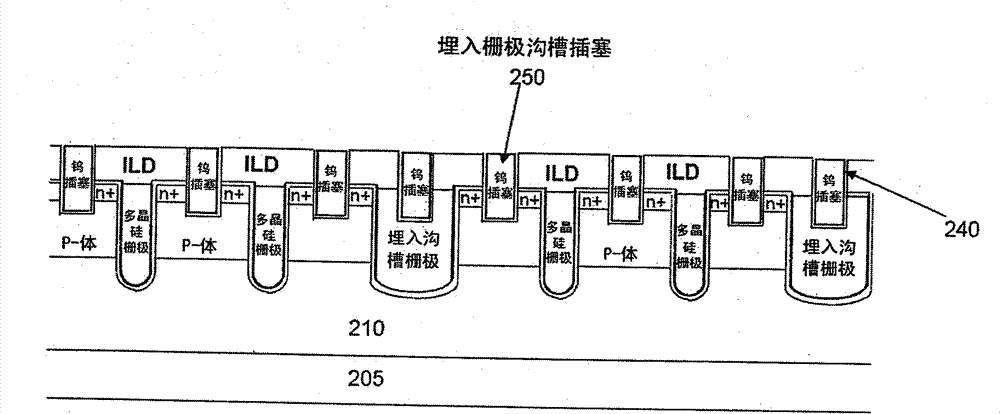

[0049] The trench type semiconductor power device with low gate resistance of the present invention, in order to reduce the gate resistance, a buried trench type gate 250 with titanium / titanium nitride / tungsten plugs is formed, with an NSG layer 270 on the top, The buried trench gate 250 arrangement is one standard trench gate with one buried trench gate, or 10 standard trench gates with one buried trench gate ; The number of the buried trench gate 250 is inversely proportional to the width of the standard trench gate of the unit, and is inversely proportional to the required gate resistance value. With the new invention, the gate resistance is not limited by the small cell pitch.

[0050] The following figure ( Figure 5A to Figure 5H ) in the X-direction sectional view of the technological process for demonstrating the idea of the present invention: in Figure 5A In , a trench mask is used to form trenches 208 in epitaxial layer 210 on base layer 205 .

[0051] exist ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More