Complementary metal oxide semiconductor (CMOS) ultra-wide-band divide-by-2 frequency divider structure

A two-frequency divider and ultra-wideband technology, which is applied in the field of two-frequency divider structure, can solve the problems of high power consumption and insufficient working bandwidth of CML frequency band, and achieve the effects of low power consumption, widening operating frequency range and convenient design.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention will be described in further detail below in conjunction with the accompanying drawings.

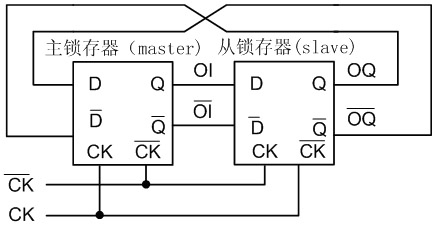

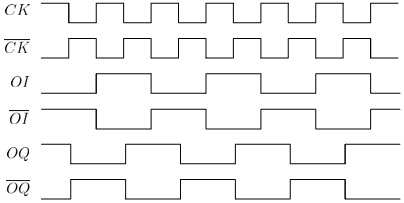

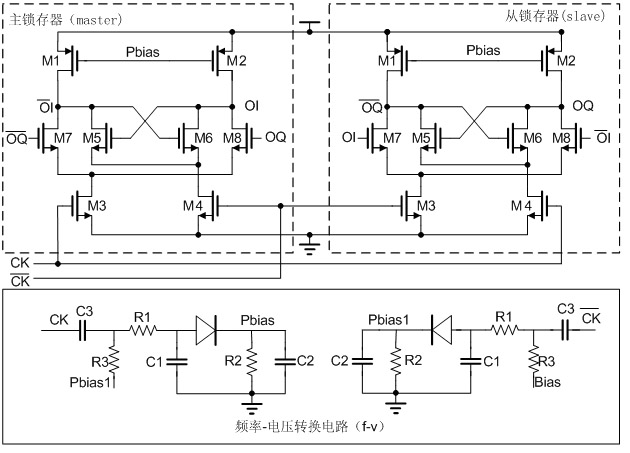

[0023] figure 1 It is a structural block diagram of a frequency divider with a CML structure. The structure contains two master-slave differential D latches, the two latches are connected in the form of negative feedback, and the input clock is a differential signal and , can be a sinusoidal signal or a square wave signal. Output two pairs of quadrature differential signals: and , and . In the positive half cycle of the clock, the main latch works in the following state, and its output , follow input , ;The slave latch works in the latched state, and its output remains unchanged, which is the output of the previous clock phase , . In the negative half cycle of the clock, the main latch works in the latched state, and its output remains unchanged, which is the output of the previous clock phase , ;The slave latch works in the fol...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More