MOS (Metal-oxide Semiconductor) transistor and making method thereof

A technology of MOS transistors and manufacturing methods, which is applied in the field of MOS transistors and their manufacturing, can solve the problems of unsatisfactory process development requirements, single structure of MOS transistors, and inflexible design, etc., and achieve flexible layout, improved utilization rate, and satisfactory integration Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

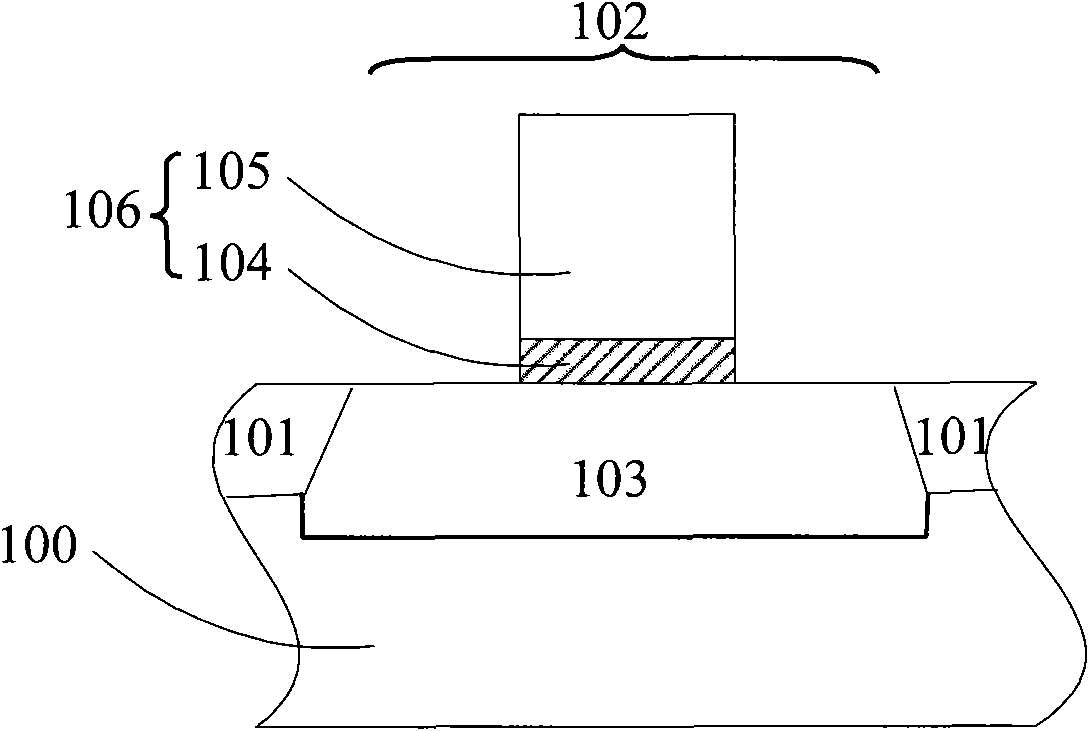

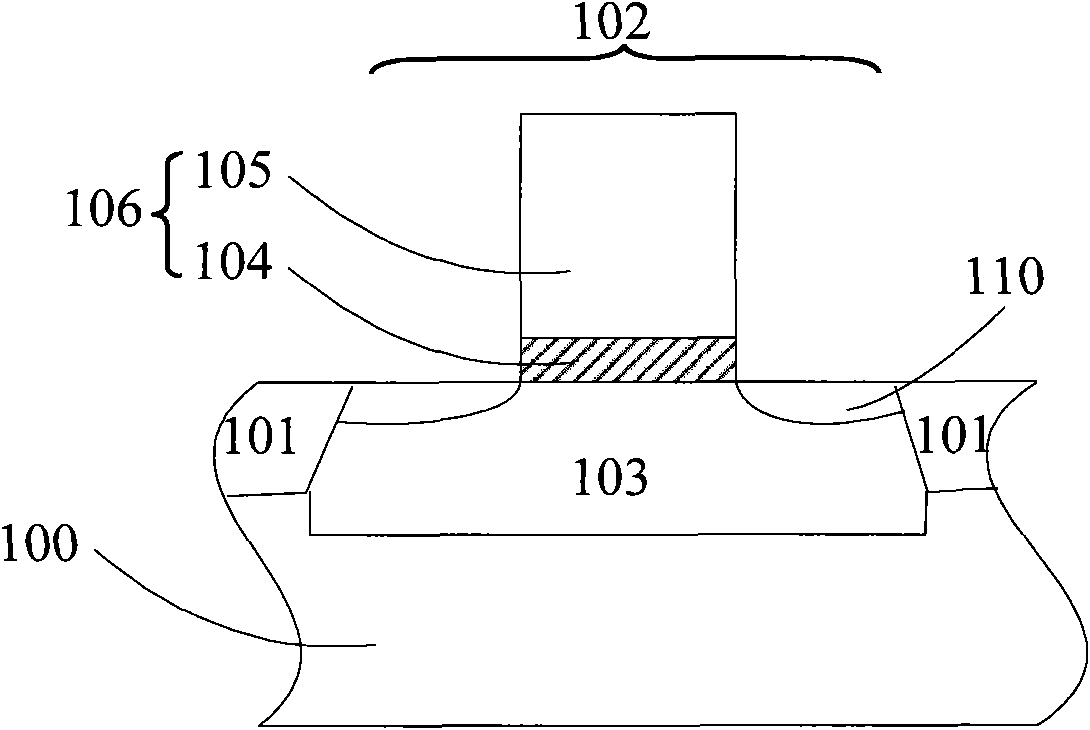

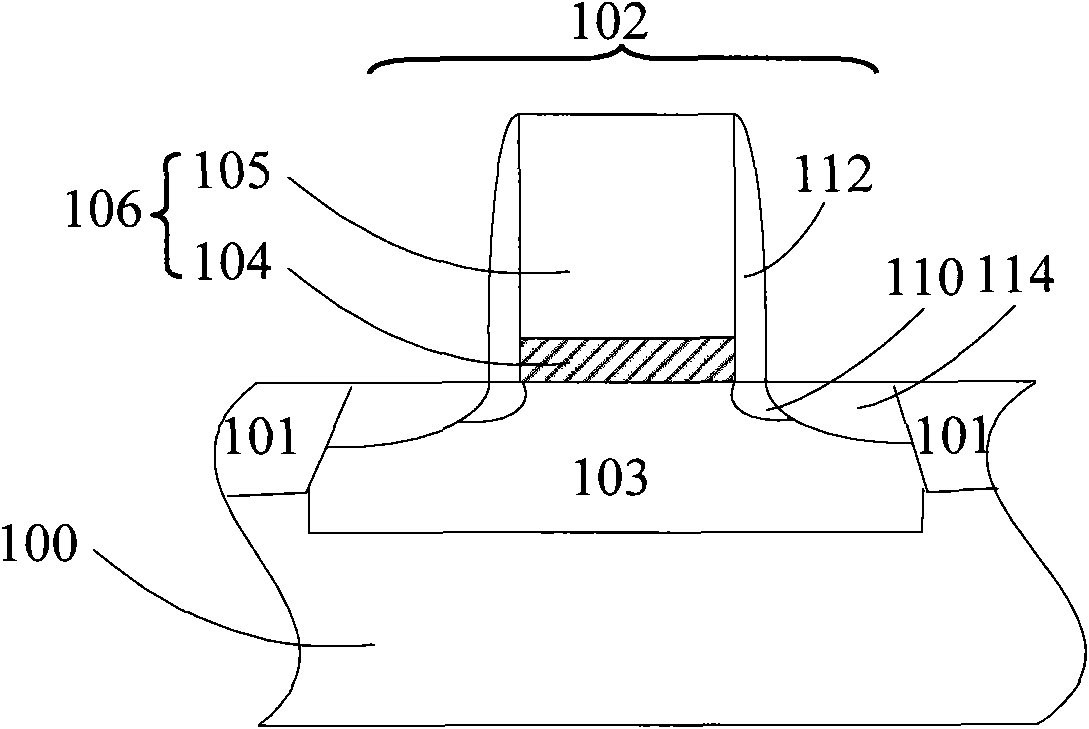

[0029]The purpose of the present invention is to implant p-type ions with different depths into the top layer of silicon-on-insulator n-type single-crystal silicon to form a first p-type single-crystal silicon layer and a second p-type single-crystal silicon layer overlapping with the n-type single-crystal silicon layer. The monocrystalline silicon layer enables the volume of the MOS transistor to be further reduced, meets the trend of increasing integration of semiconductor devices, improves the utilization rate of the chip area, makes the layout more flexible; and saves the manufacturing cost. In addition, the corners of the first n-type single crystal silicon layer and the second n-type single crystal silicon layer are subjected to high temperature treatment to make them smooth, so as to solve the corner effect caused by the strong current at the corners of square corners.

[0030] The specific implementation method of forming a MOS transistor in the present invention includ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More