Framework of high speed and low power consumption serial communication data receiving interface

A serial communication and receiving interface technology, which is applied in the field of high-speed and low-power serial communication data receiving interface architecture, can solve problems affecting the image quality of image sensors, etc., and achieve the effects of reducing power consumption, reducing production costs, and reducing requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

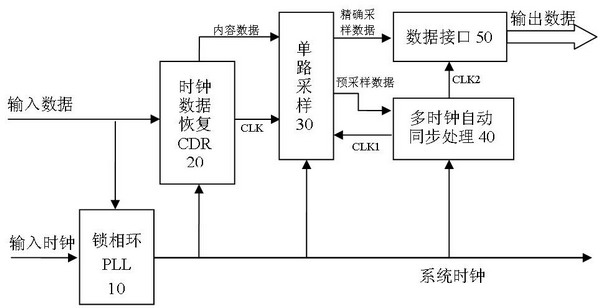

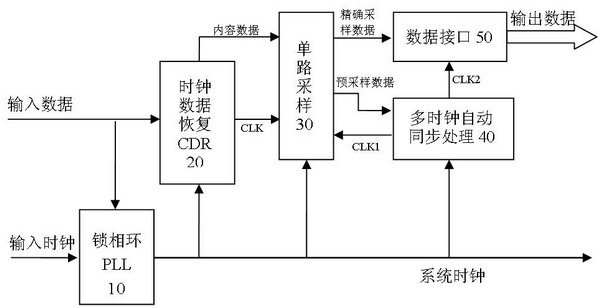

[0031] The following is attached figure 2 The specific implementation manner of the high-speed and low-power serial communication data receiving interface architecture of the present invention is described.

[0032] First, an input clock received from the outside passes through a phase-locked loop (PLL) 10 to generate a system clock with the highest frequency of the system. The phase-locked loop (PLL) 10 is a phase feedback automatic control module with functions of clock synchronization and phase locking. It implements frequency multiplication of the input clock by locking the phase to obtain the system clock synchronized with the input data. The synchronized system clocks are respectively output to the clock data recovery module (CDR) 20, the single-channel sampling module 30 and the multi-clock automatic processing module in the present invention.

[0033] The above input data is also connected to the open-loop clock data recovery module (CDR) 20, the clock data recovery ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More