Grid structure of high-K material based on silicon-on-insulator (SOI) substrate and preparation method thereof

A high dielectric constant material and high dielectric constant technology, applied in the direction of circuits, electrical components, semiconductor devices, etc., can solve the problems of not having, reducing the electron mobility of devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

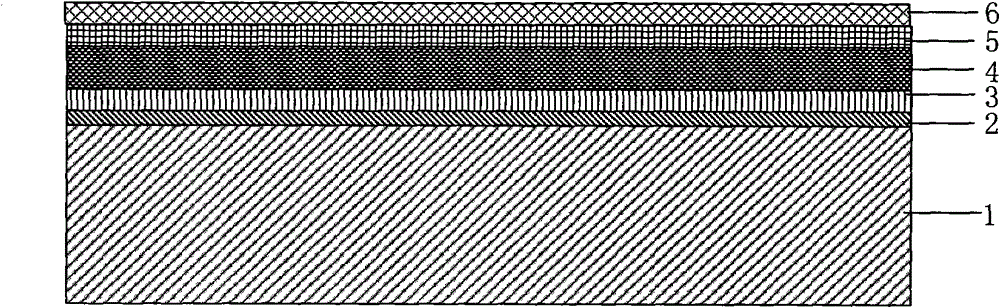

[0018] Please refer to shown in Fig. 1, a kind of high dielectric constant material gate structure based on SOI substrate comprises the SiO that is positioned on SOI substrate 1 2 Layer 2, on SiO 2 Si on layer 3 N 4 Layer 3, located in Si 3 N 4 The high dielectric constant oxide layer 4 on the high dielectric constant oxide layer, the high dielectric constant oxynitride layer 5 on the high dielectric constant oxide layer, and the metal gate electrode 6 on the high dielectric constant oxynitride layer.

[0019] A method for preparing a high dielectric constant material gate structure based on an SOI substrate, the method comprising the following steps:

[0020] Step 1, cleaning and drying, put the cut SOI substrate into the first solution and ultrasonically clean it for 15 minutes to remove metal contaminants on the substrate surface, then rinse with deionized water, and then put the substrate into the diluted second solution In solution (volume ratio: HF:H 2 O=1:50) for ...

Embodiment 2

[0034] In this embodiment, the cut SOI substrate may not be cleaned or dried (step 1 is omitted), and the cut SOI substrate is directly processed in step 2 by PEALD process, and then processed in steps 3-5 by ALD process. Other processing steps in this embodiment are the same as in Embodiment 1.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More