Method for overcoming defects of silicon chip with STI and method for constructing STI on silicon chip

A technology for silicon wafers and structures is applied in the field of suppressing defects in silicon wafers with shallow trench isolation trench structures, and can solve problems such as affecting the performance of semiconductor circuits and irregular surface defects.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] By analyzing the mechanism of the CMP process, it can help to understand the reasons for the formation of microcracks at the corners of the STI.

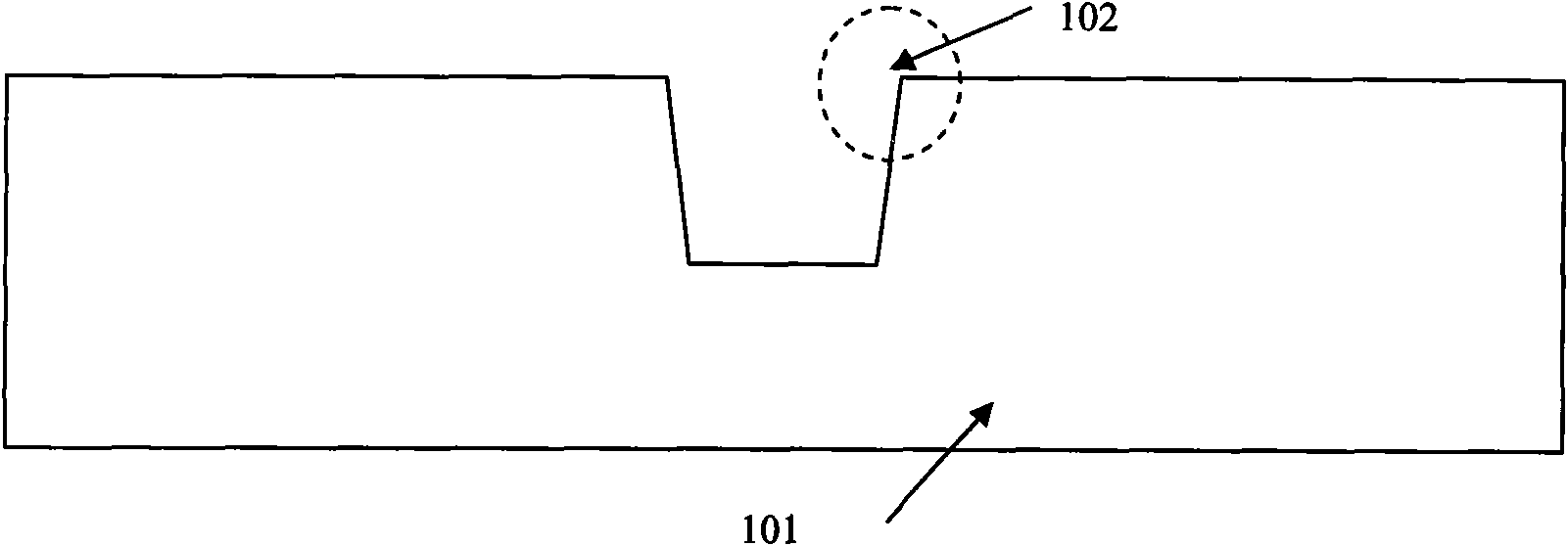

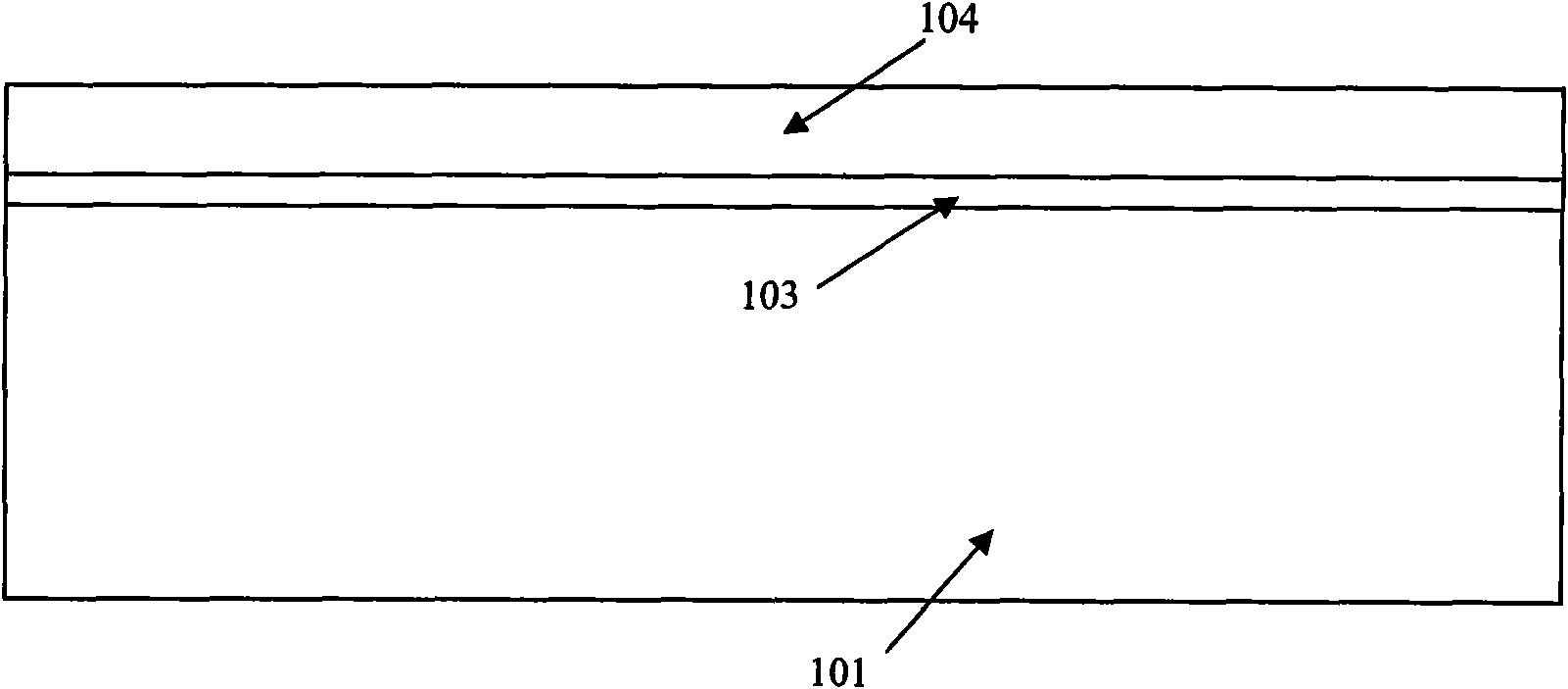

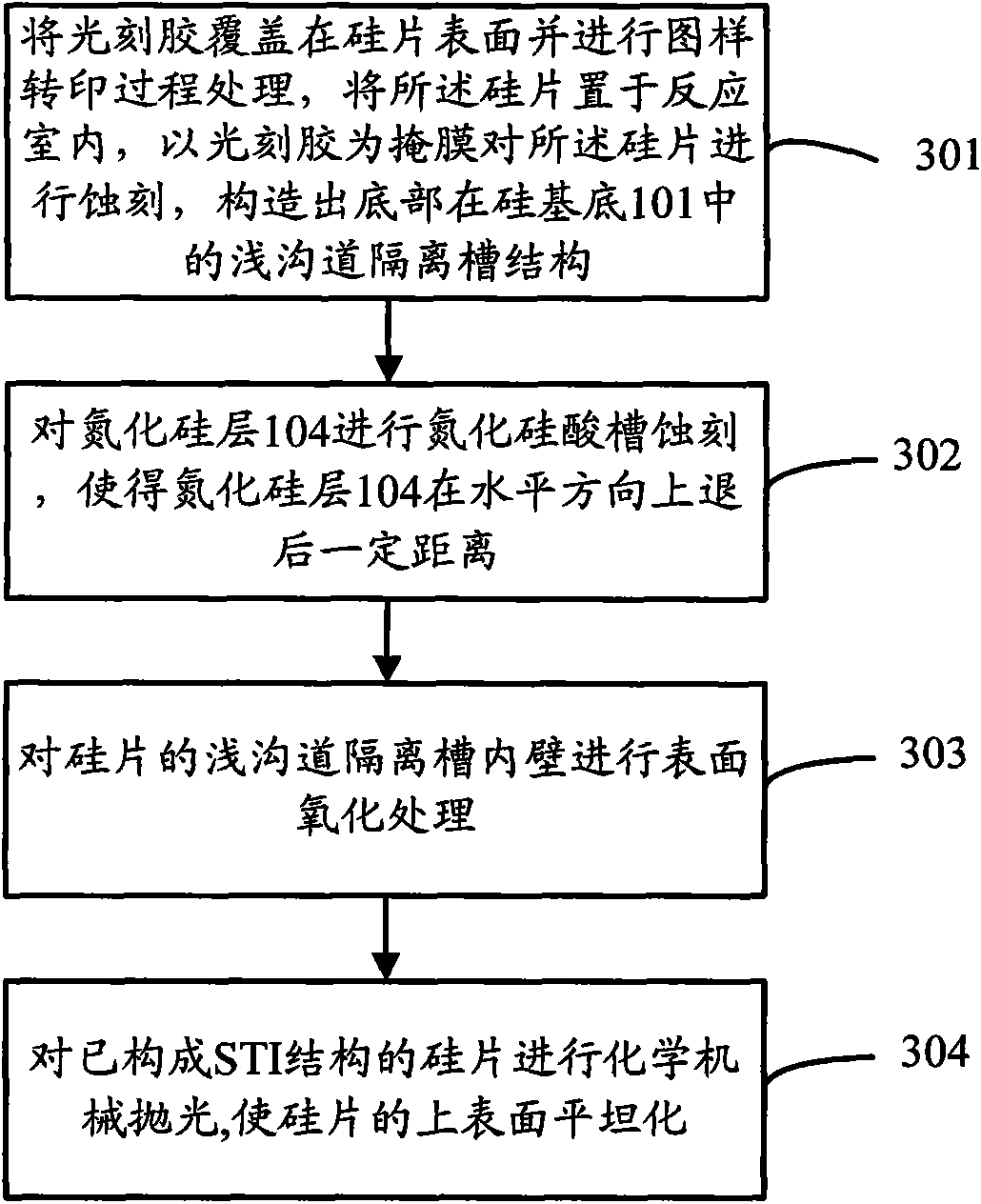

[0051] by image 3The silicon wafer shown is an example, in the CMP process, the silicon nitride layer 104 of the uppermost layer of the silicon wafer will be subjected to a downward pressure perpendicular to the plane where the silicon nitride layer 104 is located; in addition, due to the mutual movement of the silicon wafer and the polishing pad , the silicon nitride layer 104 is also subjected to a tangential force along the direction of the plane where the silicon nitride layer 104 is located. The corner 102 of the STI is where the silicon nitride layer 104 , the silicon oxide layer 103 , and the silicon substrate 101 meet. Under the action of the above pressure and tangential force, the internal stress concentration of the silicon wafer tends to occur. Under the action of internal stress, fine cracks will be generated i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More