Low power-consumption time-delay controllable POR (power on reset) method and circuit

A technology of power-on reset and low power consumption, applied in the field of electricity, can solve problems such as delays that cannot reach the millisecond level, difficulty, and change the delay of power-on reset circuits, etc., and achieve the effect of small instantaneous power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

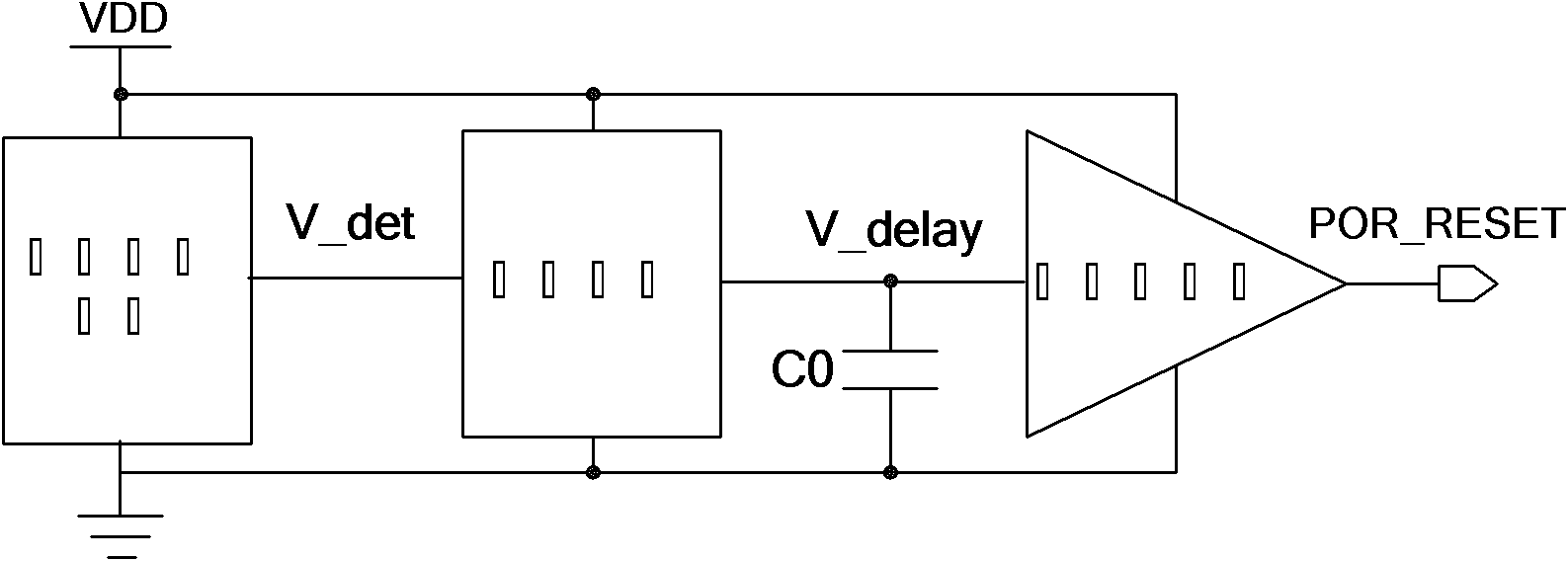

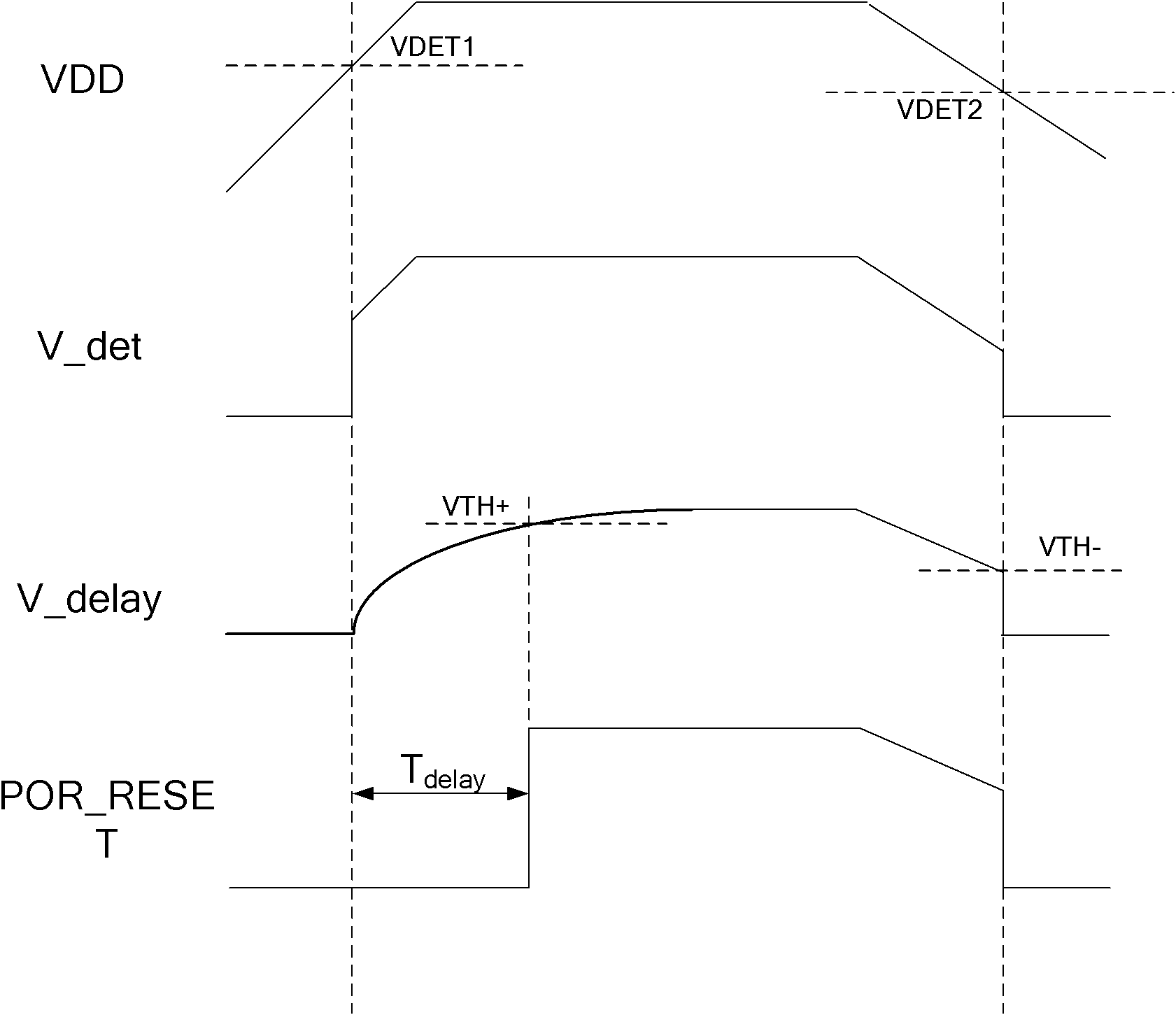

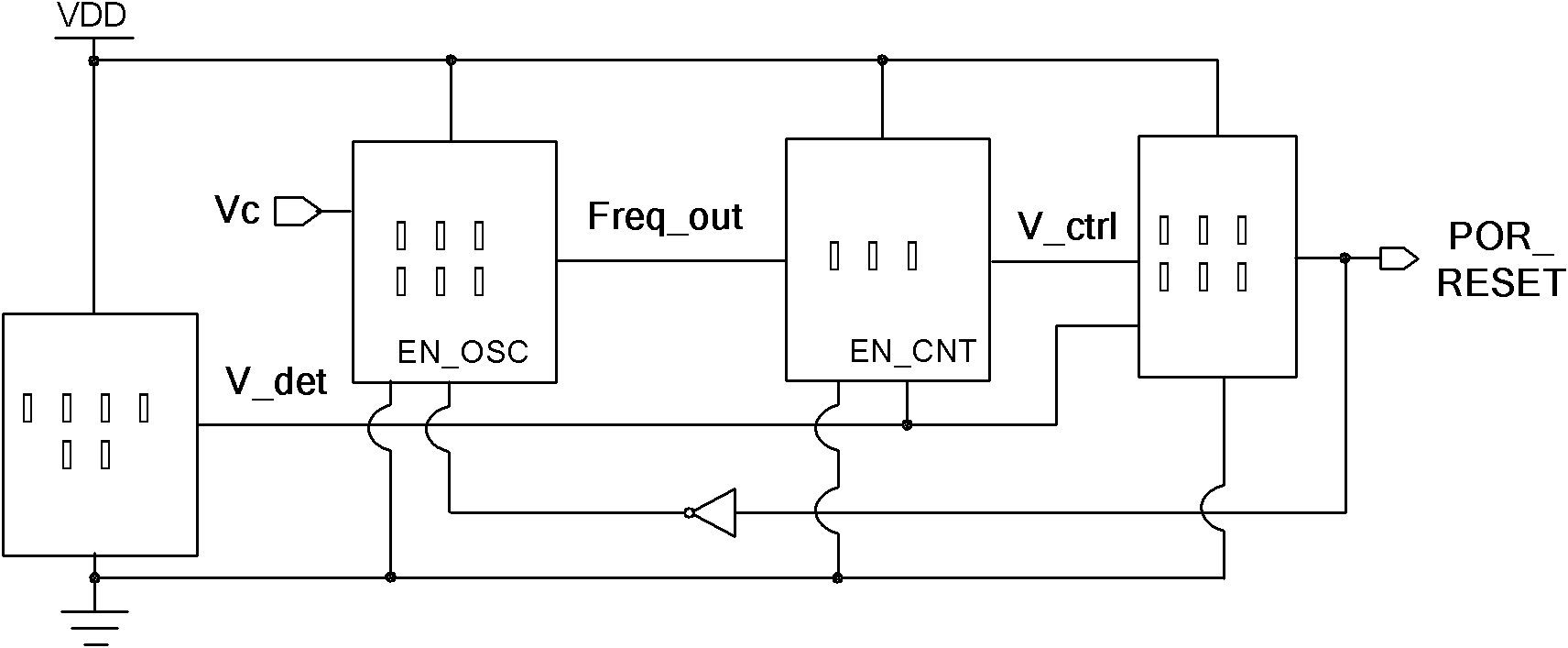

[0030] The power-on reset method with low power consumption and controllable delay of the present invention comprises the following steps: 1) programming the period T1 of the pulse waveform signal generated by the programmable oscillator through the control terminal Vc input by n bits; 2] programming the programmable oscillator Generate a pulse waveform signal to the counter; 3] When the power supply voltage is higher than the threshold, the counter starts to count the pulse waveform signal generated by the programmable oscillator; 4] When the count value of the counter reaches the set value, the counter output changes from logic low The level becomes a logic high level; 5] The output of the output buffer circuit which has the function of latching and clearing the output signal of the counter changes from a logic low level to a logic high level as a power-on reset signal; 6] uses the output A logic high output from the buffer circuit turns off the programmable oscillator and co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More