Structural design for improving power tolerance of micro low-capacitance protective device

A technology for structural design and capacitors, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as damage, and achieve the effect of increasing the chip source area, solving process incompatibility, and increasing the area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

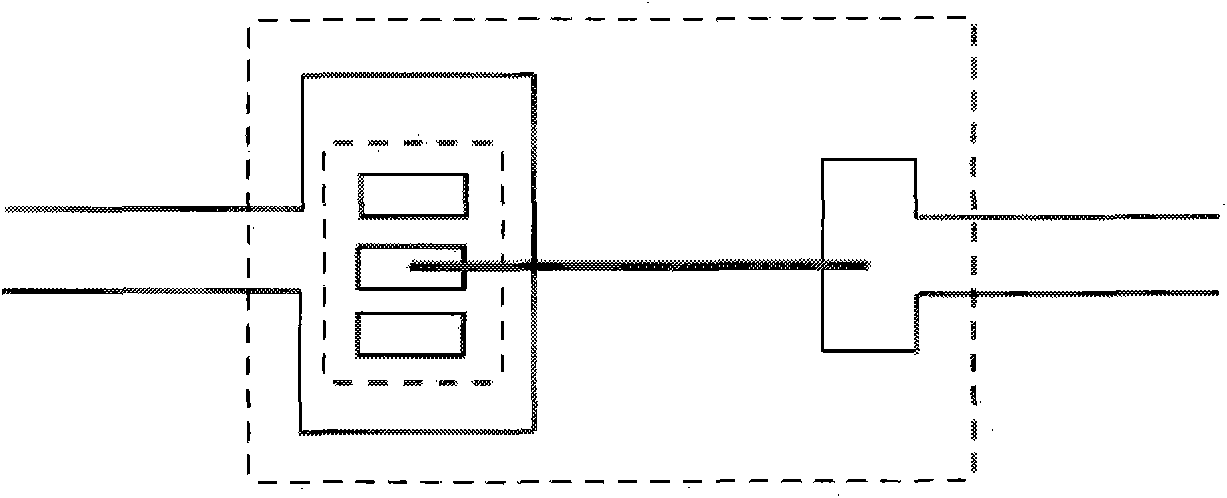

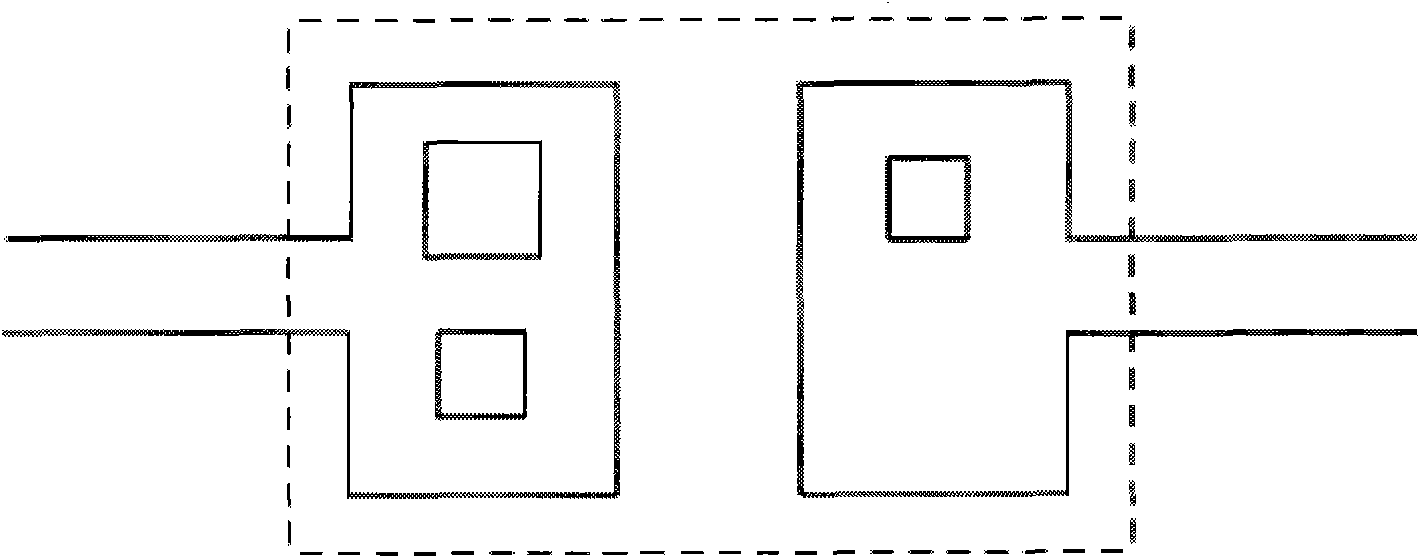

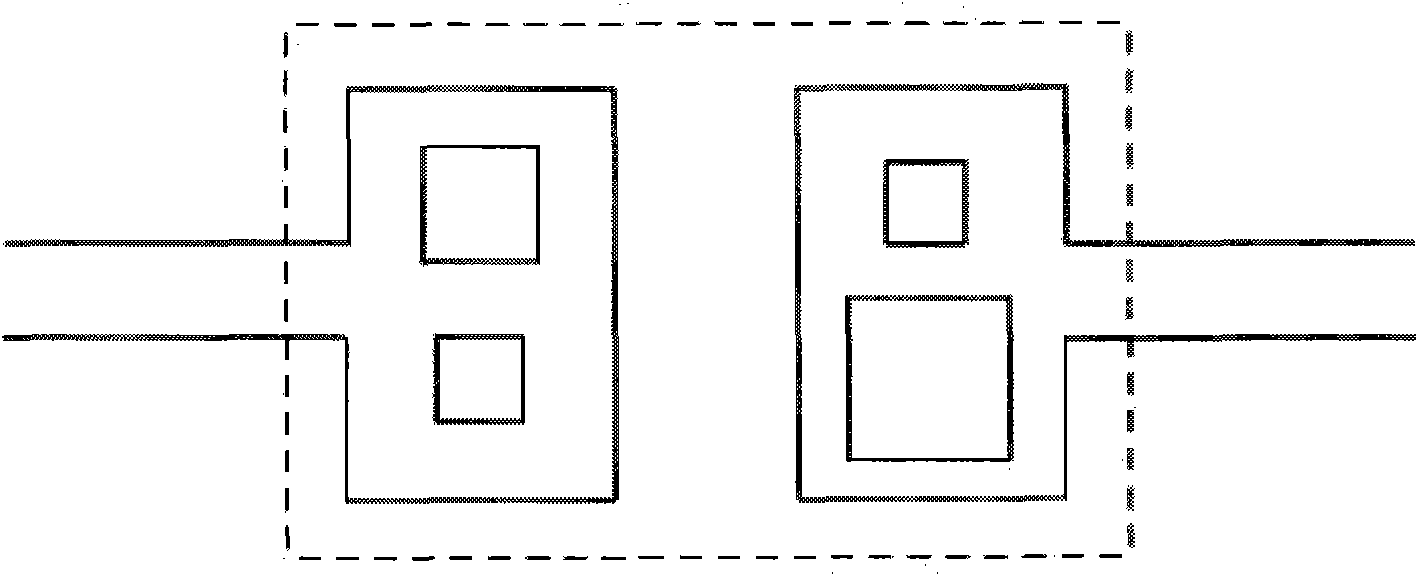

[0011] 1. Weld (conductive glue or eutectic welding) two independent chips on the metal lead frame 1, and then weld a chip on the other end 2 of the metal lead frame to form a one-way device, or weld two chips to form a two-way device.

[0012] 2. After the chip soldering is completed, it must be checked to ensure that the bonding effect of the chip is good, and then wire bonding is performed as shown in Figure 3, and finally plastic packaging is performed to form an independent device.

[0013] The invention of "a structural design for improving the power tolerance of miniature low-capacitance protection devices" lies in:

[0014] 1 Multi-core assembly, anti-power, low capacitance.

[0015] 2 Micro package, the overall size is less than or equal to 1.2mm*1mm*0.5mm.

[0016] 3 Dual carriers carry multiple chips.

[0017] Advantages of "a structural design to improve the power tolerance of miniature low-capacitance devices":

[0018] 1 The chip production process is simple. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More