Silica-based photoelectric foreign substance integrating method and silica-based photoelectric foreign substance integrating chip

An integration method and integrated chip technology, applied in optics, light guides, circuits, etc., can solve the problems of low carrier mobility, poor bonding strength, and low integration efficiency of unit module bonding technology, so as to improve the coupling efficiency, Difficulty-reducing effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

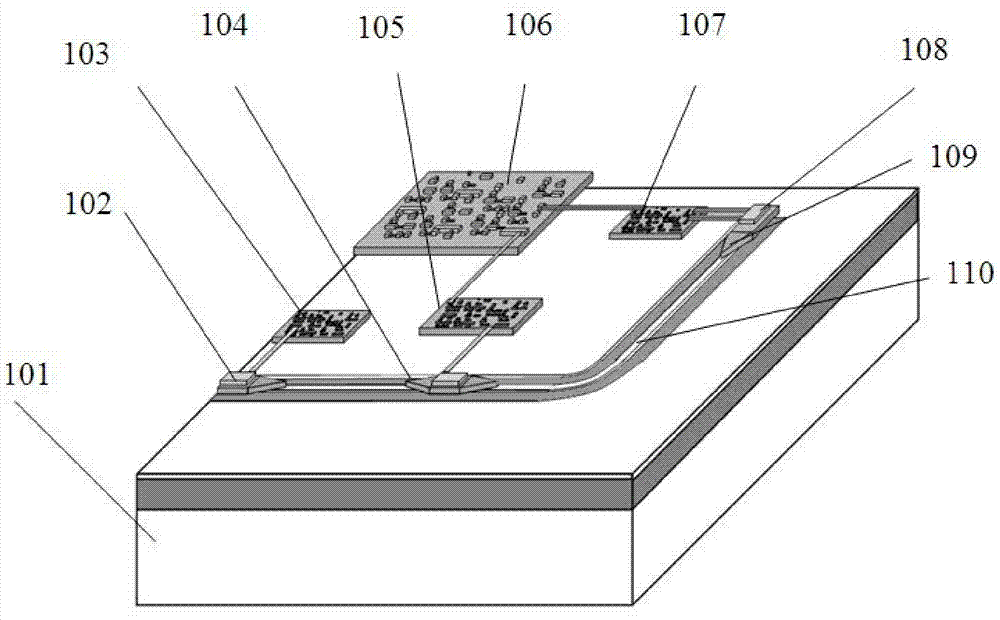

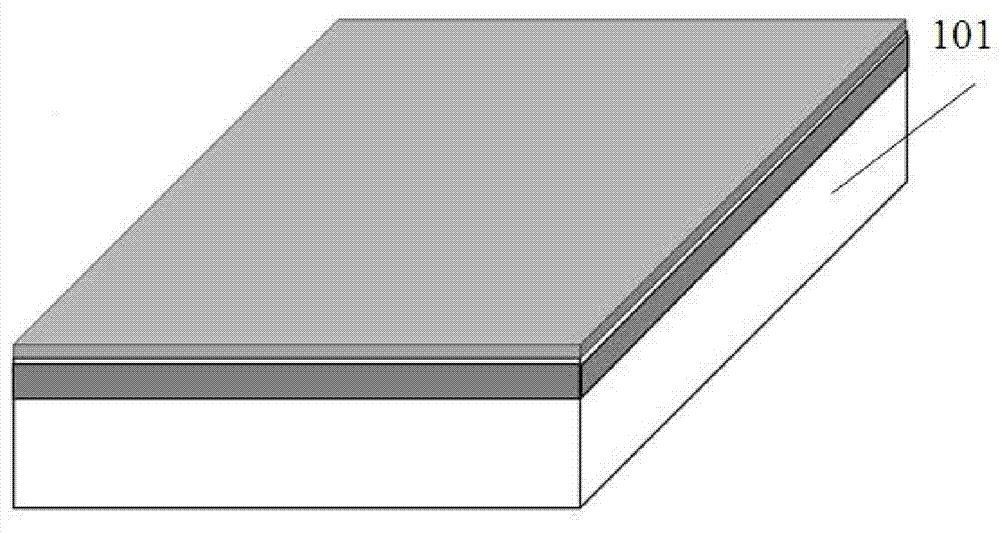

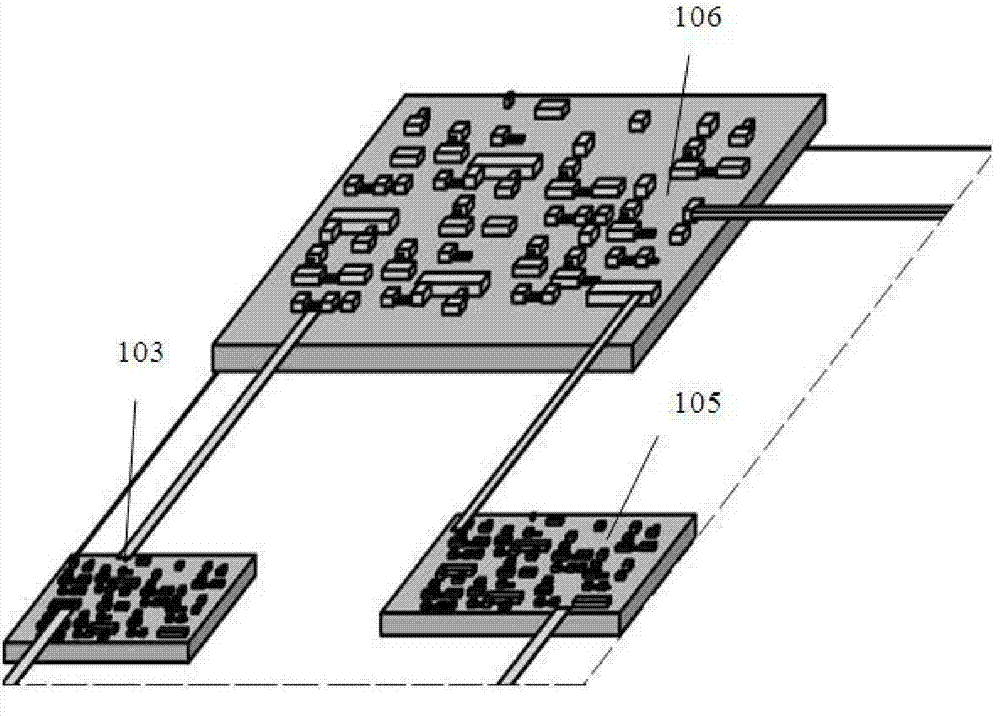

[0028]The embodiment of the present invention proposes a silicon-based optoelectronic heterogeneous integration method based on a whole-wafer bonding process and III-V CMOS technology, which specifically includes: first setting a silicon-based passive photonic device on a silicon wafer; The multi-layer quantum well structure in the active area of active photonic devices and CMOS microelectronic integrated circuits is realized by one epitaxy on the III-V wafer; the III-V wafer is bonded on the silicon wafer by the whole chip wafer bonding process, Realize high-performance heterogeneous bonding of materials; use III-V semiconductor CMOS technology integrated with existing silicon-based integrated circuit technology to manufacture CMOS microelectronic integrated circuits and drive circuits for active photonic devices; use semiconductor ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More