ESD (electrostatic discharge) high-voltage DMOS (diffused metal oxide semiconductor) device and manufacturing method thereof

A high-voltage, device technology, applied in the field of semiconductor integrated circuit manufacturing, can solve the problems of increasing the surface electric field in the drift region, the inability to realize ESD device optimization, and the easy damage of gate oxide, so as to reduce the surface electric field, reduce the trigger voltage, and reduce the conductivity. The effect of on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

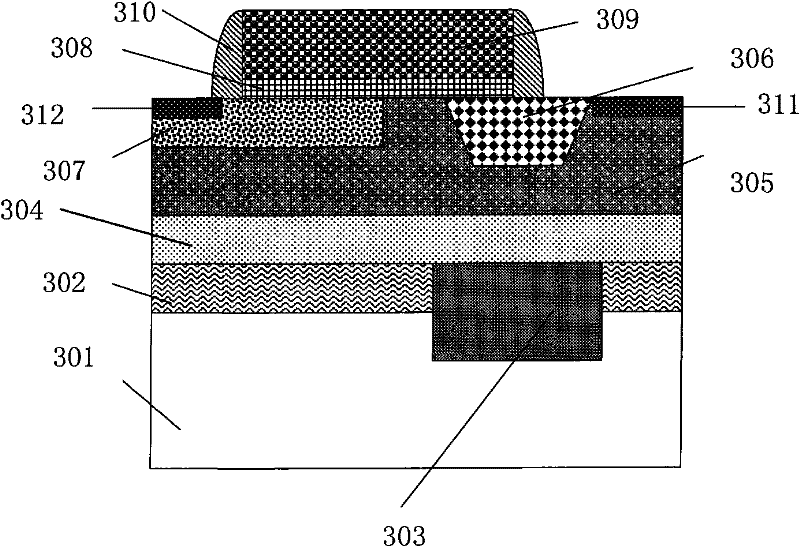

[0025] like figure 1 Shown is the structural representation of the embodiment of the present invention, the embodiment of the present invention is an ESD high voltage N-type DMOS device, comprising:

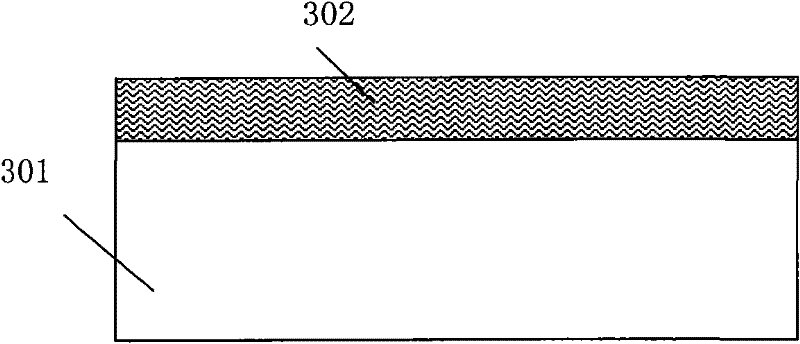

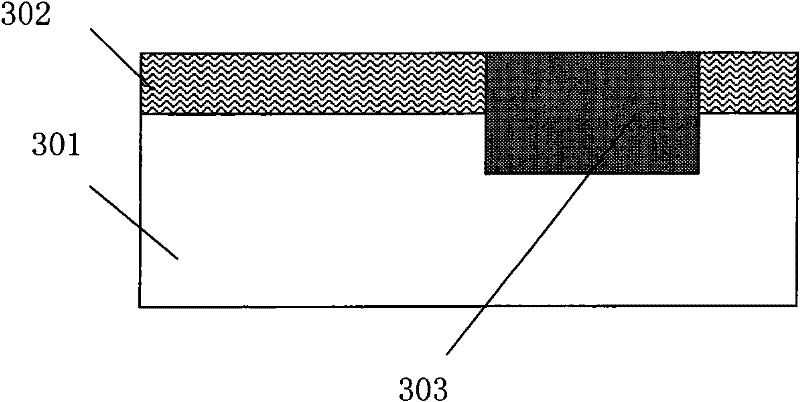

[0026] An N-type lightly doped (N-) drift region 305 is formed by implanting N-type lightly doped ions into the N-silicon epitaxial layer 304, and the silicon epitaxial layer 304 is formed on the N-type heavily doped (N+) buried layer 302 Above, the buried layer 302 is formed on the P-type substrate 301 .

[0027] A P-type channel region 307 is a P-type ion-implanted region formed in the surface part of the drift region 305 .

[0028] An N+ drain region 311 is formed in the surface partial region of the drift region 305 , and a field oxide layer 306 and a surface partial drift region 305 are separated between the drain region 311 and the channel region 307 .

[0029] An N+ source region 312 is formed in the surface part region of the channel region 307 .

[0030] A polysilicon...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More