Semiconductor structure and manufacturing method thereof

A semiconductor and wide bandgap technology, which is applied in the field of semiconductor structure and its manufacturing, can solve the problems of poor uniformity of the top layer silicon 103, difficult to control the thickness, and low yield rate, etc., and achieve the goal of suppressing the short channel effect and improving the electrical and physical properties Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The semiconductor structure and the manufacturing method thereof provided by the embodiments of the present invention solve the problems of high ultra-thin silicon-on-insulator process requirements and low yield, and better suppress the short channel effect.

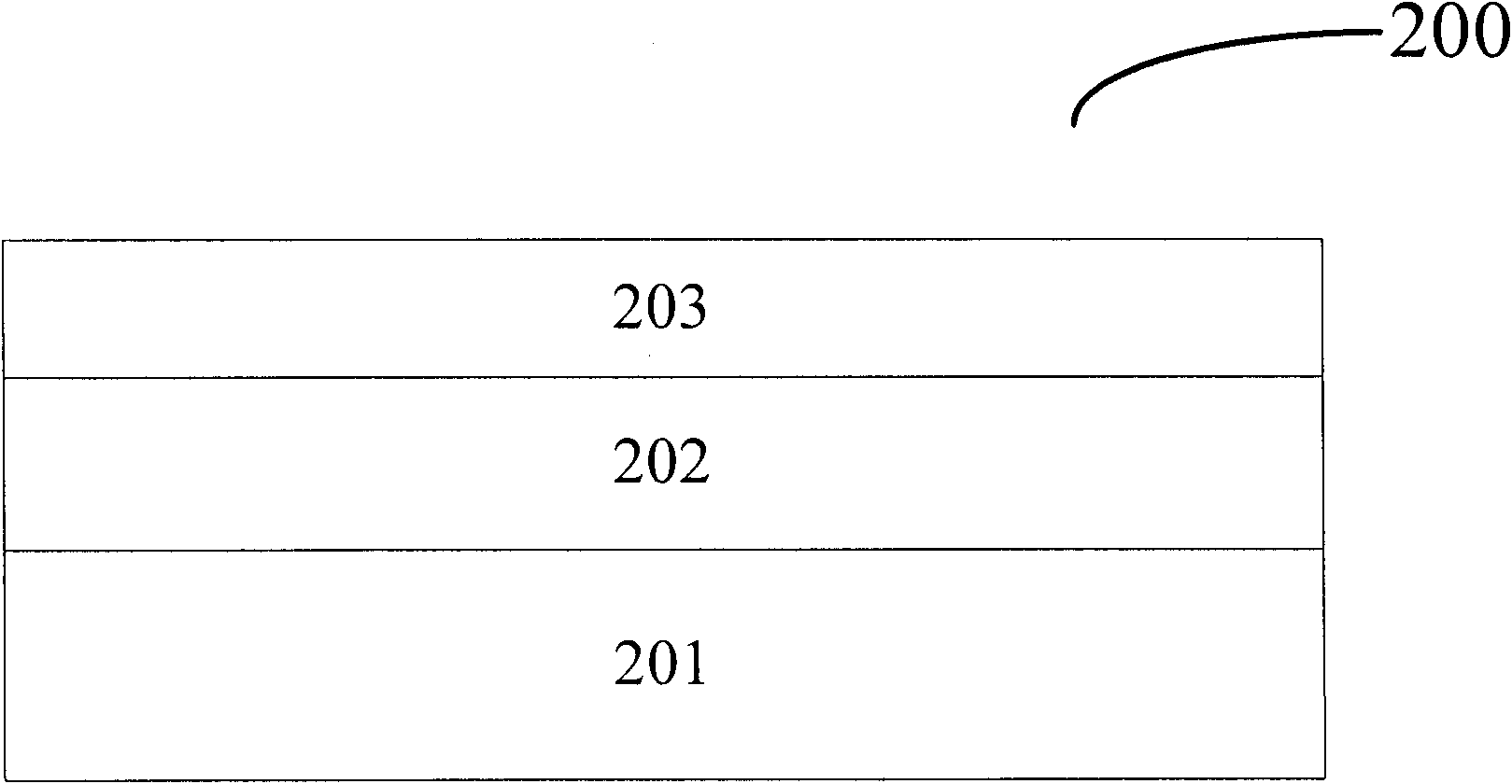

[0020] figure 2 A schematic structural diagram of a semiconductor structure 200 according to an embodiment of the present invention is shown. Such as figure 2 As shown, the semiconductor structure 200 includes a silicon substrate 201 , one or more wide bandgap semiconductor layers 202 formed on the silicon substrate, and a silicon layer 203 formed on the one or more wide bandgap semiconductor layers 202 . Wherein, the thickness of one or more wide bandgap semiconductor layers 202 is preferably 5-50 nm, and the thickness of the silicon layer 203 is preferably 5-20 nm. The top silicon layer 203 may also be referred to as top silicon.

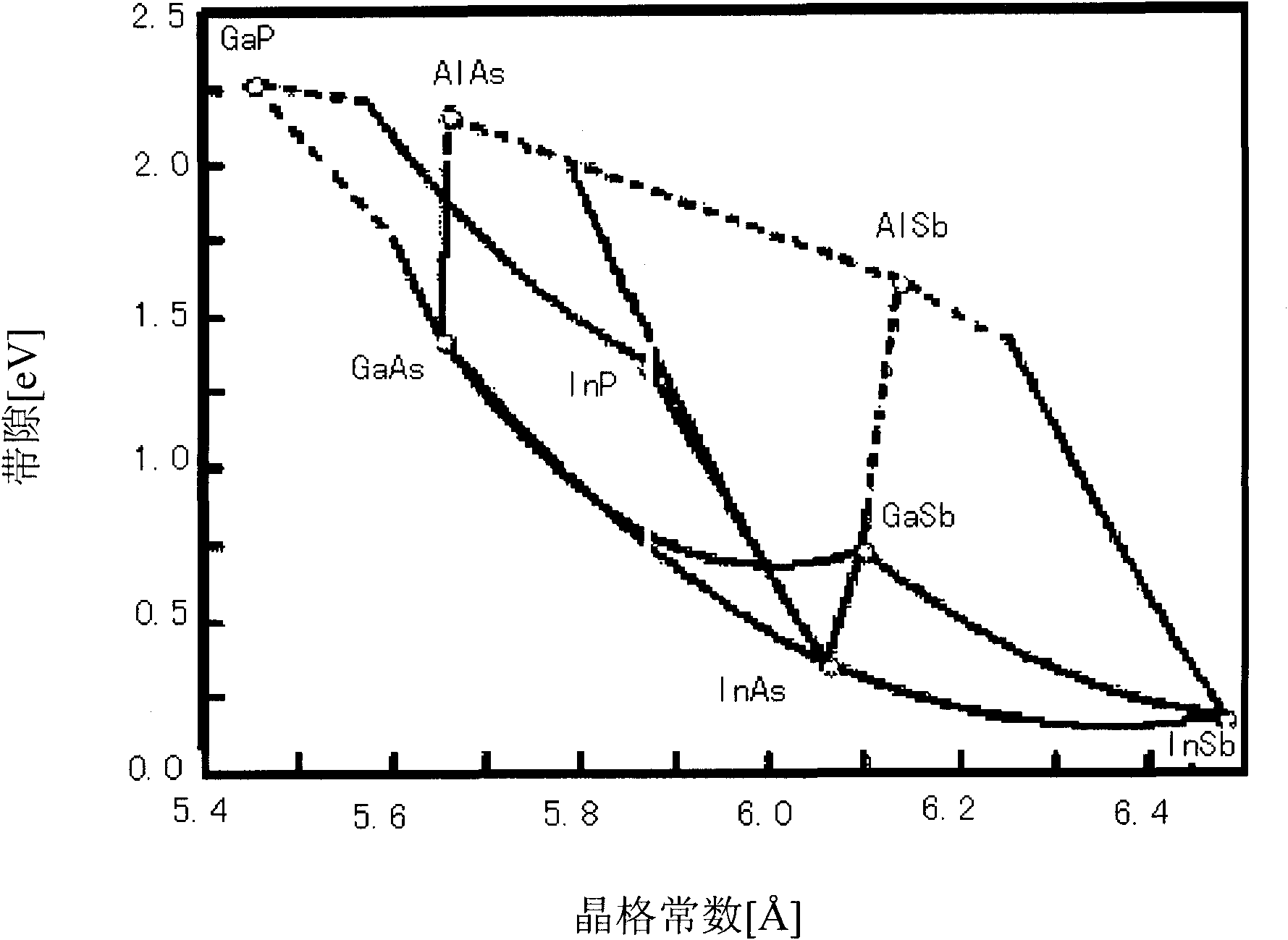

[0021] image 3 The relationship between the band gap and the lattice const...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More