Method and circuit for scheduling data of memory through fast Fourier transform (FFT) reverse operation

A data scheduling and storage technology, applied in energy-saving ICT, complex mathematical operations, memory address/allocation/relocation, etc., can solve problems such as difficult to expand data reordering, complex algorithms and data scheduling

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0059] Below in conjunction with accompanying drawing and example the present invention is described in further detail.

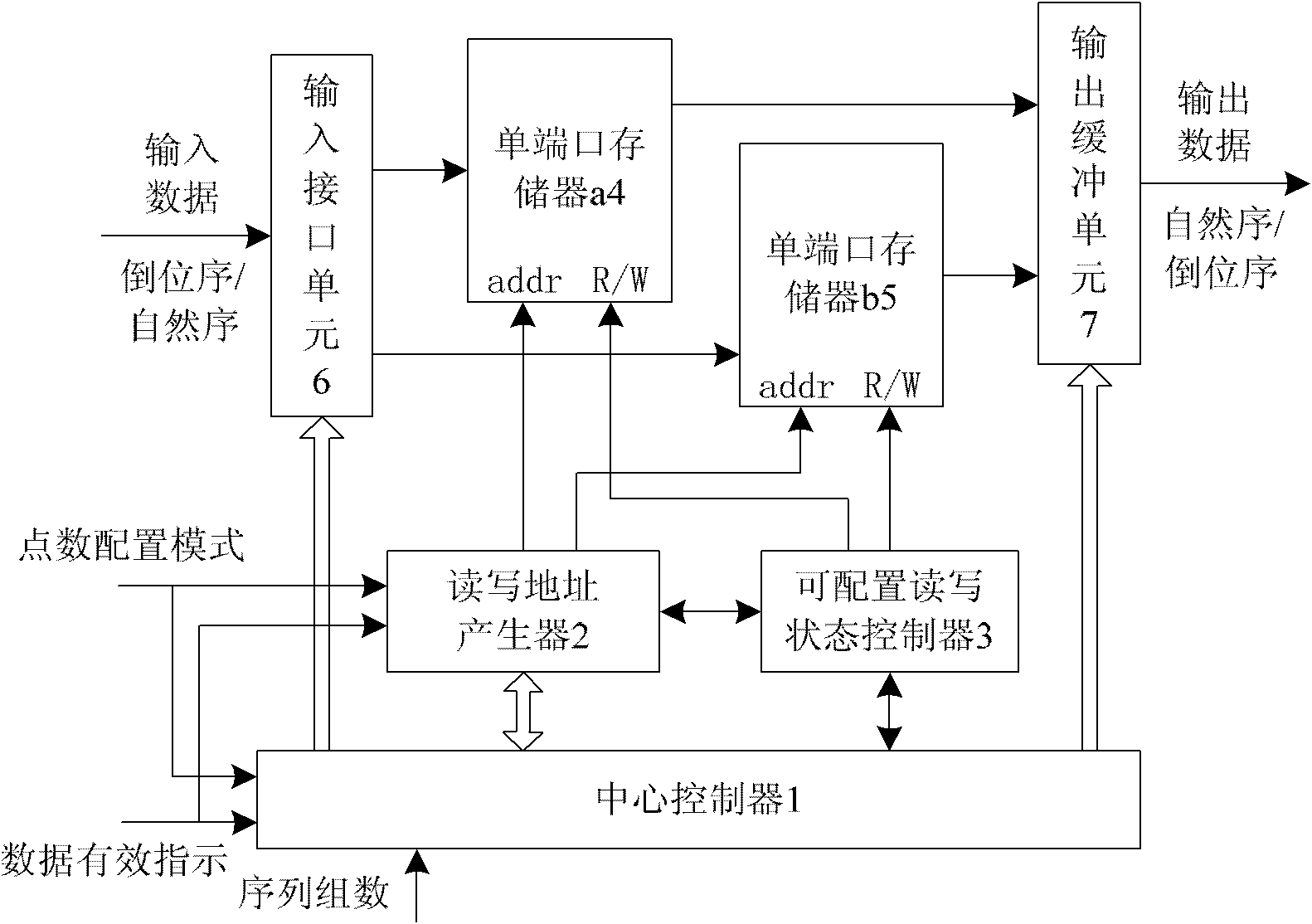

[0060] The VLSI structure proposed by the present invention based on the reverse operation of the N / 2 deep single-port memory is based on the memory data scheduling and the control mode of the finite state machine. Such as figure 1 As shown, the VLSI structure of the present invention includes a central controller 1, a read-write address generator 2, a configurable read-write state controller 3, a single-port memory a4, a single-port memory b5, an input interface unit 6, and an output buffer unit 7.

[0061] The central controller 1 is responsible for the state control and data scheduling of each module in the system. The central controller 1 receives the external data valid indication signal, point configuration mode and sequence group number signal, uses the sequence group number signal as the initial value of the remaining sequence group number indicati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More