Small area electrically removing type rewritable read only memory array

A read-only memory and sub-memory technology, applied in the field of memory arrays, can solve problems such as increasing cost requirements and increasing area costs, and achieve the effect of reducing costs and reducing unit cell area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

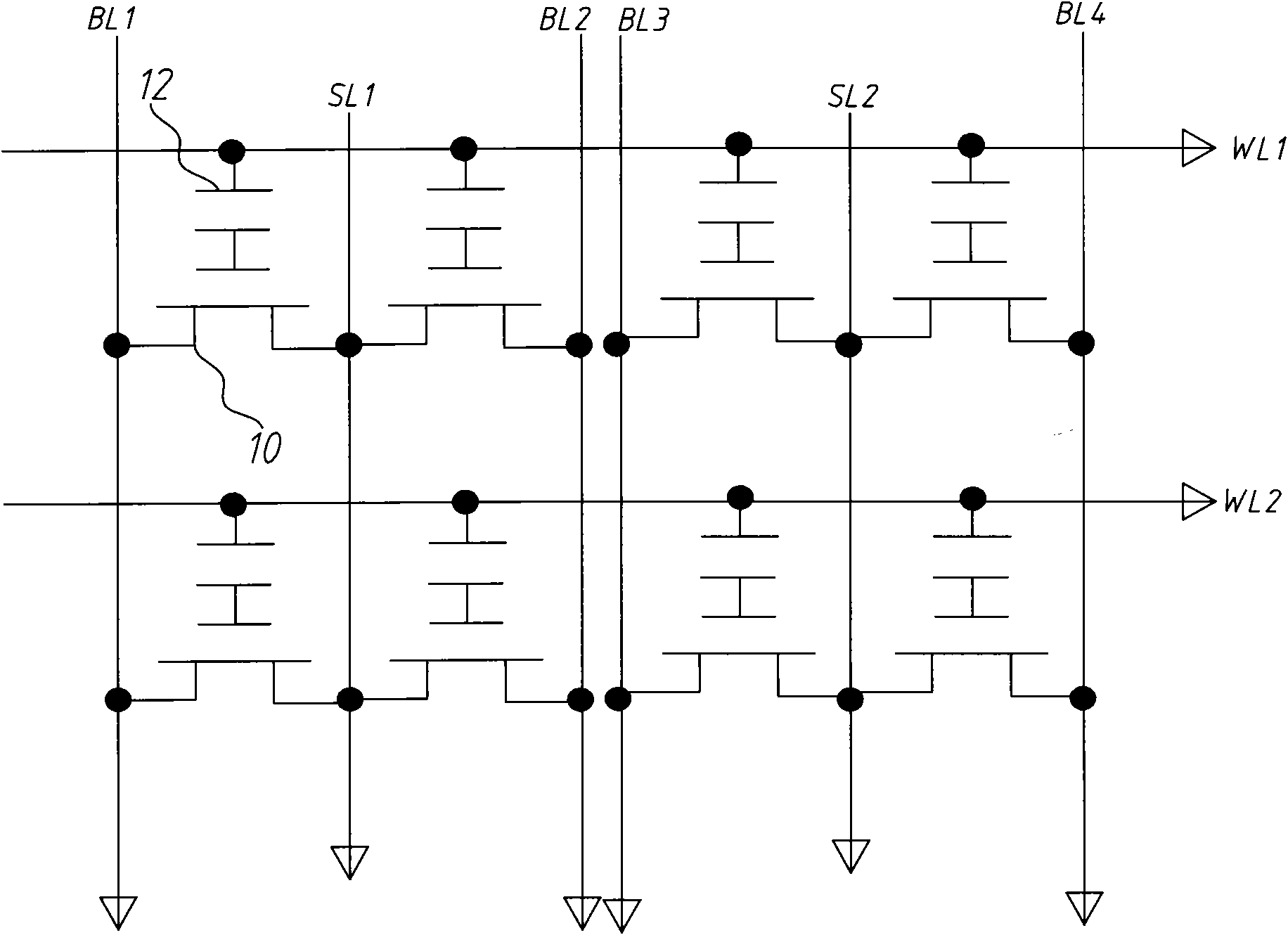

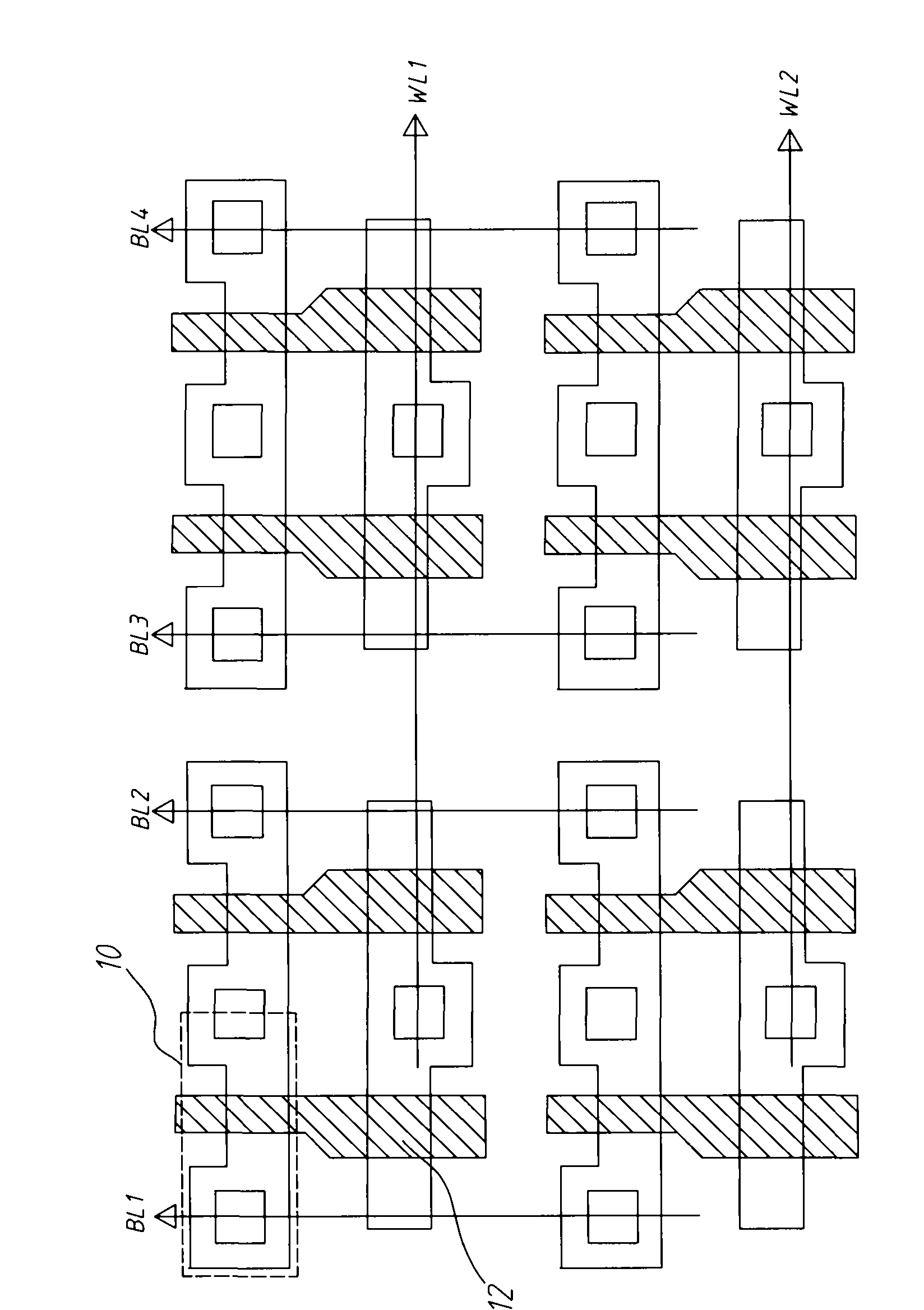

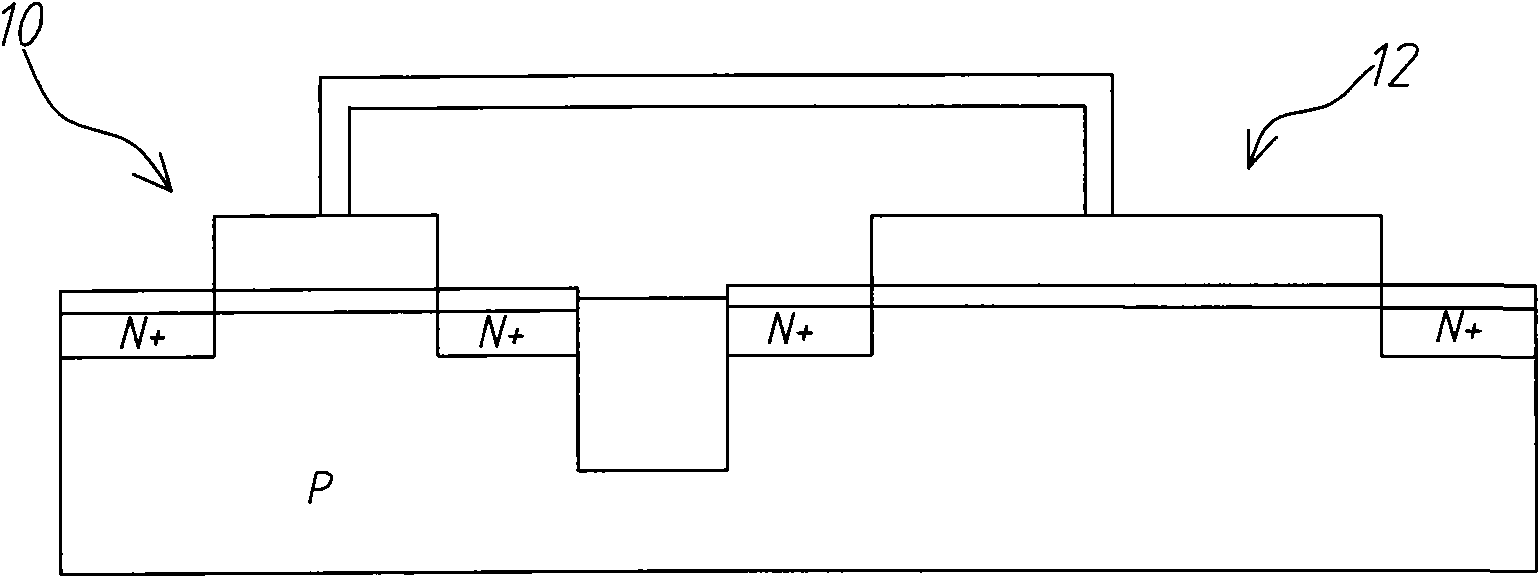

[0021] Please also refer to the following Figure 4 and Figure 5 , to introduce the first embodiment. The present invention includes a plurality of parallel bit lines 14, which are divided into multiple sets of bit lines 16, and the multiple sets of bit lines 16 include a first set of bit lines 18 and a second set of bit lines 19. One set of bit lines 18 and the second set of bit lines 19 both include a bit line 14 . There are also a plurality of parallel word lines 20 perpendicular to the bit line 14 , including a first word line 22 . There are a plurality of parallel common source lines 24 parallel to the word line 20 , including a first common source line 26 . The bit lines 14 , word lines 20 and common source lines 24 are connected to a multi-sub-memory array 28 , that is, 2×2 bit memory cells. Each sub-memory array 28 is connected to two sets of bit lines 16 , two word lines 20 and a common source line 24 , and each sub-memory array 28 is located between two adjacent...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More