Semiconductor PiP (package in package) system structure and manufacturing method thereof

A technology of packaging and system structure in packaging, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc. The effect of wire bonding quality, preventing bridging phenomenon, and improving cutting efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0066] The present invention is described in detail below in conjunction with accompanying drawing:

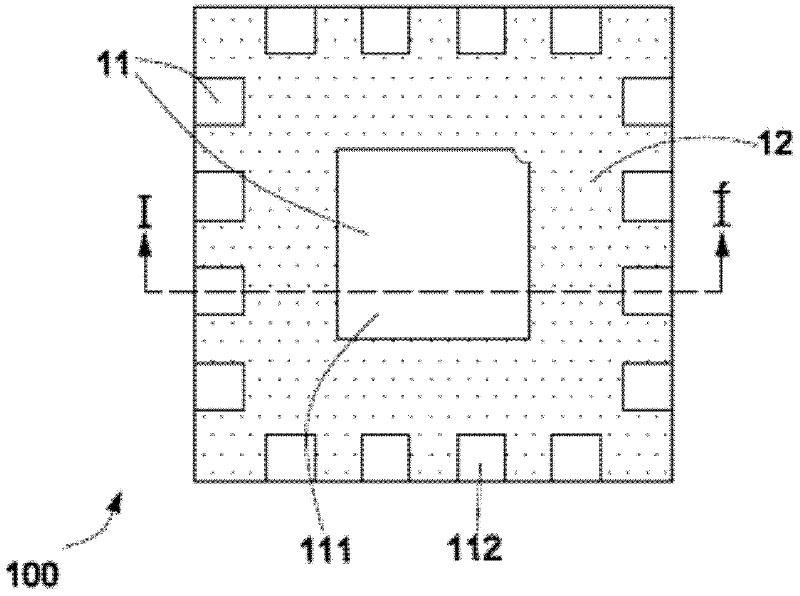

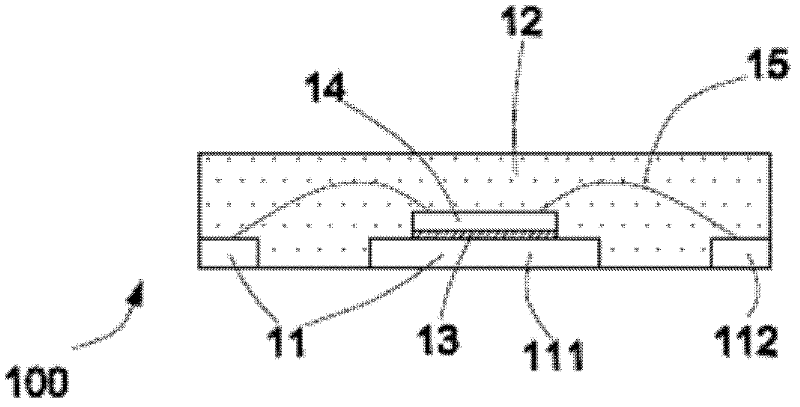

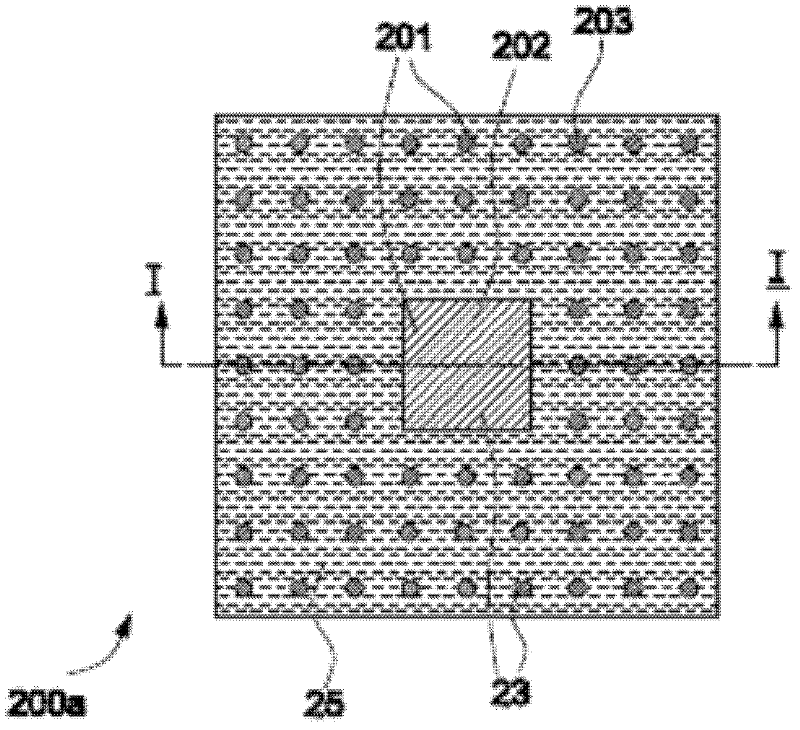

[0067] Figure 2A A schematic diagram of the rear side of a semiconductor package-in-package (PiP) system structure in which the cross-section of the pins is circular and the pins on each side of the chip carrier are arranged in parallel according to the embodiment of the present invention. Figure 2B A schematic diagram of the rear side of a semiconductor package-in-package (PiP) system structure drawn for an embodiment of the present invention in which the cross-section of the pins is rectangular and the pins on each side of the chip carrier are arranged in parallel.

[0068] Refer to the above Figure 2A -B It can be seen that, in this embodiment, the lead frames 201 of the semiconductor package-in-package (PiP) system structures 200a and 200b include a chip carrier 202 and pins 203 arranged in multiple circles around the chip carrier 202, and the chip carrier 202 The pin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More