Method for forming semiconductor device

A semiconductor and device technology, applied in the field of semiconductor device formation, can solve the problems of reducing the interface state of the gate oxide layer, reducing the probability of carrier trapping, etc., and achieve the effects of reducing silicon dangling bonds and suppressing thermionic effect.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

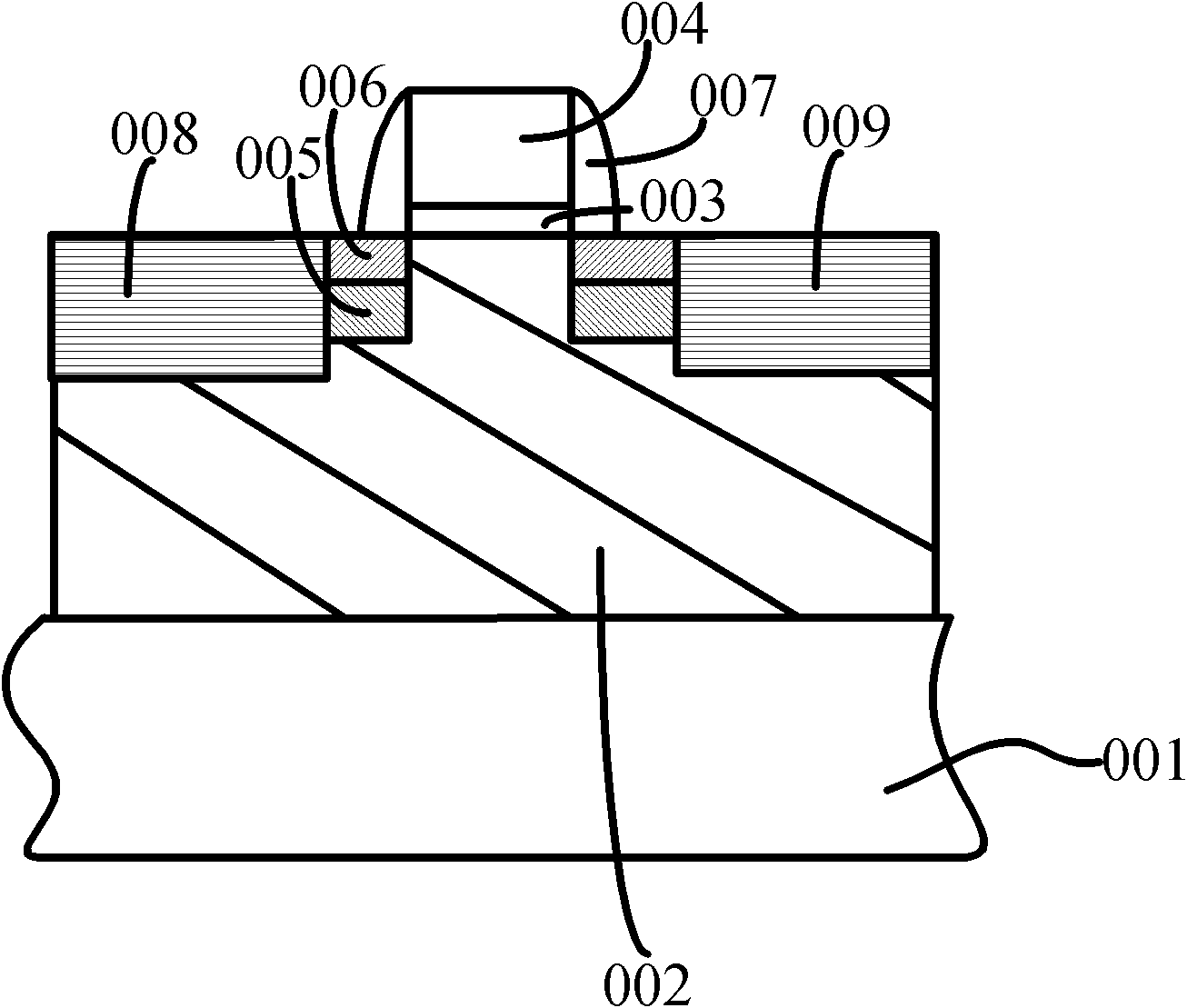

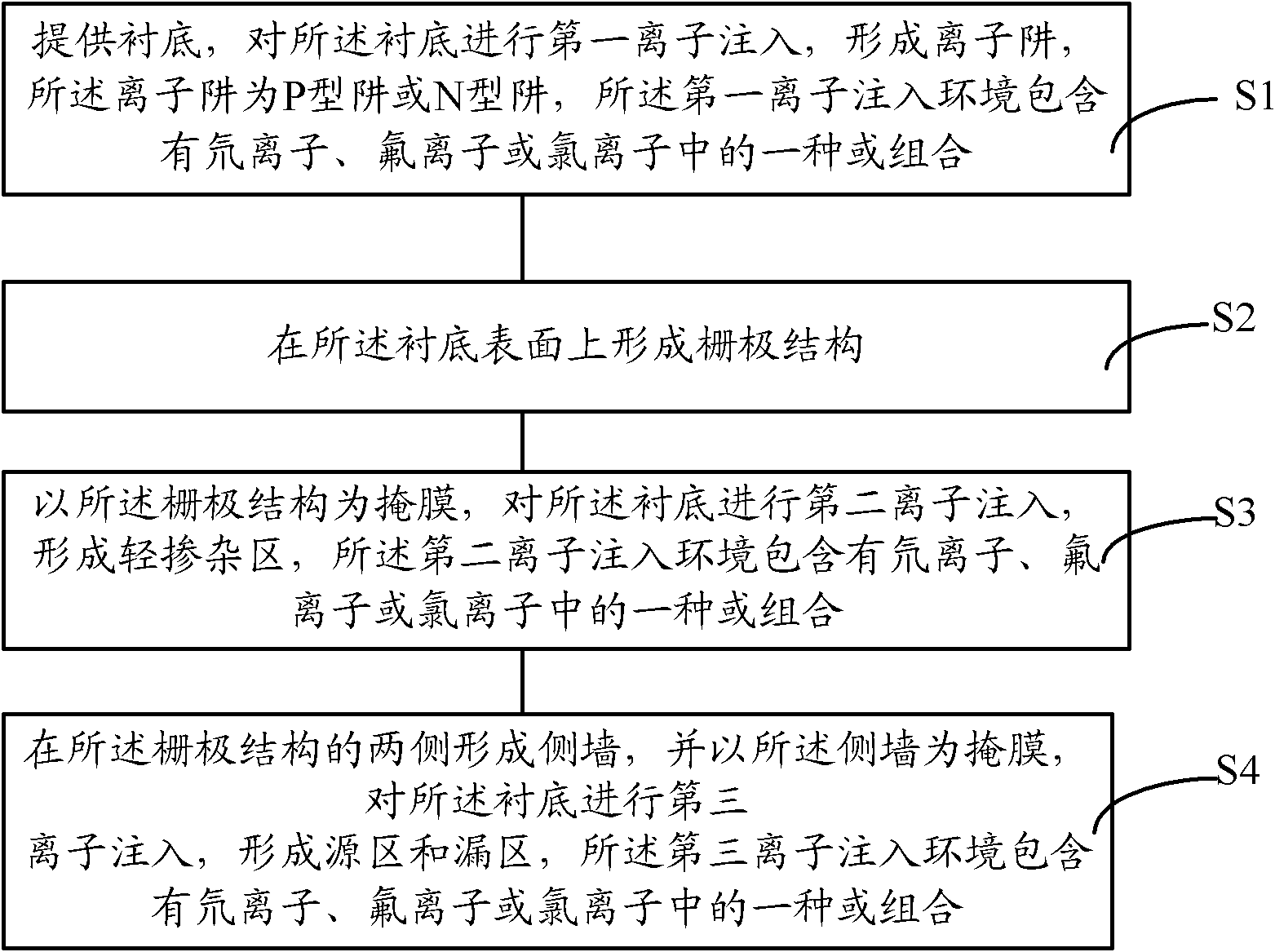

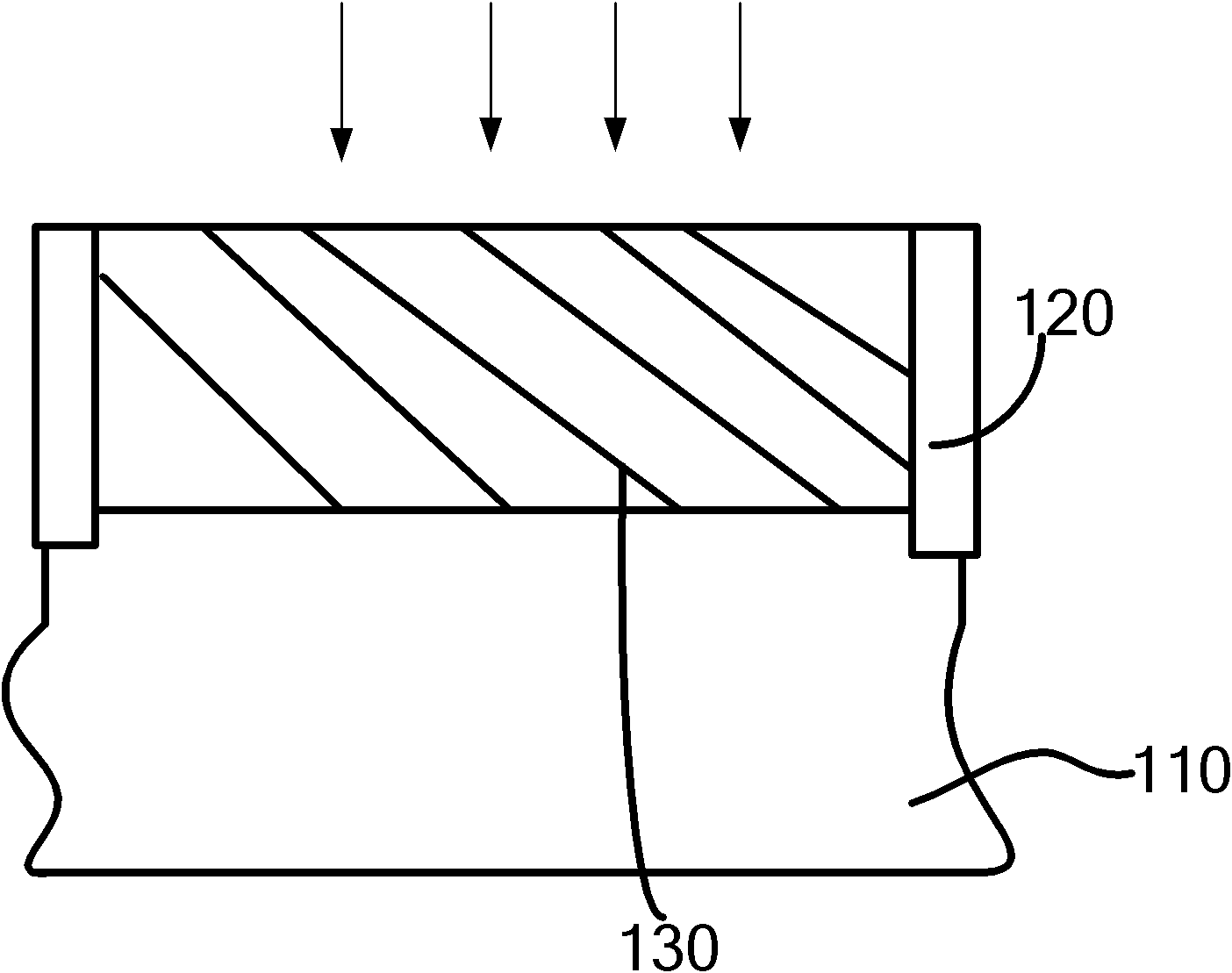

[0034] The present invention provides a method for forming a semiconductor device, which includes providing a substrate, performing a first ion implantation on the substrate to form an ion trap; forming a gate structure on the surface of the substrate; taking the gate structure as Mask, perform a second ion implantation on the substrate to form a lightly doped region, including a lightly doped source region and a lightly doped drain region; form sidewalls on both sides of the gate structure, and use the The sidewall is a mask, and a third ion implantation is performed on the substrate to form a heavily doped region, including a heavily doped source region and a heavily doped drain region; wherein the first ion implantation environment and the second ion implantation environment One ion implantation environment or multiple ion implantation environments in the third ion implantation environment also contains one or a combination of deuterium ions, fluoride ions, or chloride ions. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More