Substrate for mounting semiconductor chip and method for producing same

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as short-circuit faults, connection reliability, and wire-bondability degradation, and achieve good wire-bondability, Effect of Good Solder Connection Reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment approach

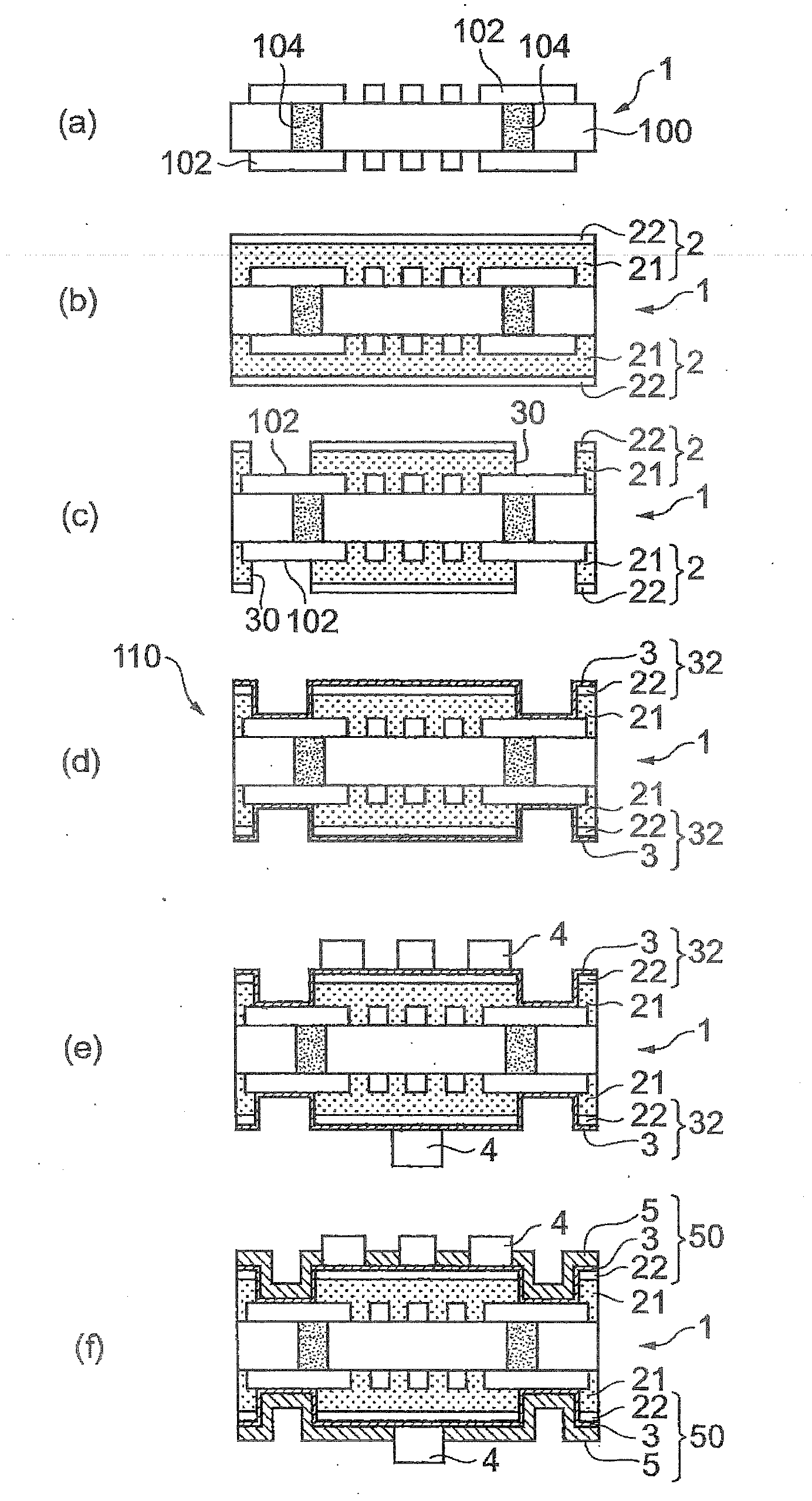

[0075] A preferred first embodiment of the method of manufacturing a substrate for mounting a semiconductor chip will be described below. figure 1 with 2 It is a process drawing which schematically shows the manufacturing method of the board|substrate for mounting a semiconductor chip concerning 1st Embodiment. This embodiment is an example of a method of manufacturing a substrate for mounting a semiconductor chip using a semi-additive method in which an outer layer circuit is formed using a resin with copper foil on the inner layer board.

[0076] In this embodiment, first, if figure 1 As shown in (a), the inner layer plate 1 is prepared. The inner-layer board 1 has: an inner-layer substrate 100, an inner-layer circuit 102 provided on its surface, and an inner-layer through-circuit formed to penetrate the inner-layer substrate and electrically connect the inner-layer circuits 102 on both surfaces. Hole 104. As each configuration in the inner layer board 1 , known configur...

no. 2 Embodiment approach

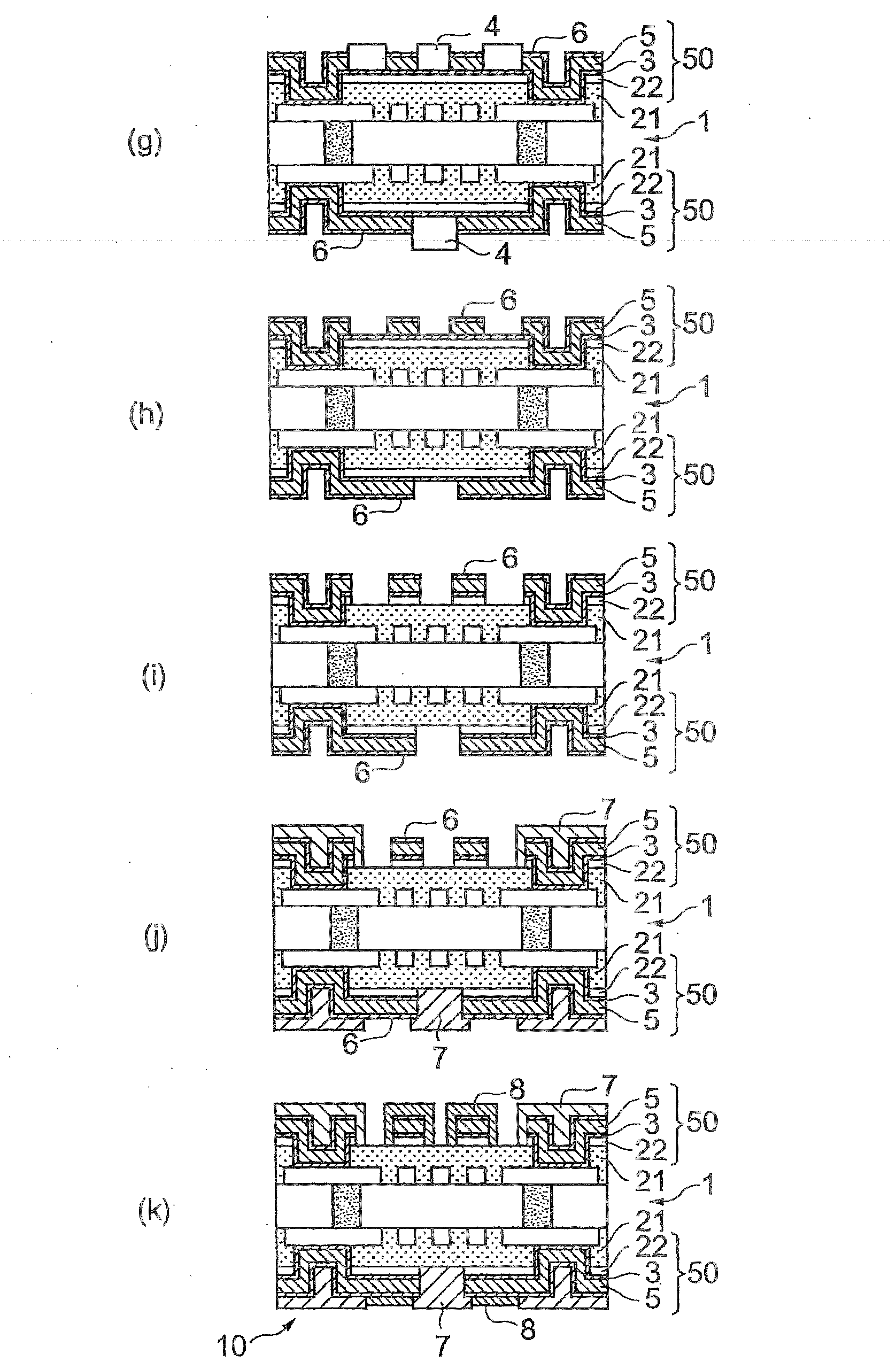

[0138] Next, a preferred second embodiment of the method of manufacturing a substrate for mounting a semiconductor chip will be described. Image 6 with 7It is a process drawing which schematically shows the manufacturing method of the board|substrate for mounting a semiconductor chip concerning 2nd Embodiment. This embodiment is an example of a method of manufacturing a substrate for mounting a semiconductor chip using a semi-additive method, and includes a step of forming a copper plating layer after laminating a composite film on an inner layer board.

[0139] In this embodiment, first, if Image 6 As shown in (a), the inner layer plate 1 is prepared. This inner layer panel 1 can be prepared in the same manner as in the first embodiment described above. Secondly, if Image 6 As shown in (b), the insulating layer 15 is formed by laminating or pressing a composite film on both surfaces of the inner layer board 1 . The composite film is a non-conductive film and is formed...

Embodiment 1

[0174] (Manufacturing of substrates for mounting semiconductor chips)

[0175] (1a) Preparation of the inner plate

[0176] First, if figure 1 As shown in (a), MCL-E-679 (manufactured by Hitachi Chemical Industries, Ltd., manufactured by Hitachi Chemical Industry Co., Ltd. trade name), the copper foil at unnecessary parts was removed by etching to form through-holes, and an inner-layer board (inner-layer board 1) having an inner-layer circuit formed on the surface was obtained.

[0177] (1b) Lamination of copper foil with resin

[0178] Such as figure 1 As shown in (b), MCF-7000LX (manufactured by Hitachi Chemical Industries, Ltd., trade name) coated with an adhesive (insulating layer 21) on a 3 μm thick copper foil 22 was heated at 170° C. 30kgf / cm 2 Under the condition of heating and pressing for 60 minutes, lamination is carried out.

[0179] (1c) Formation of IVH

[0180] Such as figure 1 As shown in (c), IVH30, which is a non-through hole with a diameter of 80 μm,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More