Multi-porous channel current equalizing-based transient voltage suppressor

A transient voltage suppression, multi-channel technology, applied in the direction of electric solid devices, circuits, electrical components, etc., can solve the problems of loss of ESD protection performance, anti-ESD ability, slow data transmission speed, etc., to enhance anti-ESD ability , to avoid local failure, the effect of short response time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

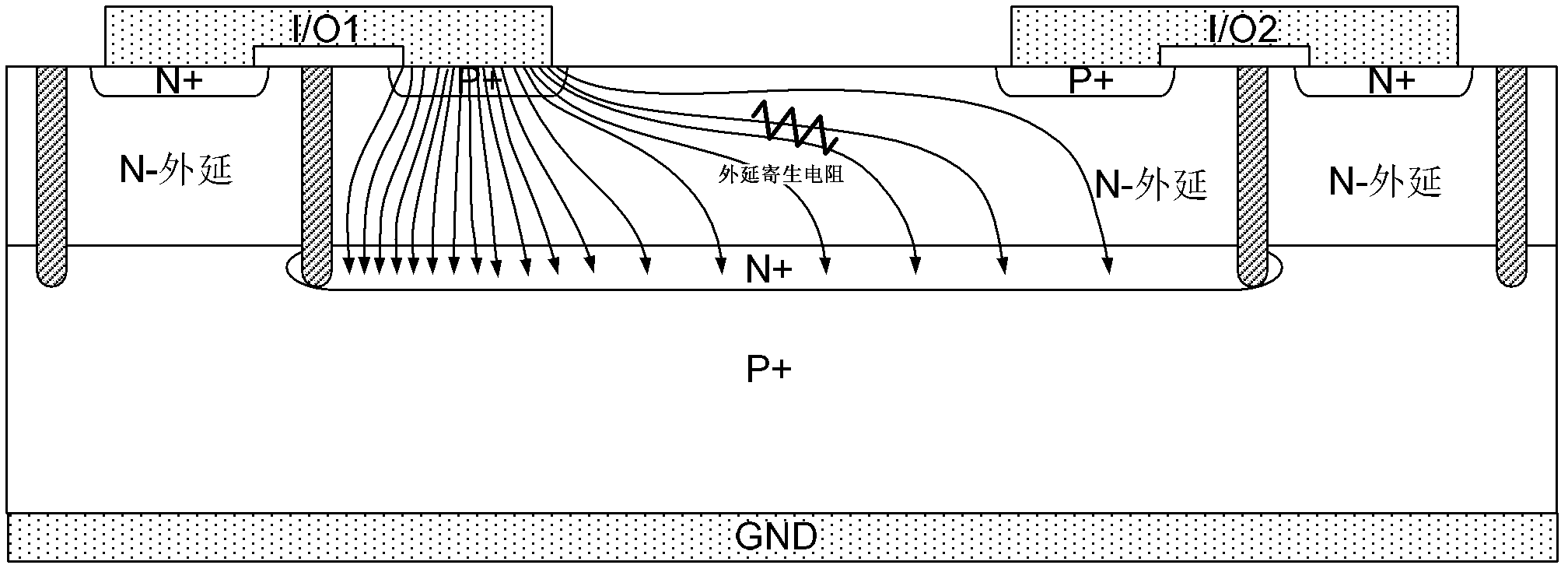

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

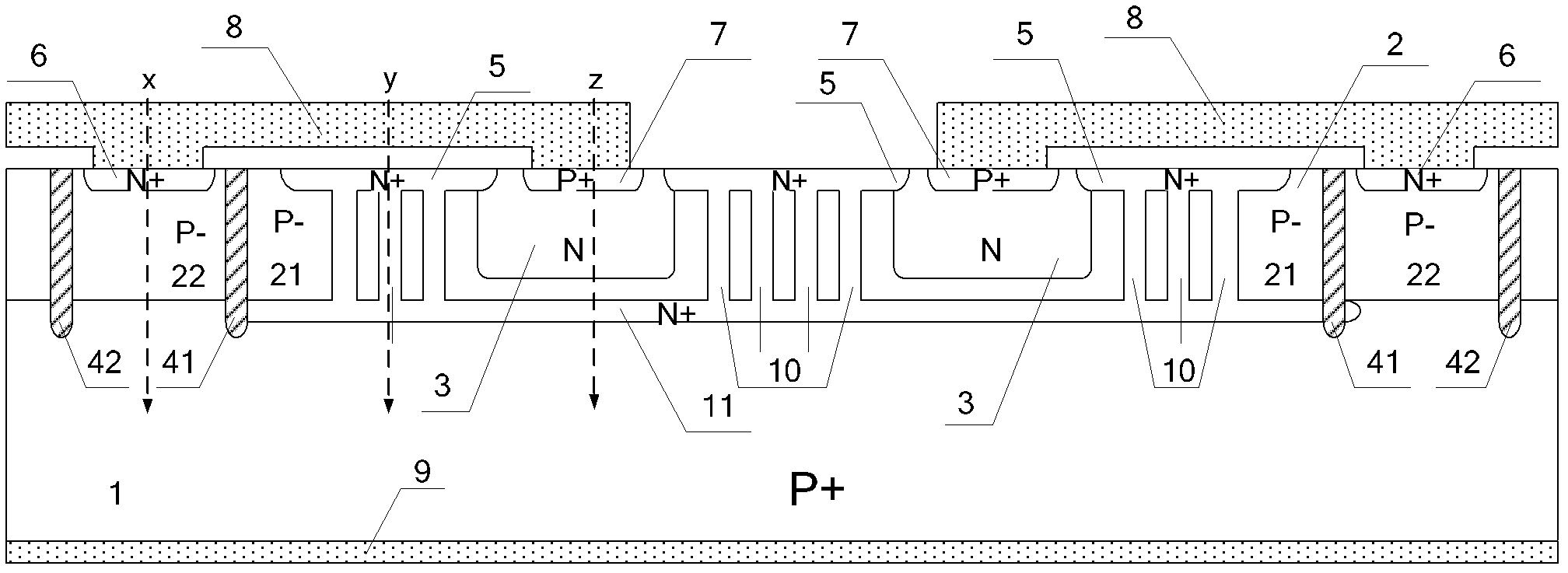

[0035] In order to describe the present invention more specifically, the technical solutions and related principles of the present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

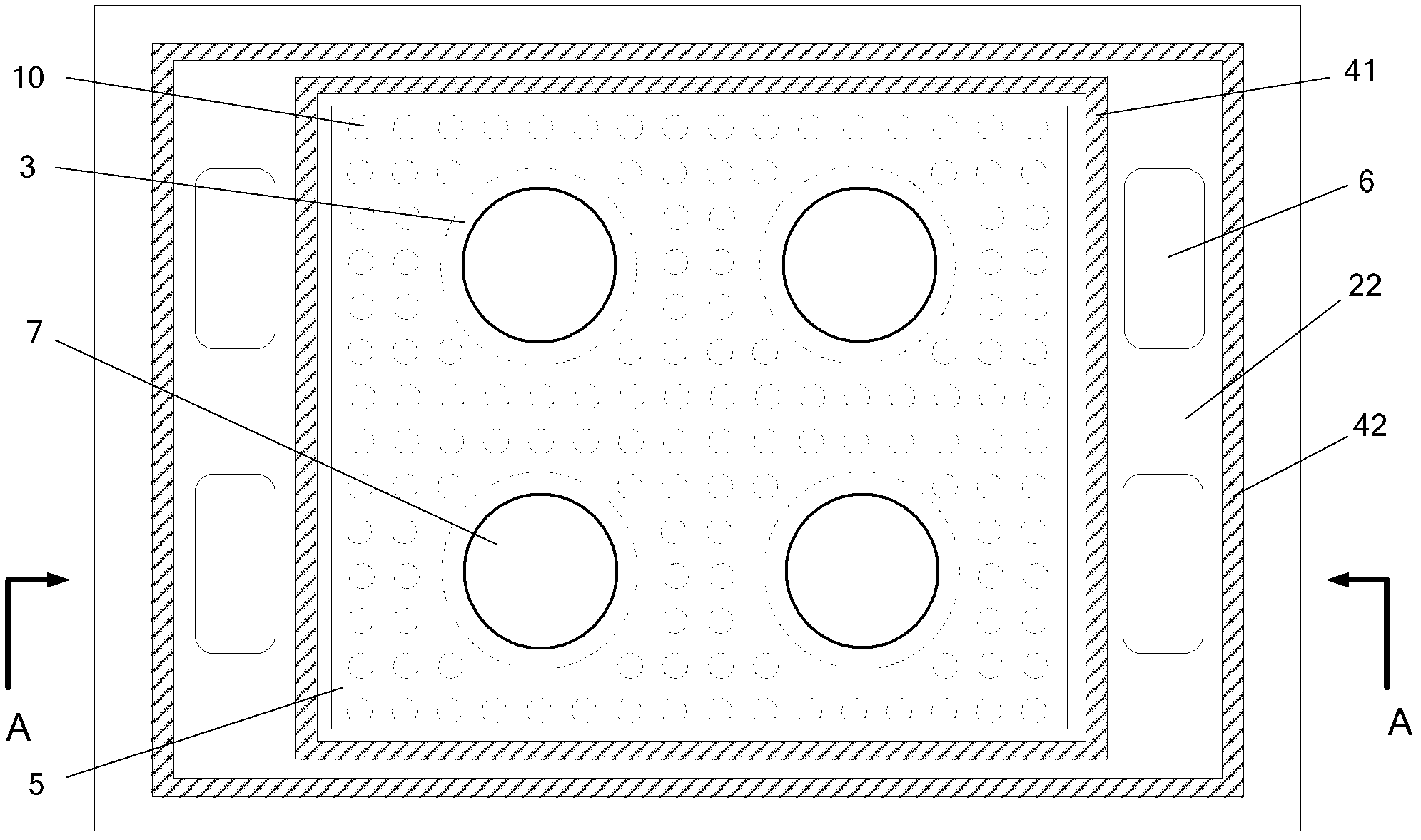

[0036] Such as figure 2 and image 3 As shown, a transient voltage suppressor based on multichannel current sharing includes a P+ substrate layer 1; a P- epitaxial layer 2 is arranged on the P+ substrate layer 1, and a ground electrode 9 is arranged at the bottom of the P+ substrate layer 1; Layer 2 is divided into two regions by the outer isolation ring 42 and the inner isolation ring 41: the first epitaxial region 21 located in the inner isolation ring 41 and the second epitaxial region 22 located between the outer isolation ring 42 and the inner isolation ring 41 ; An N+ buried layer 11 is provided between the first epitaxial region 21 and the P+ substrate layer 1, and four N+ active injection regions 6 are provided on the seco...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com