Method for forming semiconductor structure

A semiconductor and plasma technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of thinning mask layer, stronger physical bombardment of high-energy ions, and slow gas exchange, etc. The effect of eclipse selection ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 2 example

[0071] refer to Figure 10 , Figure 10 It is a schematic flowchart of a method for forming a semiconductor structure according to the second embodiment of the present invention, including:

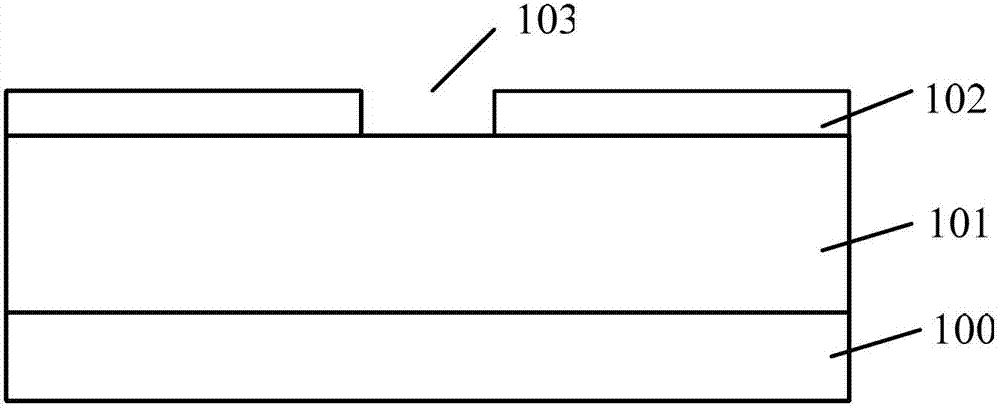

[0072] Step S31, providing a substrate, and forming a dielectric layer on the substrate;

[0073] Step S32, forming a mask layer on the dielectric layer, the mask layer having openings exposing the surface of the dielectric layer;

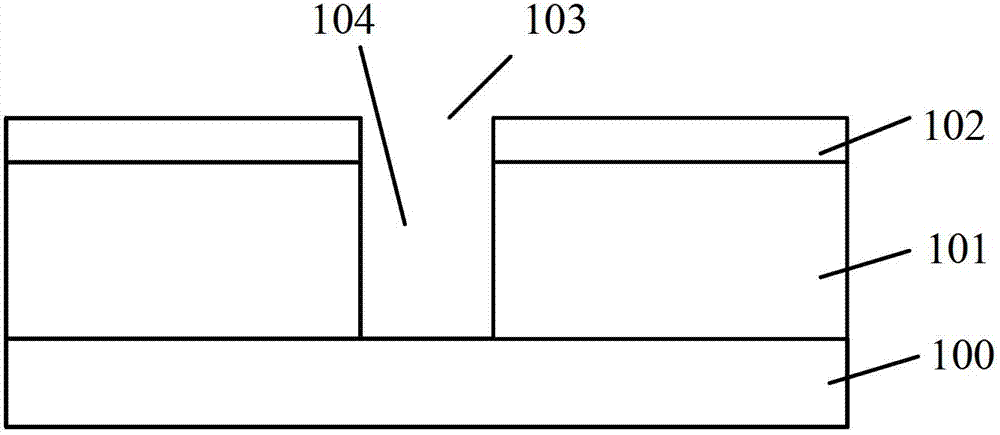

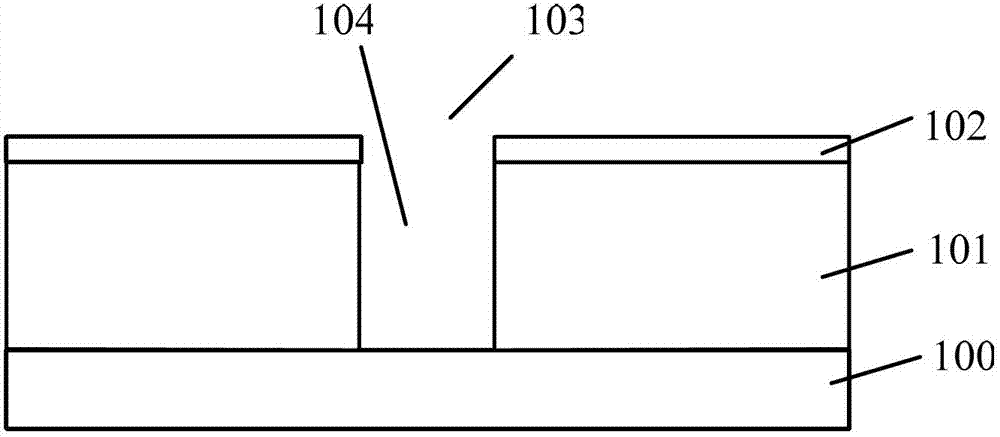

[0074] Step S33, using the mask layer as a mask to perform plasma etching on the dielectric layer, the radio frequency power source outputs radio frequency power in a continuous manner, the bias power source outputs bias power in a pulsed manner, and the bias The first duty cycle of the output pulse of the power source is continuously reduced. When the bias power source is turned on, a part of the dielectric layer is etched to form an etching hole. When the bias power source is turned off, a polymerization layer is formed on the surface of the mask layer. o...

no. 3 example

[0094] refer to Figure 17 , Figure 17 It is a schematic flowchart of a method for forming a semiconductor structure according to the third embodiment of the present invention, including:

[0095] Step S41, providing a base, and forming a dielectric layer on the base;

[0096] Step S42, forming a mask layer on the dielectric layer, the mask layer having openings exposing the surface of the dielectric layer;

[0097] Step S43, using the mask layer as a mask to perform plasma etching on the dielectric layer, the radio frequency power source and the bias power source both output radio frequency power in a pulsed manner, and the radio frequency power source and the bias power source pulse The output frequencies are equal, the second duty cycle of the output pulse of the RF power source remains unchanged, the first duty cycle of the output pulse of the bias power source is equal to the second duty cycle of the output pulse of the RF power source, when the RF power source is turn...

no. 4 example

[0118] refer to Figure 23 , Figure 23 It is a schematic flowchart of a method for forming a semiconductor structure according to a fourth embodiment of the present invention, including:

[0119] Step S51, providing a substrate, and forming a dielectric layer on the substrate;

[0120] Step S52, forming a mask layer on the dielectric layer, the mask layer having openings exposing the surface of the dielectric layer;

[0121] Step S53, using the mask layer as a mask to perform plasma etching on the dielectric layer, the radio frequency power source and the bias power source both output radio frequency power in a pulsed manner, and the radio frequency power source and the bias power source pulse The output frequencies are equal, the second duty cycle of the output pulse of the RF power source remains unchanged, the first duty cycle of the output pulse of the bias power source is smaller than the second duty cycle of the output pulse of the RF power source, when the RF power s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More