Manufacturing method for back contact crystalline silicon solar cell

A technology for a solar cell and a manufacturing method, applied in the field of solar cells, can solve the problems of increasing the production cost of the cell, reducing the parallel resistance of the cell, and being prone to leakage, so as to reduce the laser isolation process, reduce the risk of leakage, and reduce the cost of equipment. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

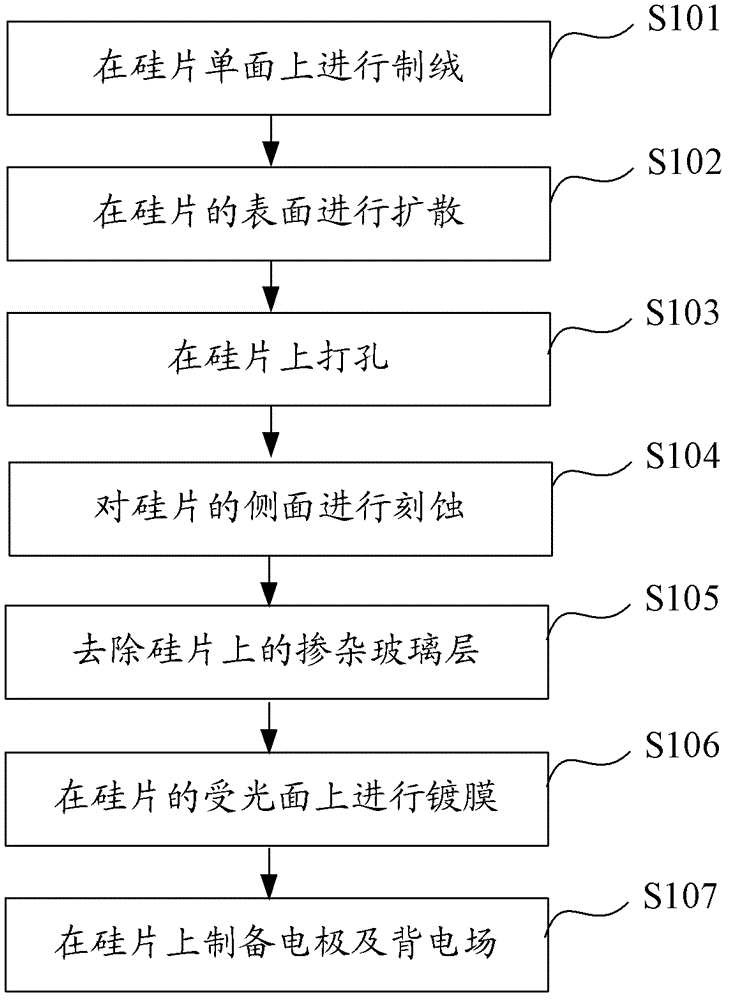

[0052] Please refer to figure 1 , figure 1 The flow chart of the method for manufacturing the back contact crystalline silicon solar cell provided in the first embodiment, as shown in figure 1 As shown, the method includes the following steps:

[0053] Step S101: performing texturing on one side of the silicon wafer to form a surface structure;

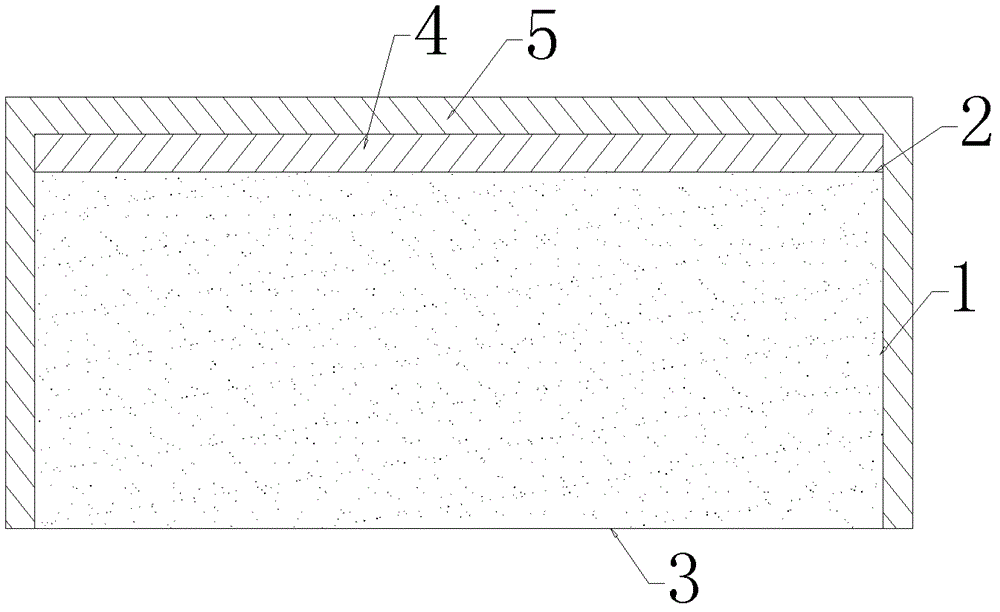

[0054]In the embodiment of the present invention, texturing is selected to be carried out on one side of the silicon wafer 1. The purpose of texturing is to form an uneven structure on the originally bright silicon wafer surface through a chemical reaction to prolong the propagation path of light on the surface, thereby Improve the absorption of light by the silicon wafer. The schematic diagram of the structure of the silicon wafer after texturing is as follows: figure 2 As shown in the figure, 1 is a silicon wafer, 2 is a light-receiving surface, 3 is a backlight surface, and 4 is a suede surface. In addition, oil and metal imp...

Embodiment 2

[0073] Please refer to Figure 8 , Figure 8 A flow chart of a method for manufacturing a back-contact crystalline silicon solar cell provided in Example 2, as shown in Figure 8 As shown, the method includes the following steps:

[0074] Step S201: performing texturing on both surfaces of the silicon wafer to form a surface structure;

[0075] The schematic diagram of the structure of the silicon wafer after texturing is as follows: Figure 9 As shown, the suede 4 is formed on both surfaces of the silicon wafer 1 in the figure.

[0076] Step S202: Diffusion on the surface of the silicon wafer to form a P-N junction;

[0077] The schematic diagram of the structure of the silicon wafer after diffusion is shown in Figure 10 As shown in Figure 5, there are emitter junctions diffused on both surfaces and side surfaces of the silicon wafer 1.

[0078] Compared with the steps S101-S103, the above two steps are only that texturing and diffusion are carried out on both sides of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More