B4-flash device and manufacture method thereof

A manufacturing method and device technology, which is applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve the problems of limiting gate length, etc., and achieve the effects of improving performance, reducing the remaining hole volume, and saving costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

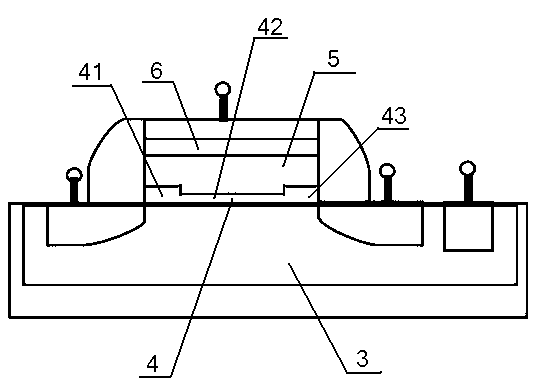

[0020] The present invention will be explained in detail below in conjunction with the accompanying drawings.

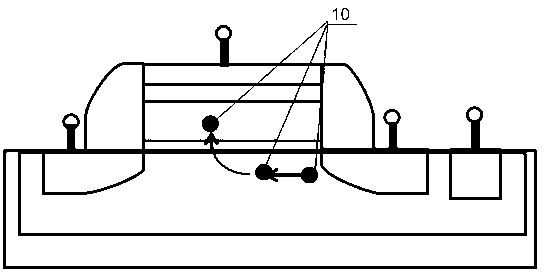

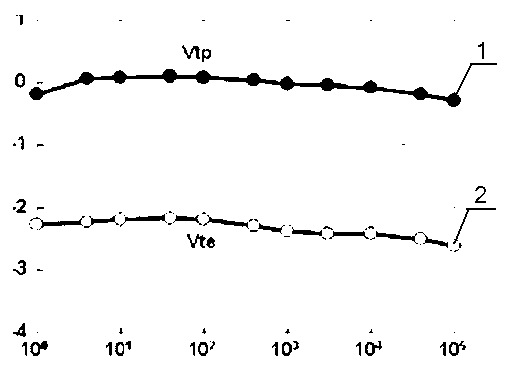

[0021] For the 60nm SONOS structure, the substrate bias assisted band to band tunneling-induced hot electron injection (Bulk Bias assisted Band to Band induced hot electron injection) is used to compile, and the hole tunneling injection of FN is used to achieve erasure. Compared with other structures, it has many advantages. Both electrons and holes act on the silicon oxide layer during its cycle, but the programming and erasing voltages still vary periodically. Such as figure 2 As shown in , wherein, line segment 1 and line segment 2 represent the change of the ordinate voltage of programming and erasing with the side length of the abscissa cycle. It can be seen from the figure that the trend of compiling and erasing states decreases at the same time (the actual required voltage gradually increases). Since the operating window does not change significantly, it me...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More