Wafer level packaging structure and manufacturing method thereof

A technology of wafer-level packaging and manufacturing methods, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as long drilling time, increased drilling difficulty, and increased laser processing costs, and achieve improved Yield rate, effect of reducing drilling difficulty and time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] In order to make the above objects, features and advantages of the present invention more comprehensible, preferred embodiments of the present invention are exemplified below and described in detail in conjunction with the accompanying drawings. Furthermore, the directional terms mentioned in the present invention, such as "up", "down", "front", "back", "left", "right", "inside", "outside", "side", etc., It is only for orientation with reference to the attached drawings. Therefore, the directional terms used are used to illustrate and understand the present invention, but not to limit the present invention.

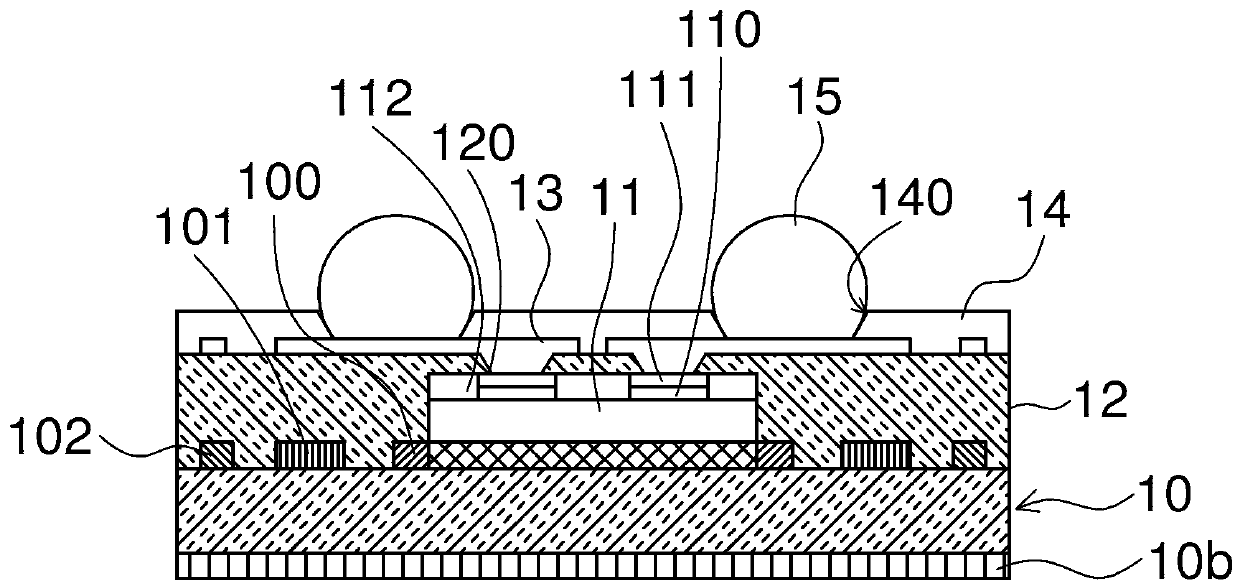

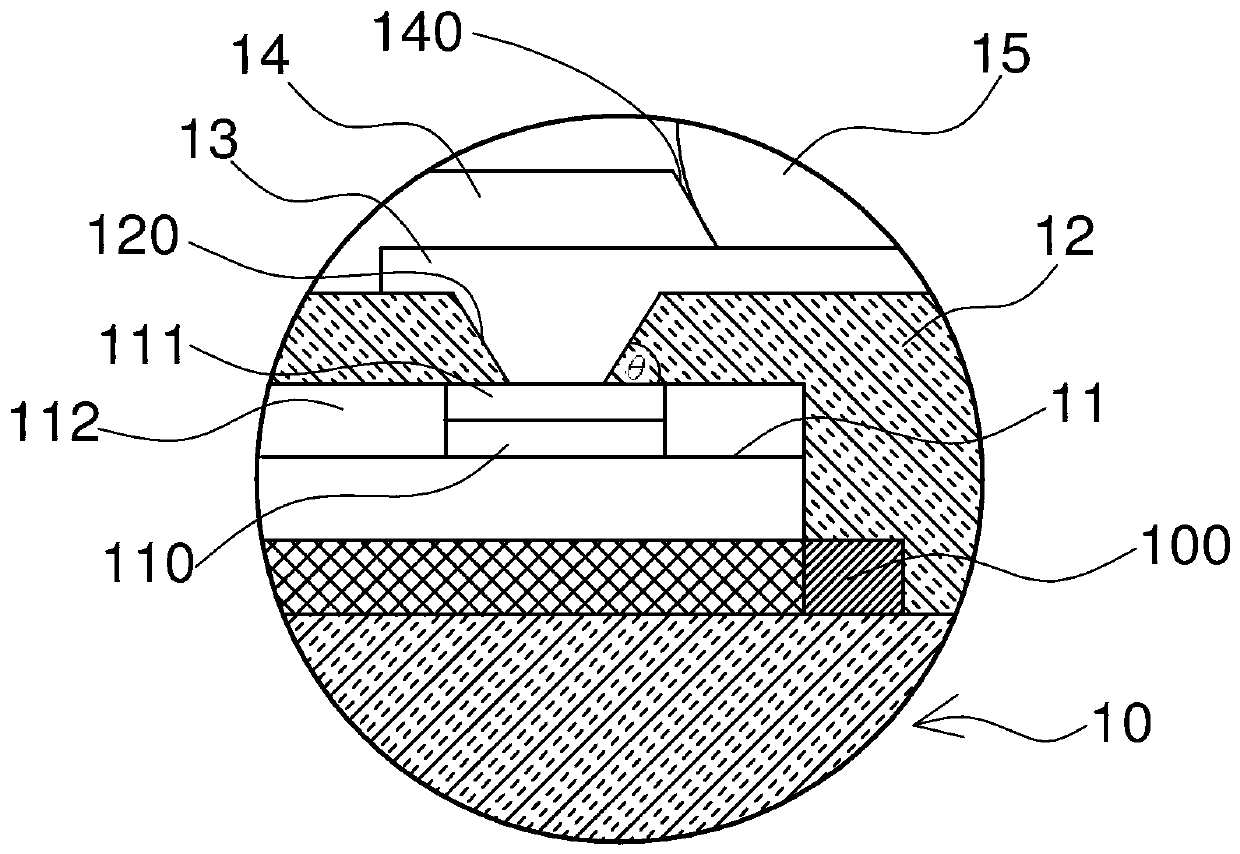

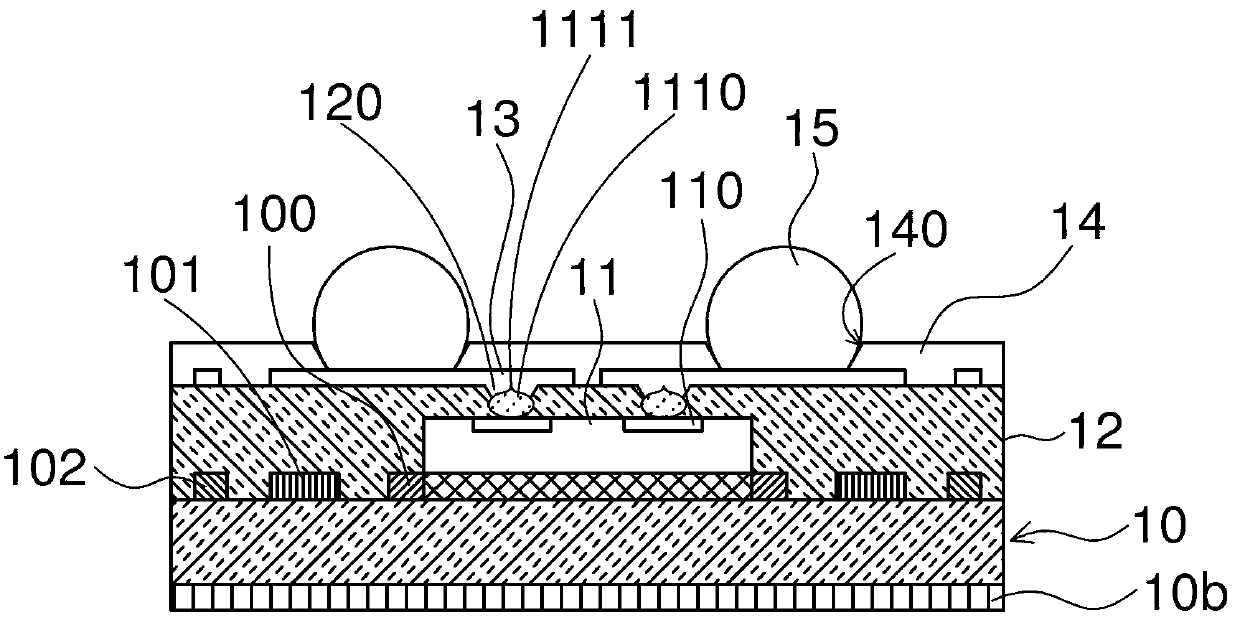

[0026] Please refer to figure 1 as shown, figure 1 is a schematic structural diagram of a wafer-level packaging structure according to an embodiment of the present invention. The wafer-level packaging structure disclosed in the present invention is a fan-out wafer-level packaging structure, including a support layer 10, a chip 11, an insulating layer 12, a rewir...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More