A method for emulating large-capacity memory by imitating netlist after simplifying memory

A large-capacity memory and memory technology, which is applied in instruments, special data processing applications, electrical digital data processing, etc., can solve problems such as difficulty in simulation of large SRAMs, and achieve the effect of reducing simulation difficulty and improving simulation speed.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

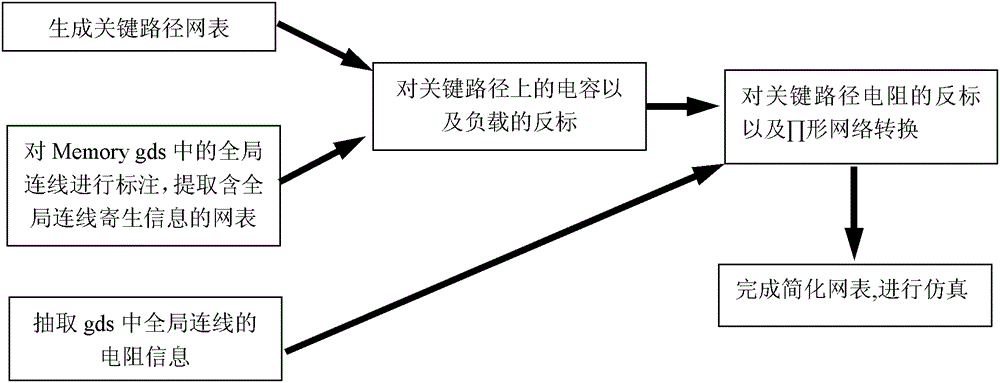

[0020] After simplifying the memory of the present invention, imitating the netlist to realize the method for large-capacity memory simulation, its flow chart is as follows figure 1 As shown, the steps include:

[0021] 1) formulate the critical path, and generate the netlist of the critical path; wherein, the generation method of the critical path is as follows:

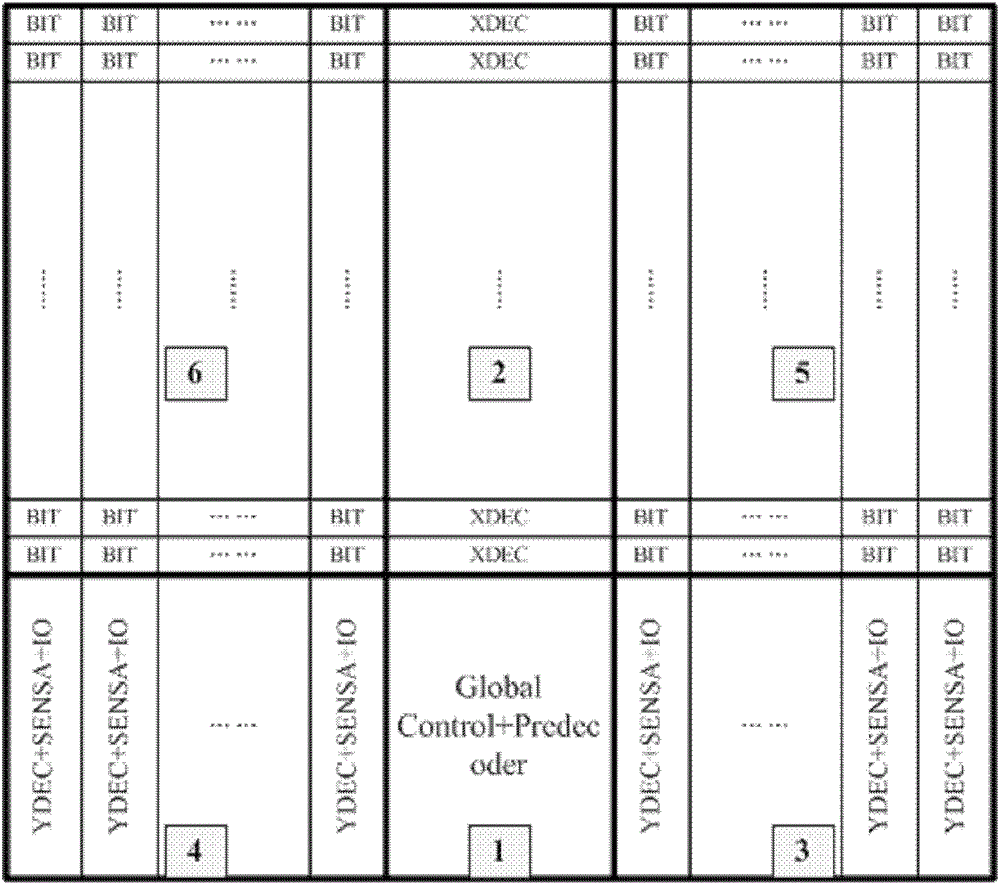

[0022] According to a general SRAM structure block diagram (such as figure 2 As shown), the SRAM is divided into 6 structural blocks (the structural blocks surrounded by the thickest black line in the figure), and each block is numbered separately:

[0023] Structural block 1 is a control signal generation circuit, such as clock signal generation, input signals such as address, write enable (writeenable) signal latch, and address pre-decoding circuit; the circuit structure of structural block 1 has no rules;

[0024] Structural block 2 is the decoding circuit XDEC in the X direction, which is composed of identica...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More