Quantum well semiconductor and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of low luminous efficiency of medium and large-sized chips, reduce junction temperature, prevent excessive reverse current, and reduce forward voltage Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

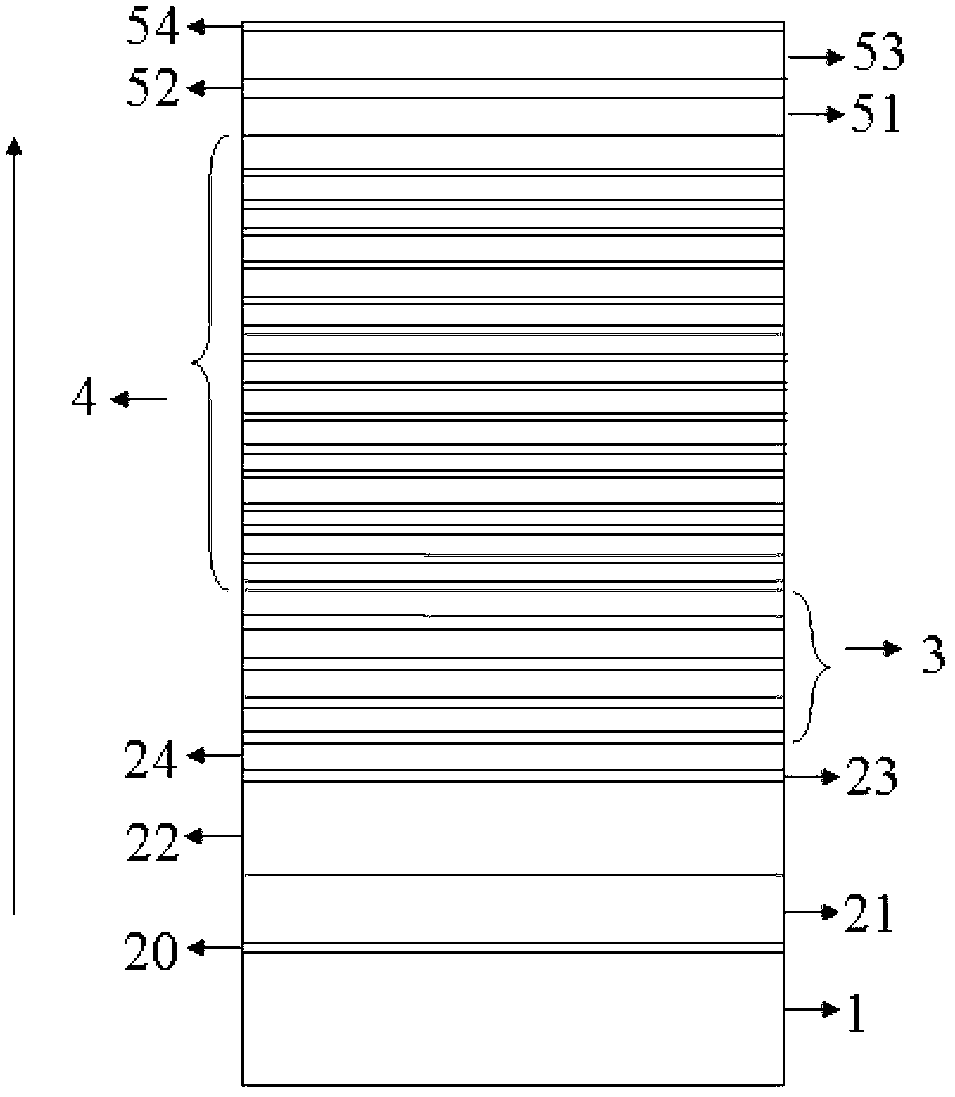

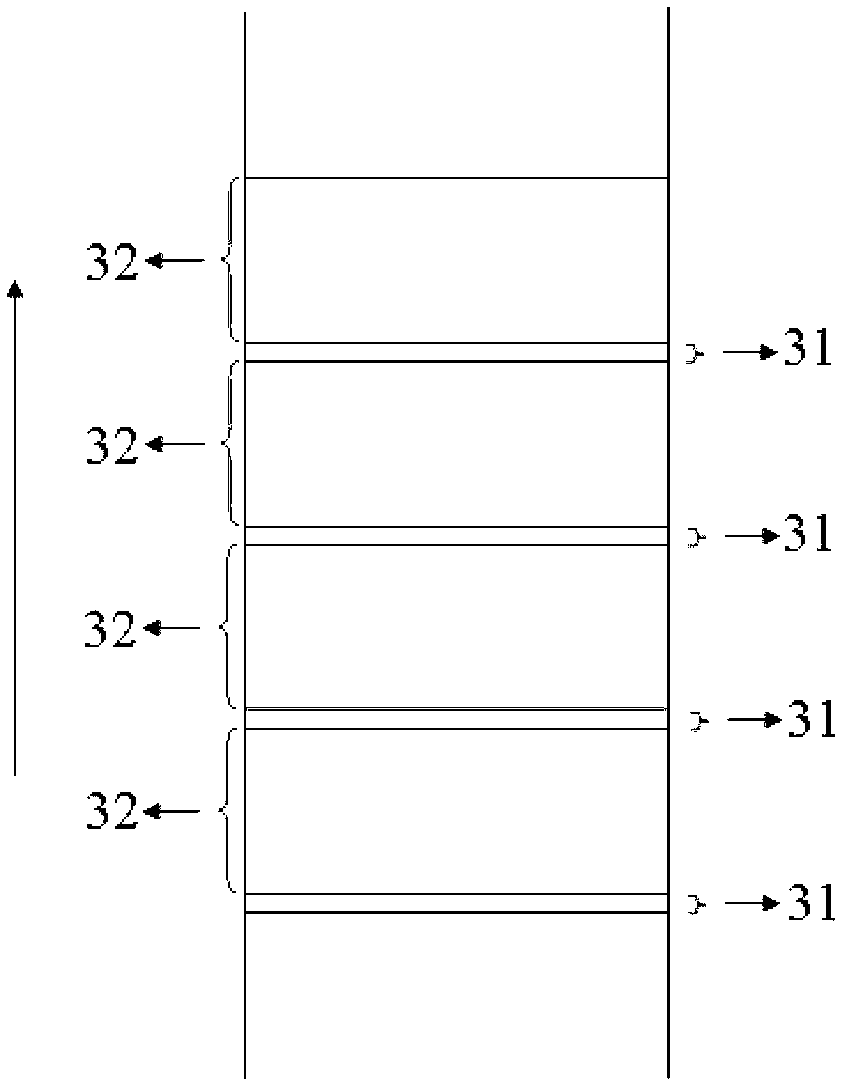

Image

Examples

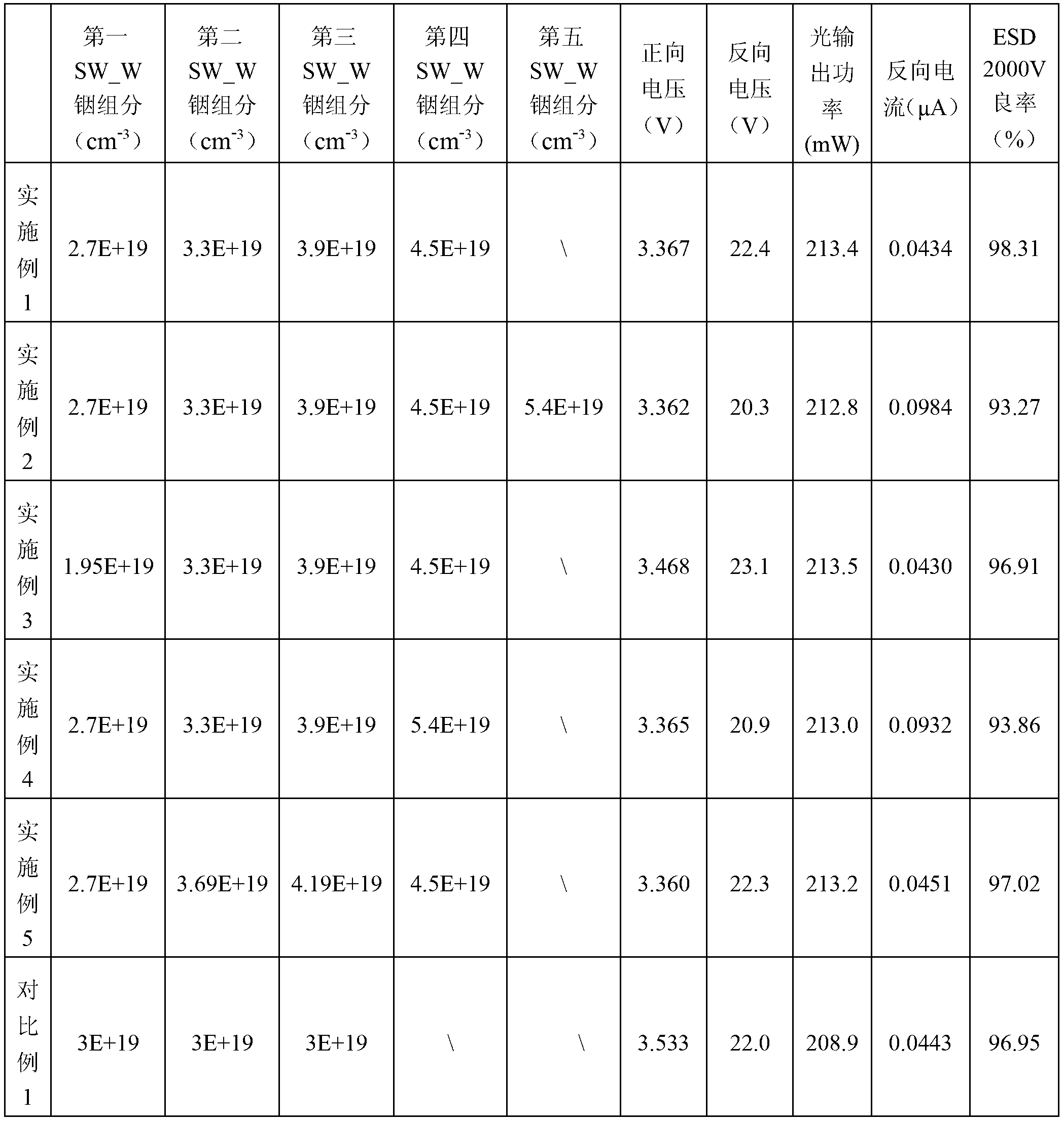

Embodiment 1

[0039] Prepare the C-plane sapphire patterned substrate, place it on the graphite disk of the AIXTRON Crius1 type MOCVD reaction chamber, and perform heat treatment for 8 minutes at the substrate setting temperature of 1280°C in a hydrogen environment, and then lower the substrate setting temperature to Up to 640°C, the growth pressure is controlled at 450 Torr, trimethylgallium with a flow rate of 60 sccm and high-purity ammonia gas with a flow rate of 10,000 sccm are introduced for 2.5 minutes to form a GaN buffer layer with a thickness of about 45 nm; set the temperature to 1230°C , the growth pressure is controlled at 225 Torr, and the trimethylgallium with a flow rate of 200 sccm and the high-purity ammonia gas with a flow rate of 24000 sccm are fed again to form an undoped GaN layer with a thickness of 3000 nm; the growth pressure is controlled at 113 Torr, and the set temperature is raised to 1240°C, add 16 sccm monomethylsilane gas to the above-mentioned trimethylgalliu...

Embodiment 2

[0043] Form the GaN buffer layer, the undoped GaN layer, the doped GaN layer, the N-type AlGaN electron blocking layer, and the GaN barrier layer protection layer sequentially on the C-face sapphire patterned substrate according to the same method as in Example 1; When the set temperature is maintained at 920°C and the growth pressure is controlled at 225Torr, the first InGaN with a thickness of 0.8nm is formed by passing high-purity ammonia gas with a flow rate of 33000sccm, triethylgallium with a flow rate of 40sccm, and trimethylindium with a flow rate of 351sccm. layer, and then fed trimethylgallium with a flow rate of 95 sccm and monomethylsilane gas with a flow rate of 0.68 sccm to form the first GaN layer with a thickness of 40 nm, and trimethyl indium with a flow rate of 429 sccm to form the first GaN layer with a thickness of 0.8 nm. Two InGaN layers, repeating the process of forming the first GaN layer to form a second GaN layer with a thickness of 40nm, feeding trime...

Embodiment 3

[0045] Form the GaN buffer layer, the undoped GaN layer, the doped GaN layer, the N-type AlGaN electron blocking layer, and the GaN barrier layer protection layer sequentially on the C-face sapphire patterned substrate according to the same method as in Example 1; When the set temperature is maintained at 920°C and the growth pressure is controlled at 225Torr, the first InGaN with a thickness of 0.8nm is formed by passing high-purity ammonia gas with a flow rate of 33000 sccm, triethylgallium with a flow rate of 40 sccm and trimethyl indium with a flow rate of 254 sccm layer, and then fed trimethylgallium with a flow rate of 95 sccm and monomethylsilane gas with a flow rate of 0.68 sccm to form the first GaN layer with a thickness of 40 nm, and trimethyl indium with a flow rate of 429 sccm to form the first GaN layer with a thickness of 0.8 nm. Two InGaN layers, repeating the process of forming the first GaN layer to form a second GaN layer with a thickness of 40nm, feeding tri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More