Transistor formation method and CMOS formation method

A technology of transistors and semiconductors, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of small increase in carrier mobility, limited improvement in transistor performance, limited stress, etc., and achieve carrier mobility Increase, increase stress, performance improvement effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

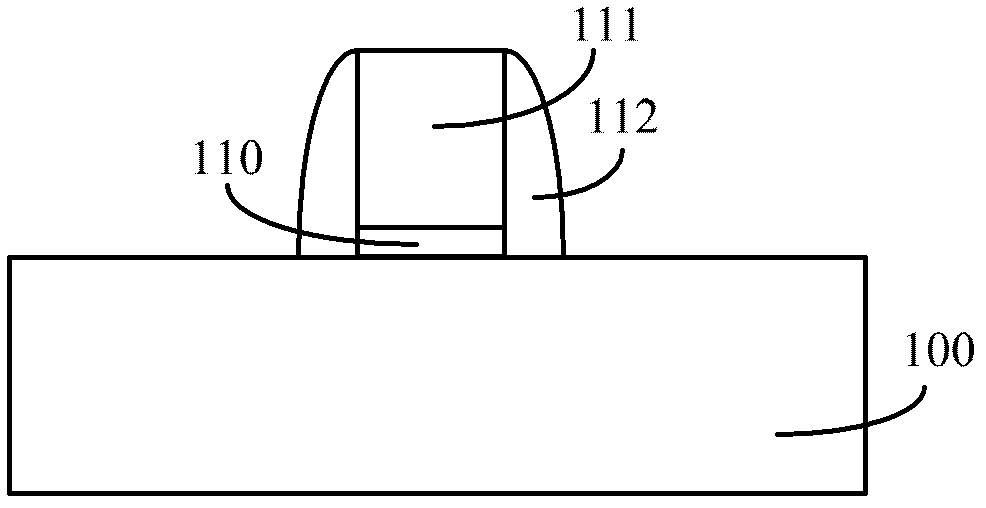

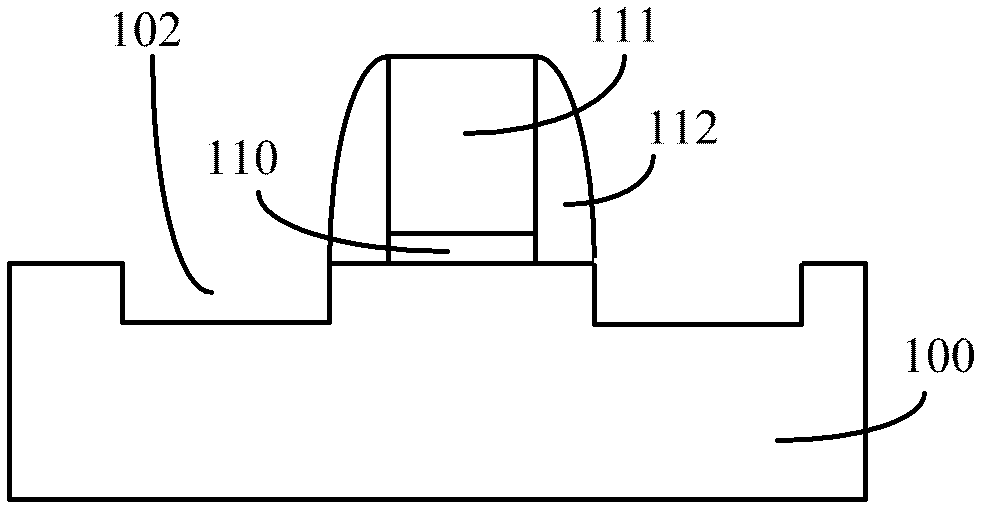

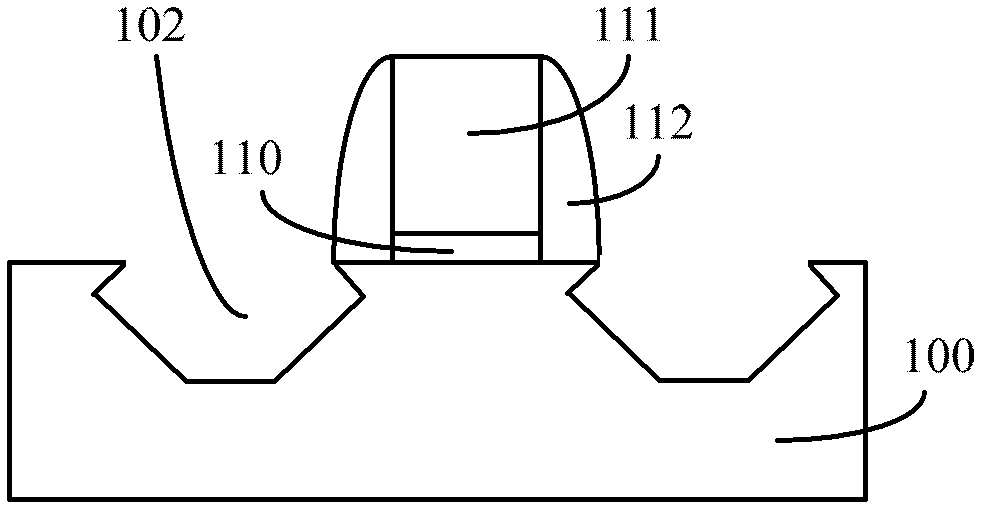

[0070] As mentioned in the background art, the transistor with the stress liner layer formed by the prior art provides limited stress to the channel region, and the improvement of the carrier mobility of the channel region is small, resulting in the formation of the transistor. Performance improvements are limited.

[0071] After research, the inventors found that the reason why the mobility of the transistor with the stress liner layer formed by the prior art is small is that in the existing method of forming the transistor with the stress liner layer, there will be Dry etching and wet etching are carried out in the semiconductor substrates on both sides to form sigma-shaped openings, so that the sidewalls in the gate structure are thinned during the dry etching and wet etching processes; Thin sidewalls easily transfer the stress formed by the stress liner layer to the sidewalls, so the stress obtained in the channel region is reduced, resulting in an insignificant increase i...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More