Processor performance optimization method based on clock planning deviation algorithm

An optimization method and algorithm technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as long time, limited clock deviation planning optimization space, no improvement plan, etc., to achieve the effect of increasing frequency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

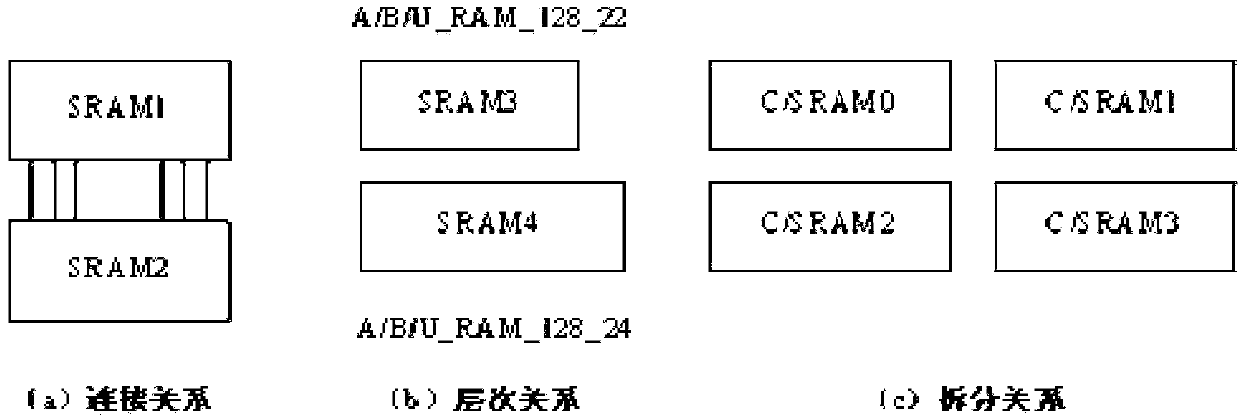

[0030] The present invention implements the effective method based on a multi-SRAM processor platform such as ARM1136JF-S.

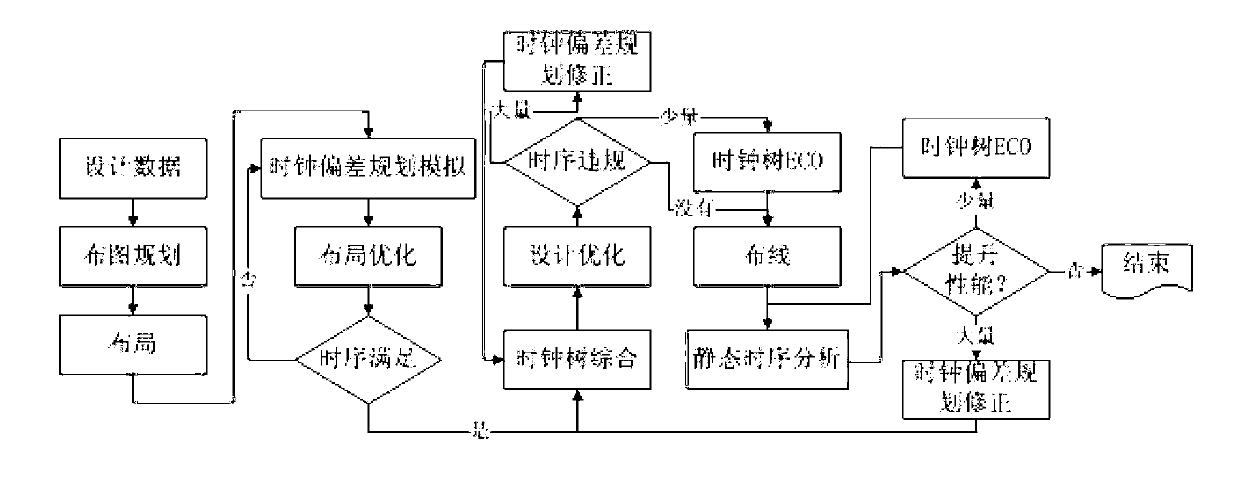

[0031] Such as figure 1 As shown, it is the overall frame diagram of the present invention, the data used for design is laid out, and the associated SRAM will be placed. Then enter the layout stage, and adjust the critical path through clock skew planning. This process requires several iterations to achieve the desired effect. Finally, the wiring forms the final layout and performs static timing analysis to clean up the time violations, and finally obtain accurate and detailed performance improvement parameters.

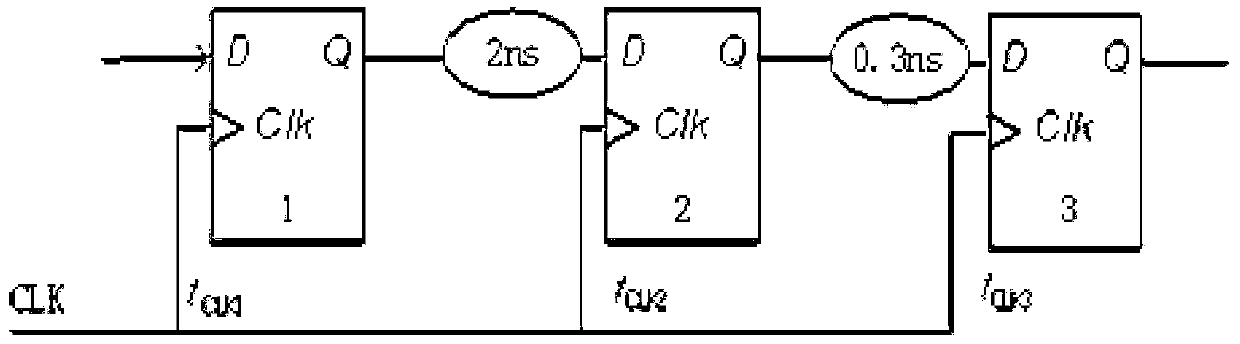

[0032] Such as figure 2 As shown in Table 1, it is a schematic circuit diagram of the clock deviation adjustment and an example table of the clock deviation scheme of the present invention. In the same cloc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More