A multi-ceramic-layer patterned structure substrate for optical and electronic devices

A technology of electronic devices and ceramic layers, applied in the field of electronics, can solve problems such as difficult heat transfer, electrical conduction short circuit, etc., and achieve the effects of solving heat dissipation problems, good electrical isolation and thermal isolation, and high withstand voltage breakdown performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

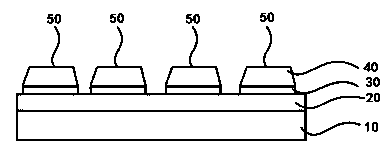

[0022] as attached figure 1 As shown, the multi-ceramic layer patterned structural substrate for optical and electronic devices described in this embodiment includes an aluminum or aluminum alloy substrate 10, and a SiC pressure-resistant ceramic layer 20 and AlN are sequentially formed on the metal substrate. High thermal conductivity ceramic layer 40; there is an aluminum transition layer 30 between the SiC pressure-resistant ceramic layer 20 and the AlN high thermal conductivity ceramic layer 40, and the AlN high thermal conductivity ceramic layer 40 and the aluminum transition layer 30 are selectively selected by a mask Etching forms a plurality of isolation pedestals 50; and forming a metal circuit layer (not shown in the figure) on the uppermost layer of the multi-ceramic layer of the isolation pedestals. The SiC pressure-resistant ceramic layer is prepared by an arc ion plating deposition method, with a thickness of 200 um. Wherein, the step of the aluminum transition ...

Embodiment 2

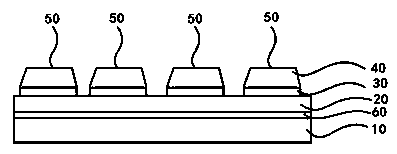

[0024] as attached figure 2 As shown, the multi-ceramic layer patterned structural substrate for optical and electronic devices described in this embodiment includes an aluminum or aluminum alloy substrate 10, and a SiC pressure-resistant ceramic layer 20 and AlN are sequentially formed on the metal substrate. High thermal conductivity ceramic layer 40; there is an aluminum transition layer 30 between the SiC pressure-resistant ceramic layer 20 and the AlN high thermal conductivity ceramic layer 40, and an active braze is arranged between the aluminum alloy substrate 10 and the SiC pressure-resistant ceramic layer 20 Welding layer 60; and selectively etch the AlN high thermal conductivity ceramic layer 40 and the aluminum transition layer 30 through a mask to form a plurality of isolation bases 50; and form on the uppermost layer of the multi-ceramic layer of the isolation base metal circuit layer (not shown in the figure). The SiC pressure-resistant ceramic layer is prepare...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More