Electrostatic discharge resistant LDMOS device

An antistatic and device technology, applied in the electronic field, can solve problems such as damage, uneven opening of parasitic BJTs, current concentration, low ESD performance, etc., achieve process compatibility and improve ESD capabilities

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] In order to make the technical problems, technical solutions and positive effects to be solved by the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings.

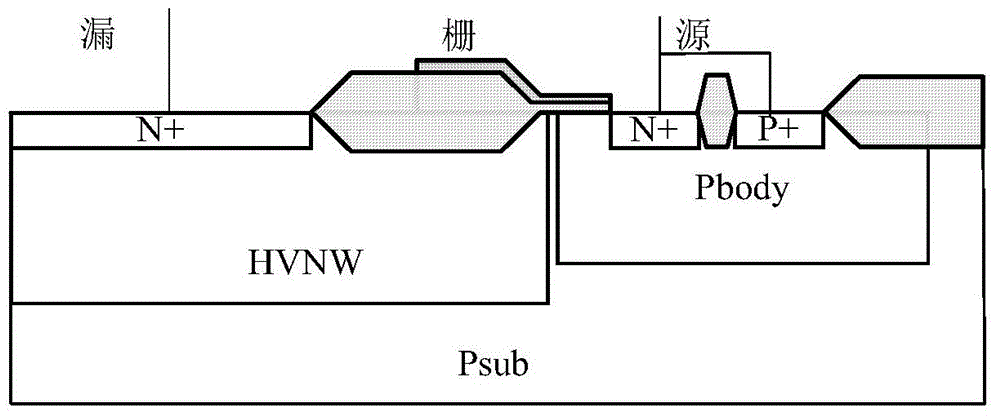

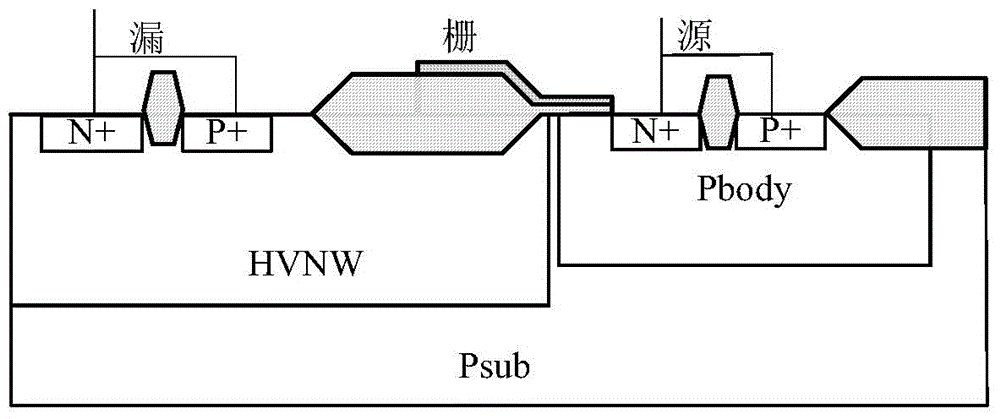

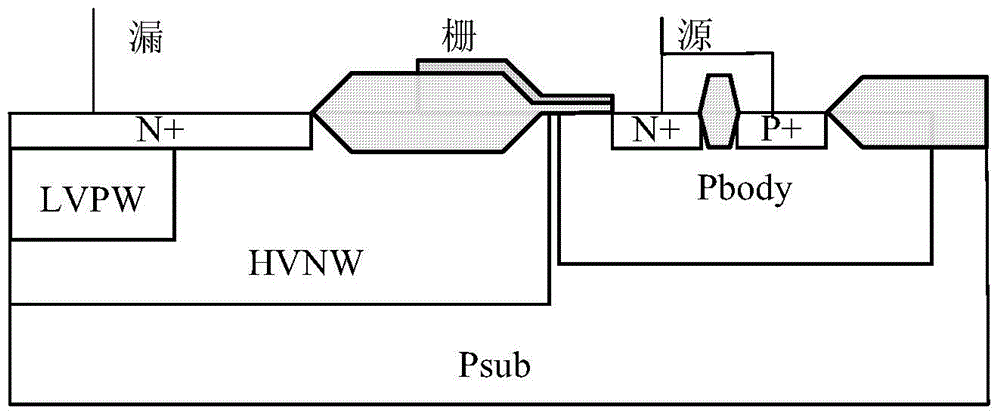

[0020] An anti-static discharge LDMOS device such as image 3 As shown, a conventional LDMOS device is included; the conventional LDMOS device includes a P-type semiconductor substrate, a P-type semiconductor base region and an N-type semiconductor drift region located on the surface of the P-type semiconductor substrate, and the P-type semiconductor base region and N Type semiconductor drift regions are independent of each other and do not contain each other; there are N+ source regions and P+ contact regions that are independent of each other and do not contain each other on the surface of the P-type semiconductor base region, wherein the N+ source region is close to the N-type semiconductor drift region and the P+ contact region ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com